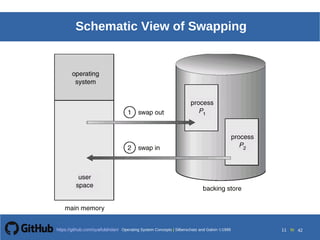

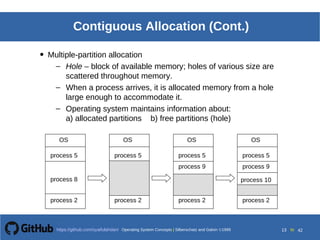

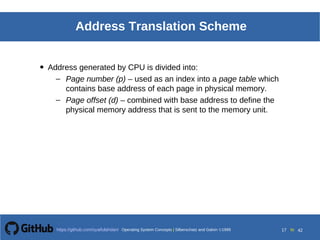

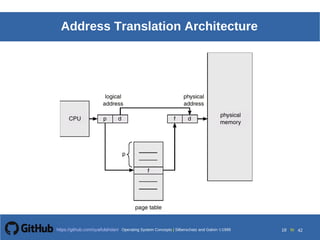

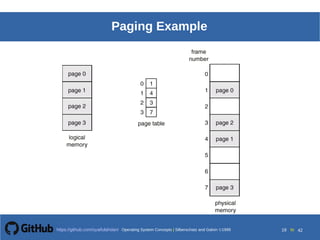

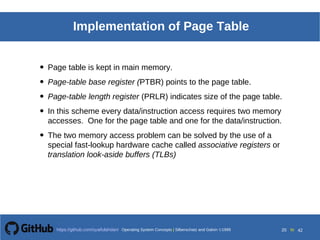

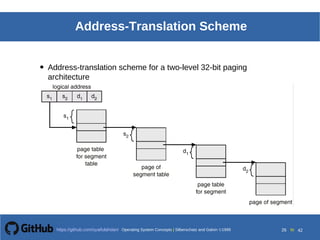

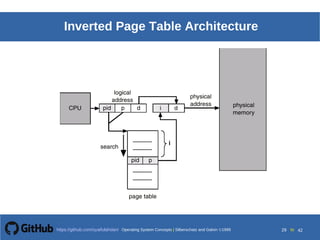

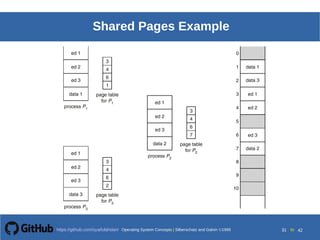

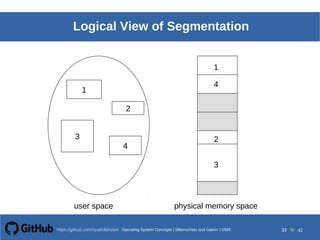

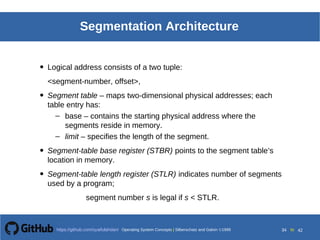

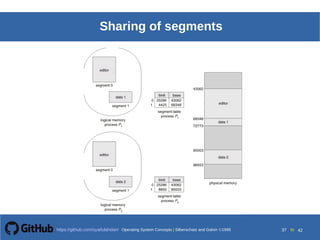

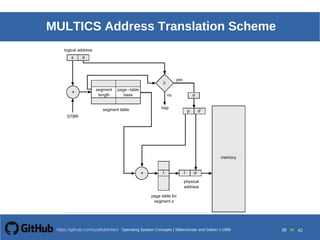

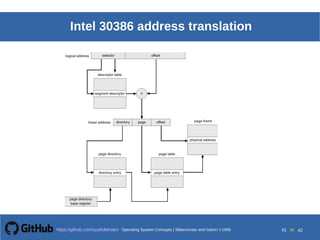

This document discusses memory management techniques in operating systems. It covers logical versus physical address spaces, swapping, contiguous allocation, paging, segmentation, and segmentation with paging. Specific techniques discussed include dynamic loading, dynamic linking, overlays, the role of the memory management unit in address translation, and issues like fragmentation that can occur with contiguous allocation.