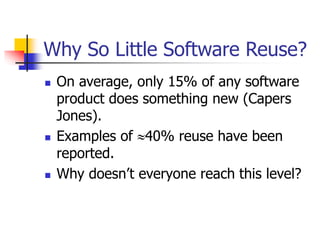

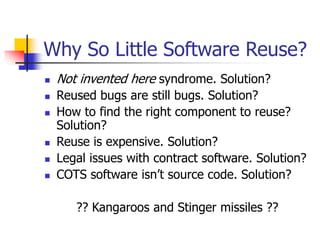

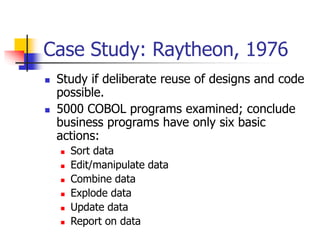

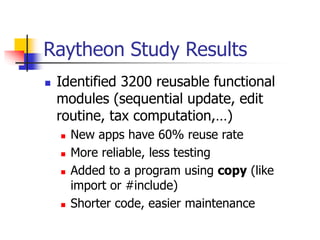

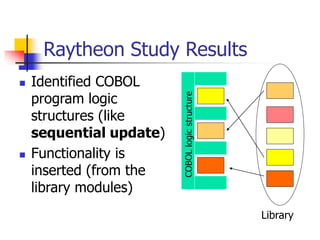

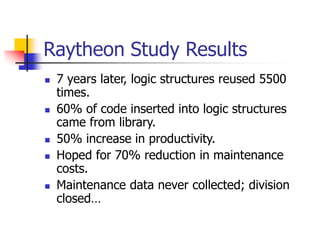

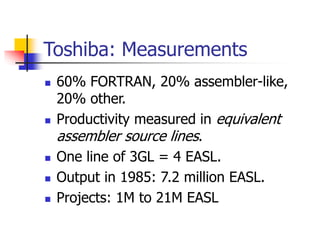

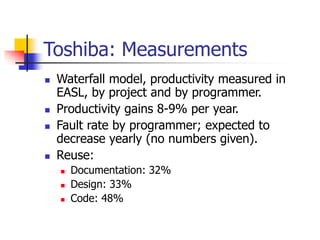

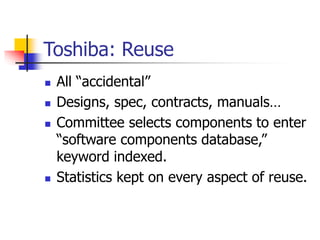

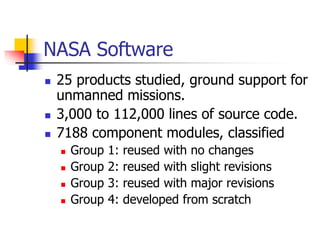

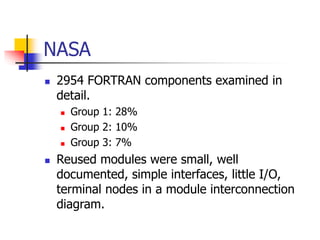

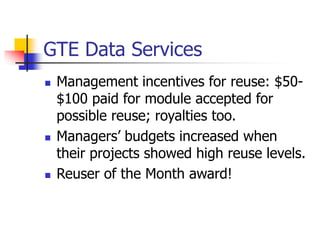

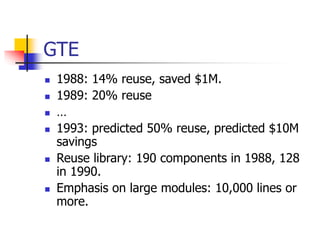

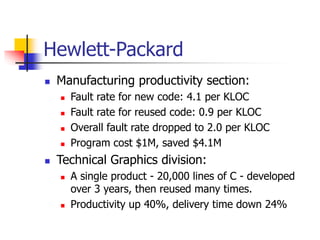

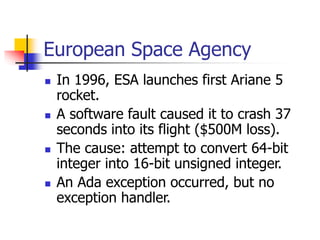

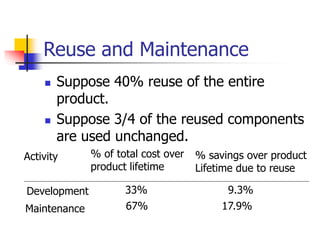

This document discusses reusability, portability, and interoperability in object-oriented analysis and design. It provides examples of deliberate software reuse from companies like Raytheon, Toshiba, NASA, GTE, and Hewlett-Packard that achieved reuse rates from 15-60% and significant cost savings and productivity gains. Barriers to reuse include the "not invented here" attitude and bugs in reused code. The document also discusses achieving portability across platforms and interoperability between programs from different vendors.