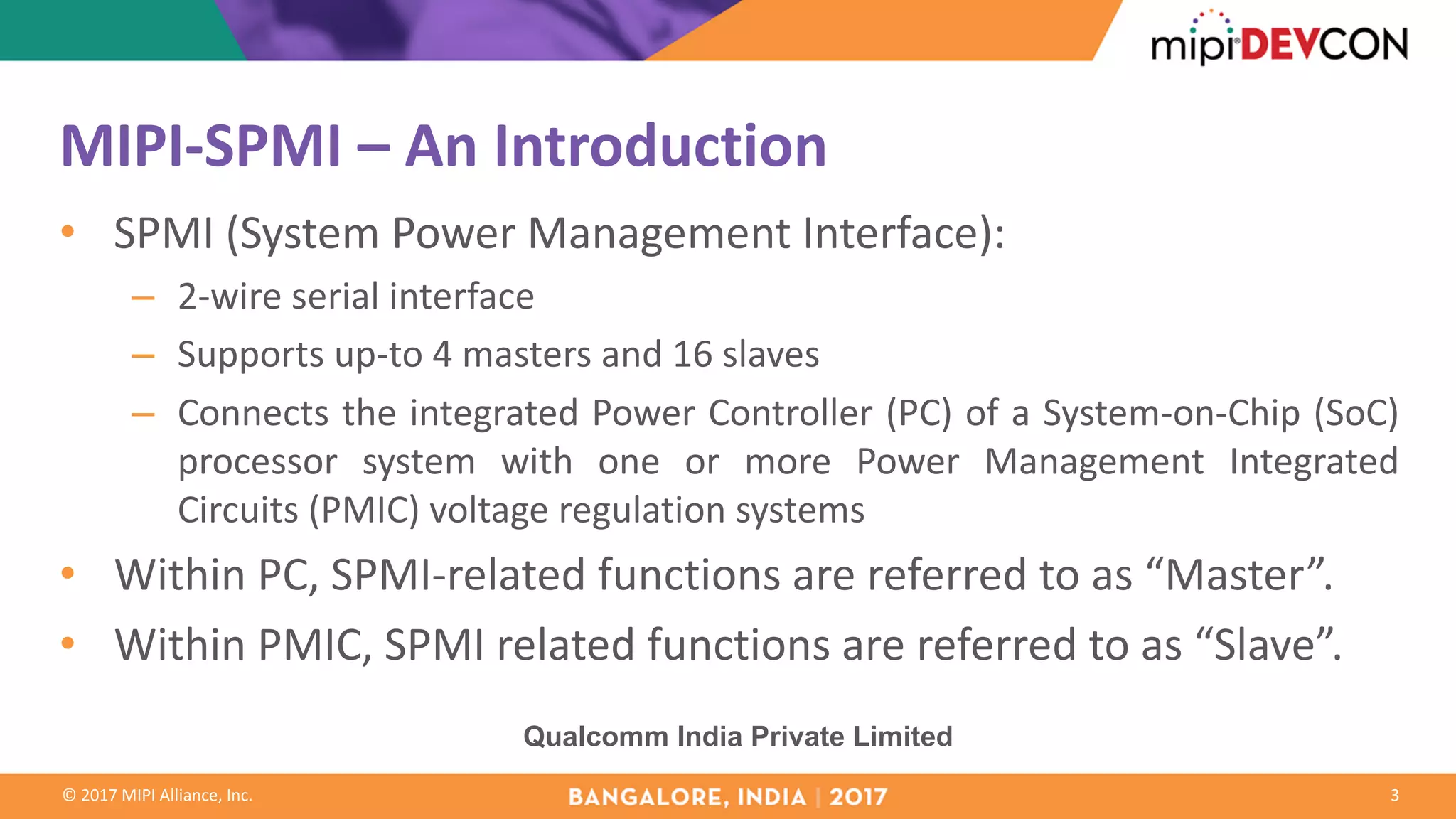

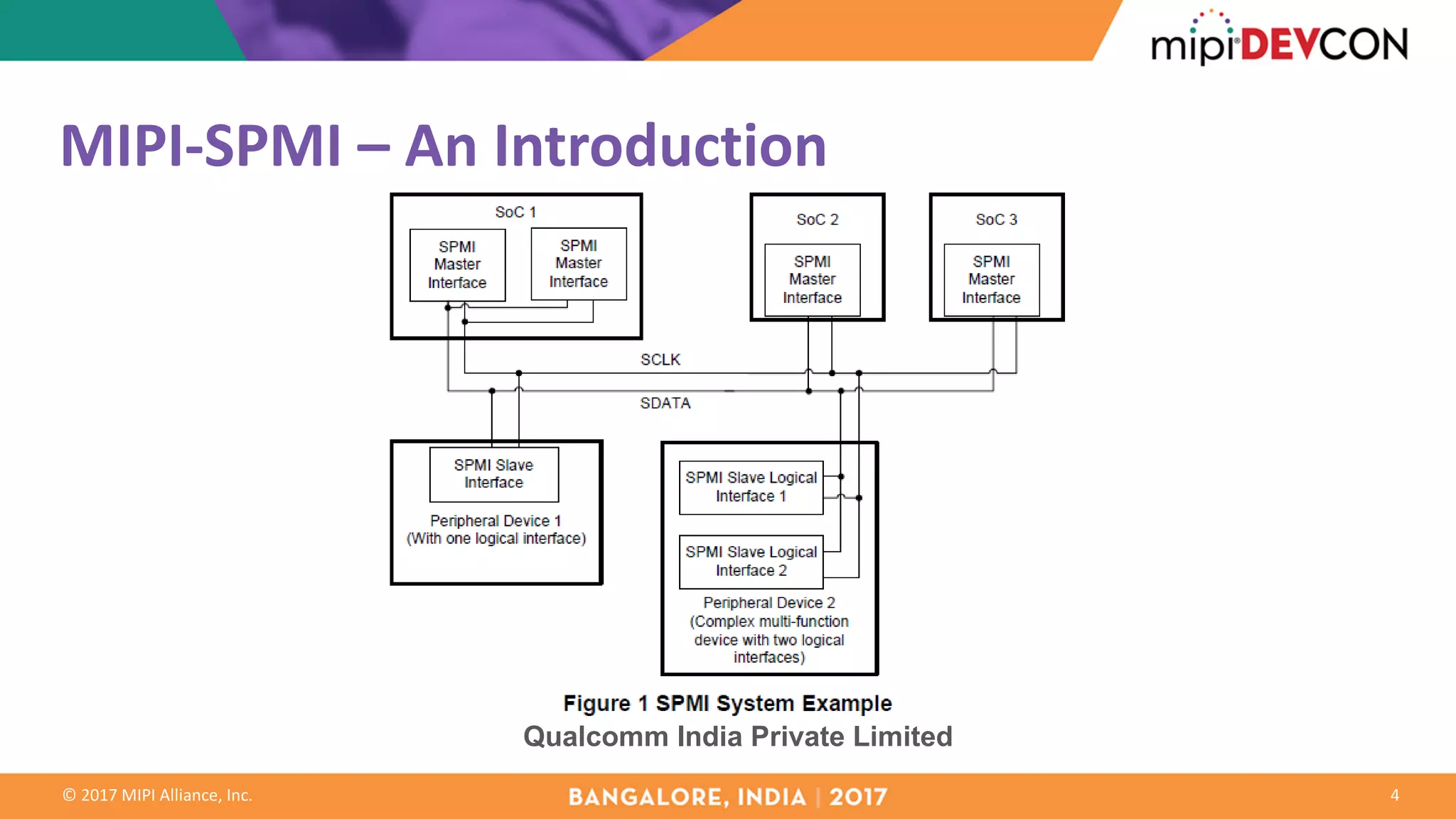

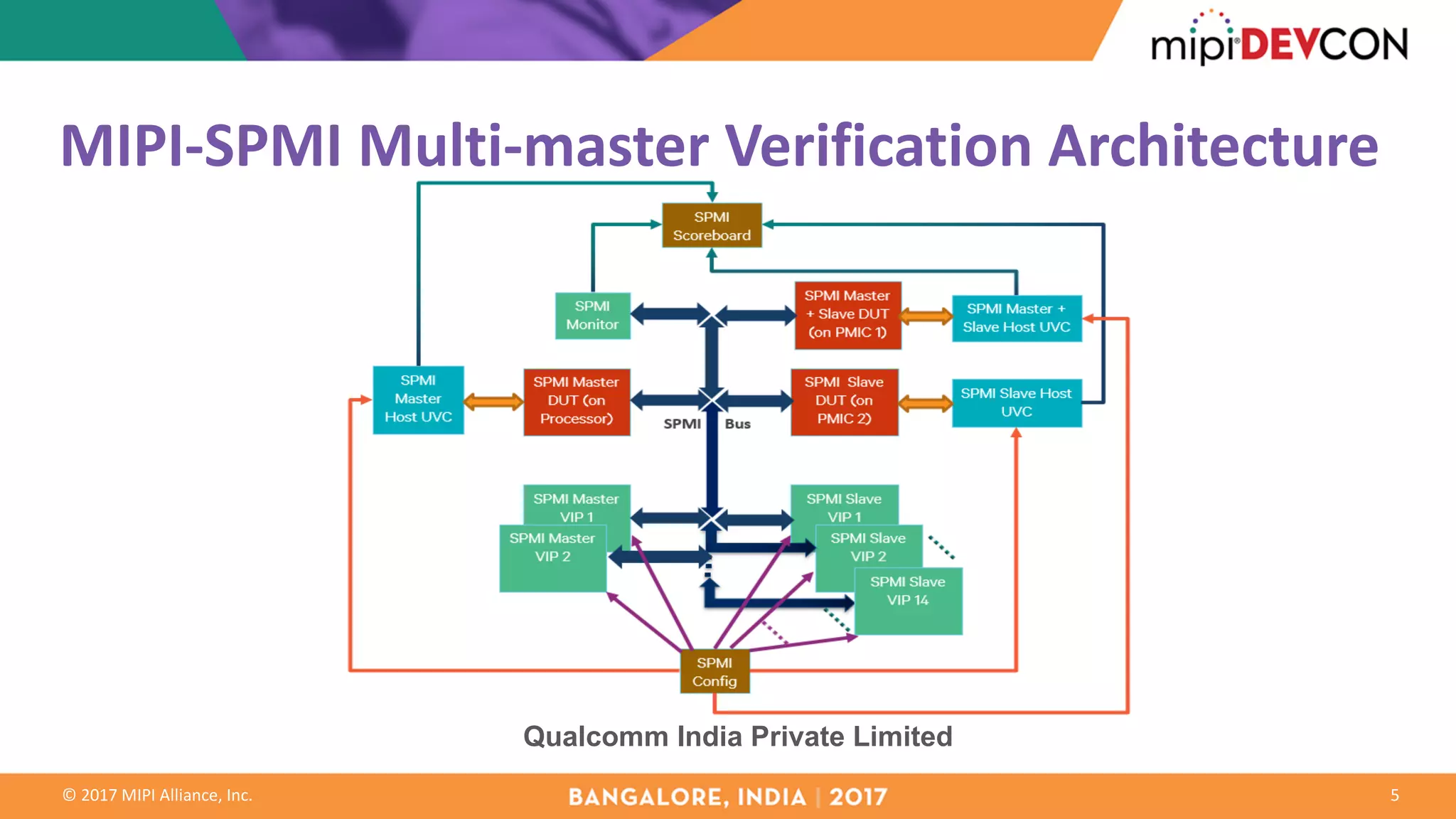

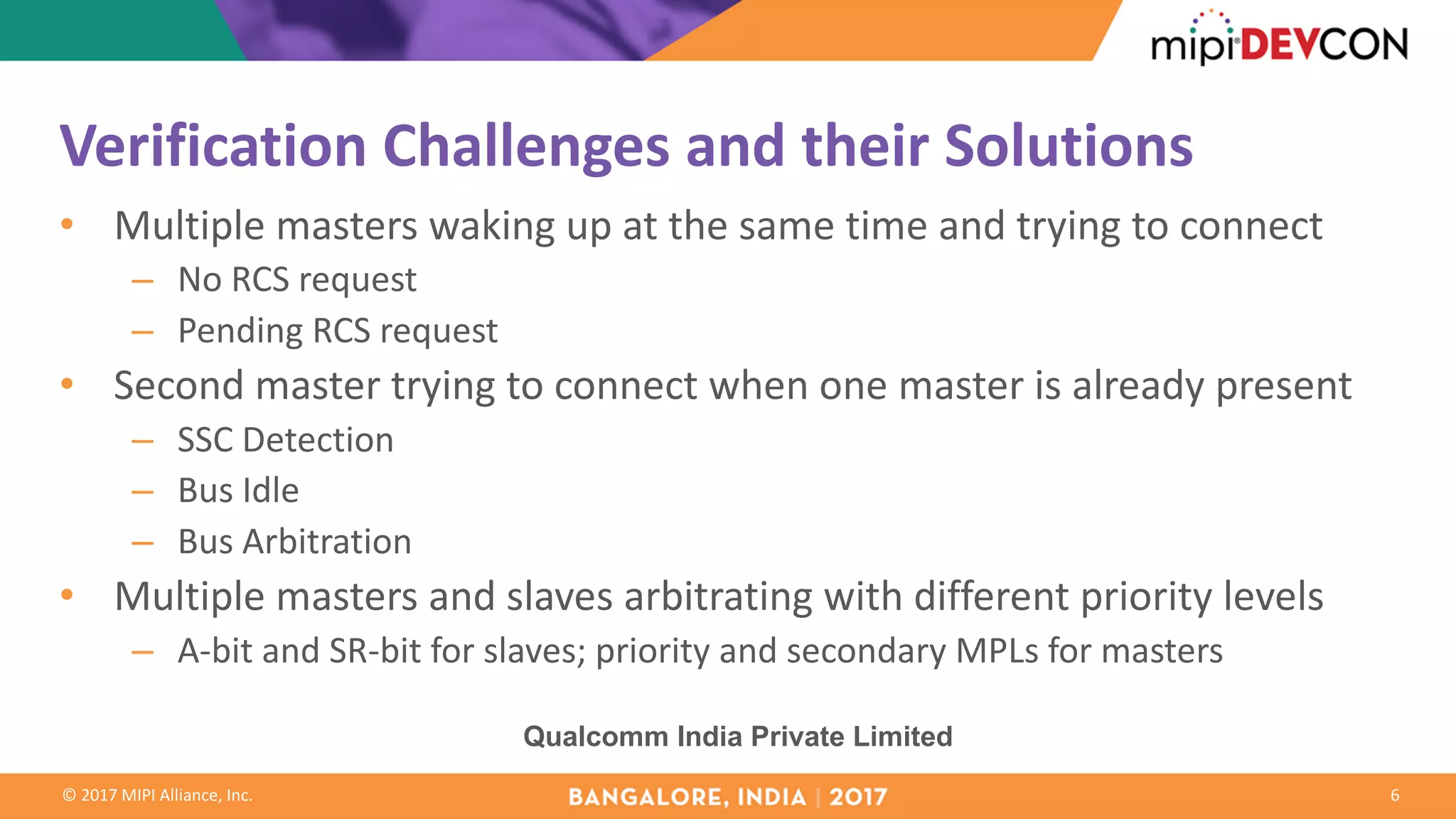

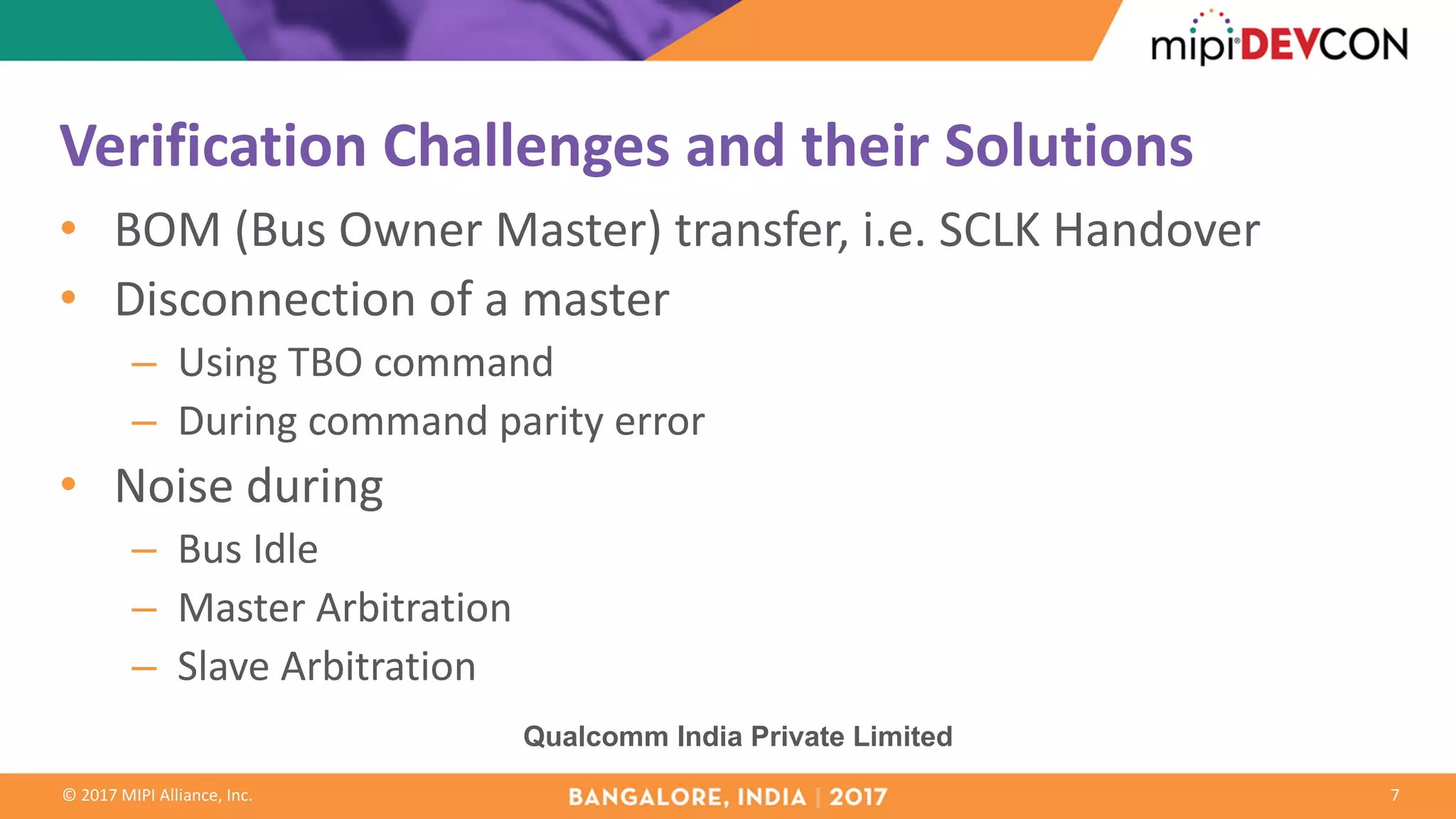

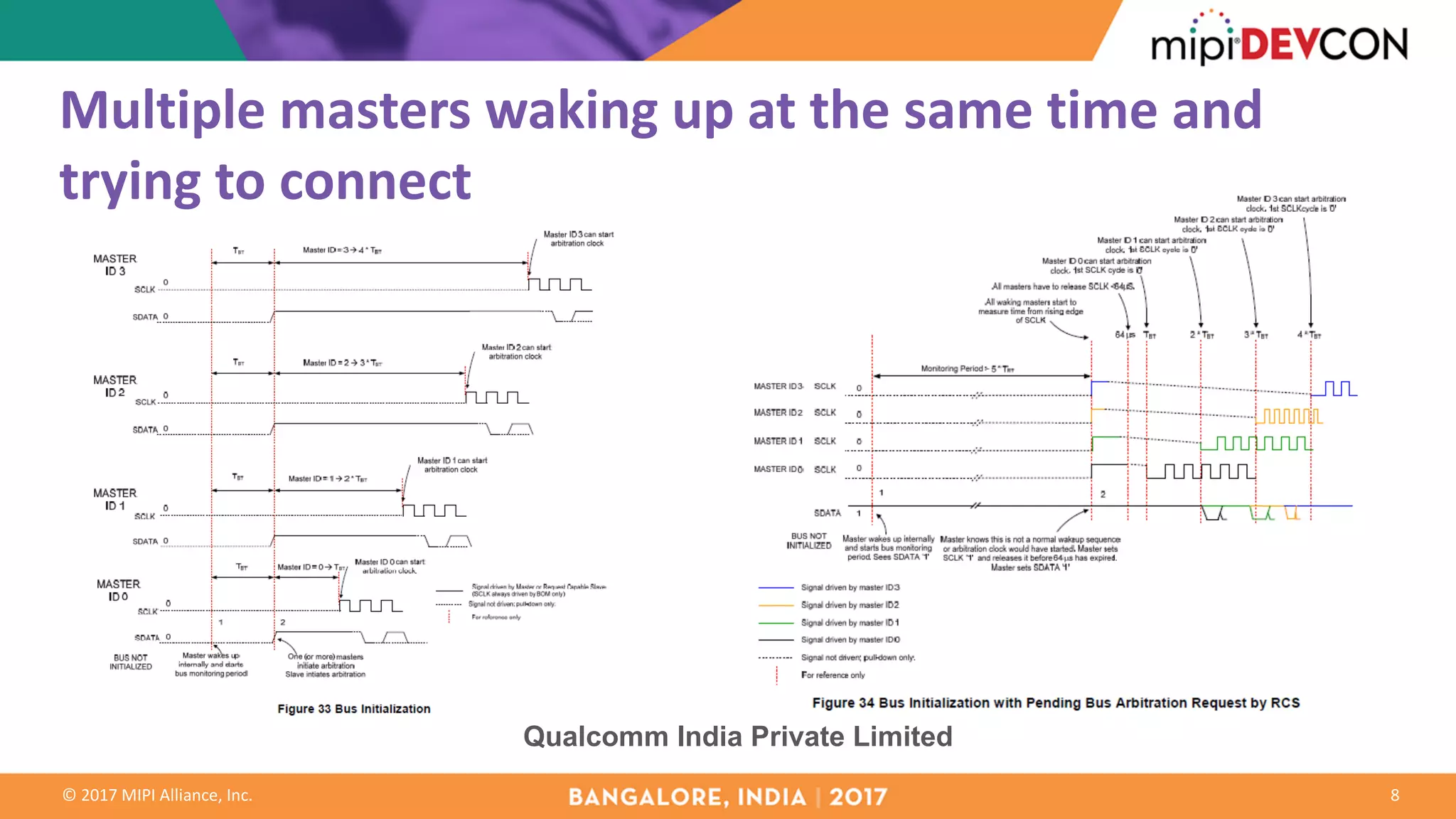

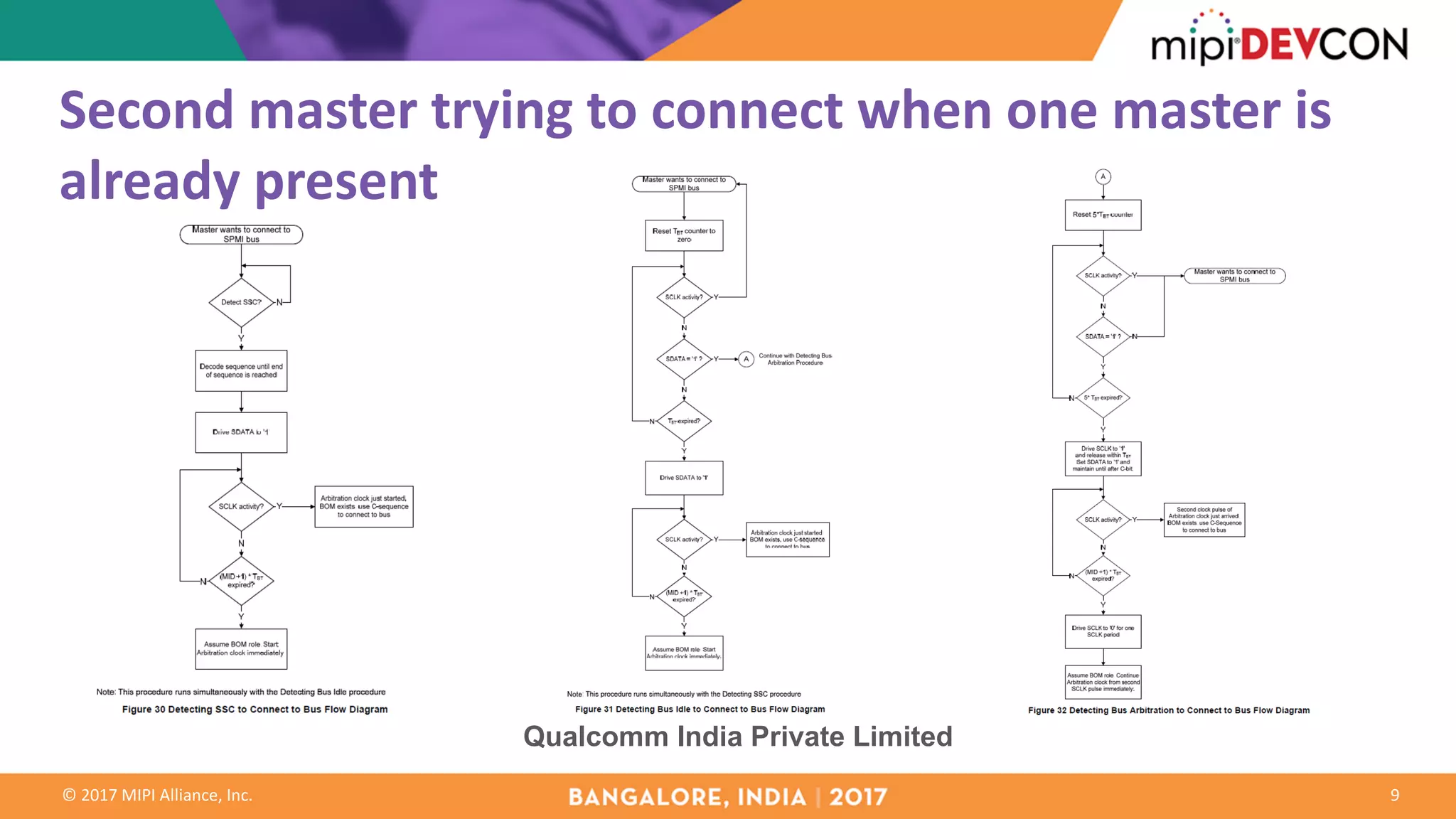

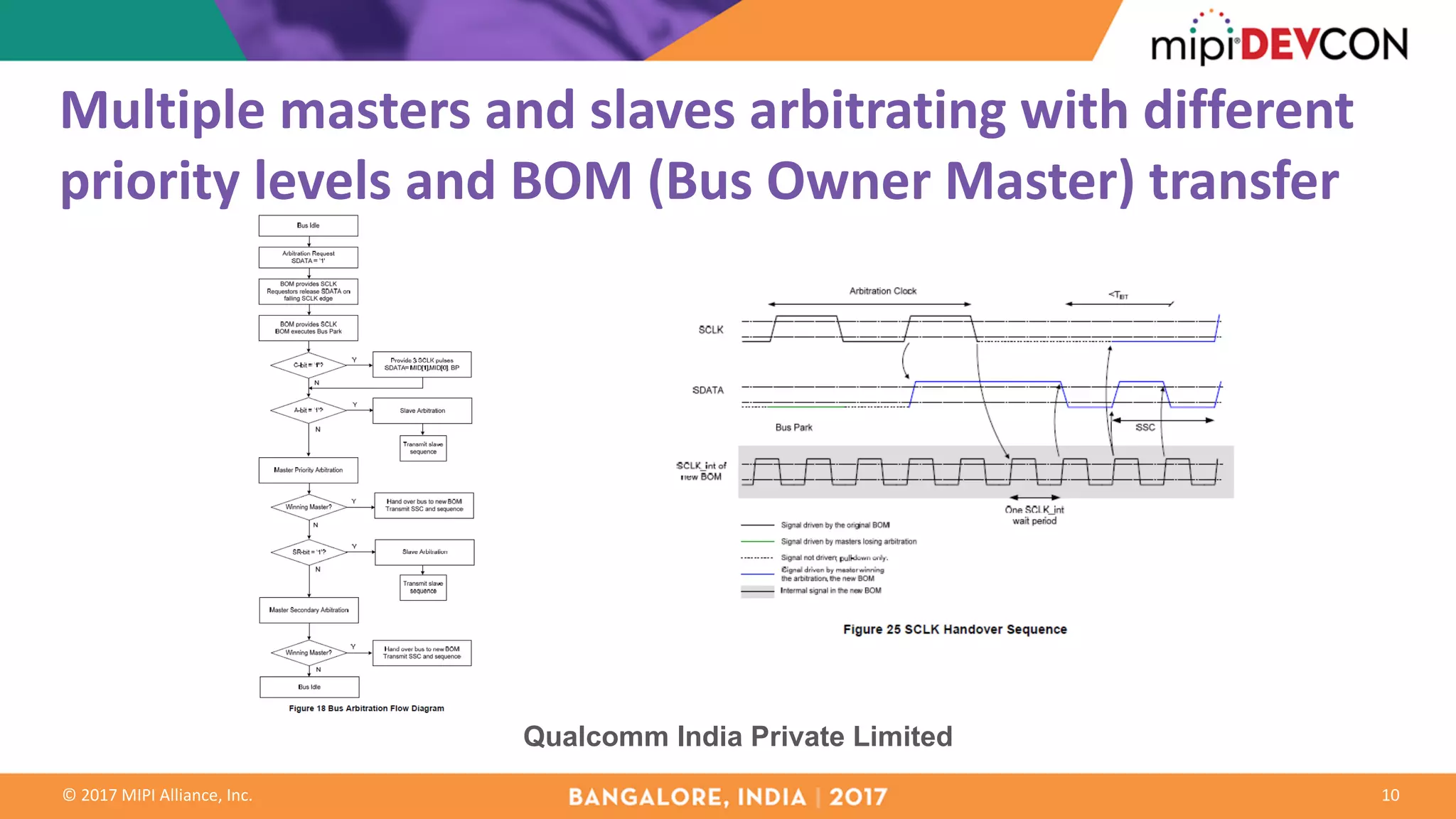

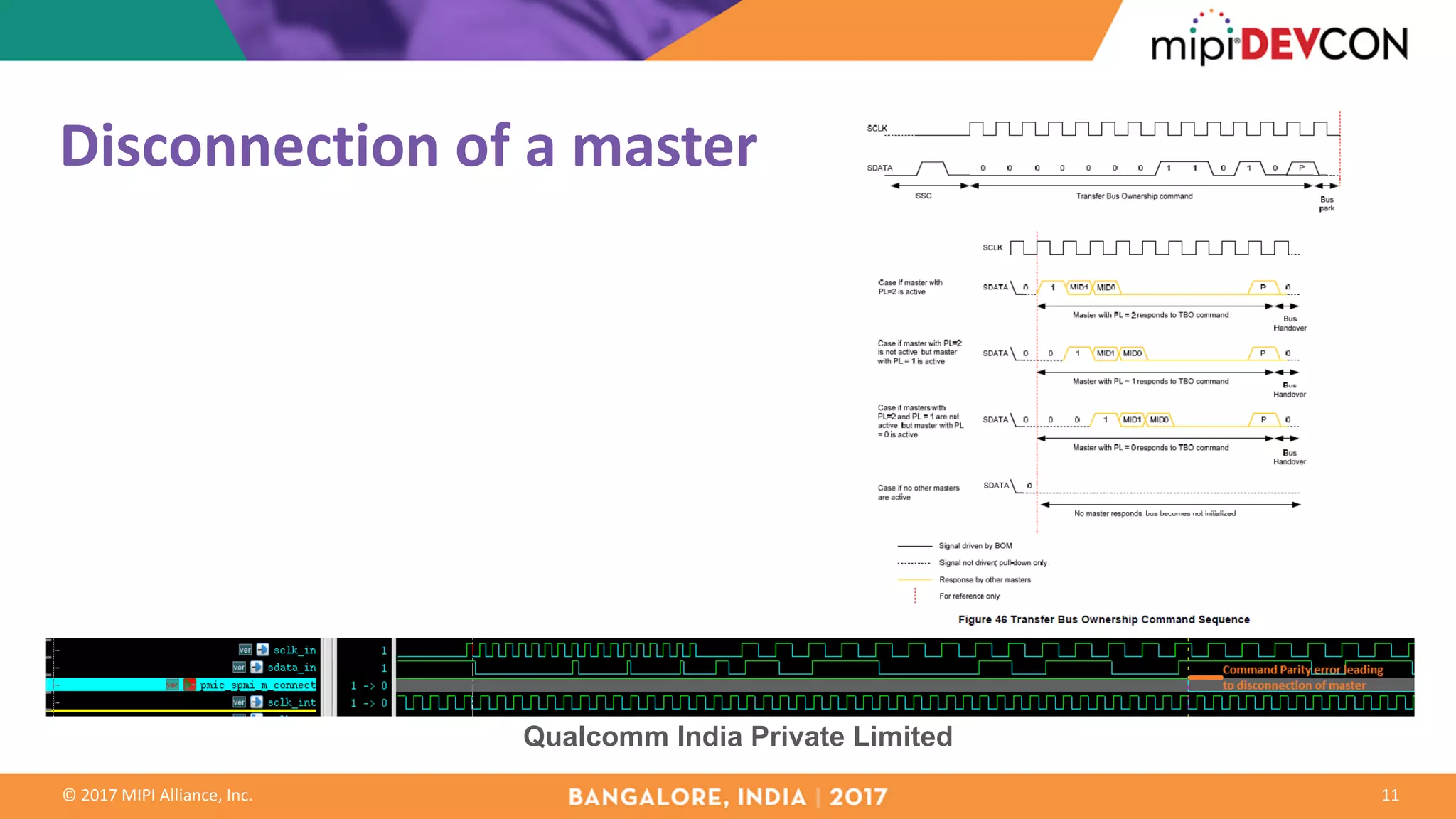

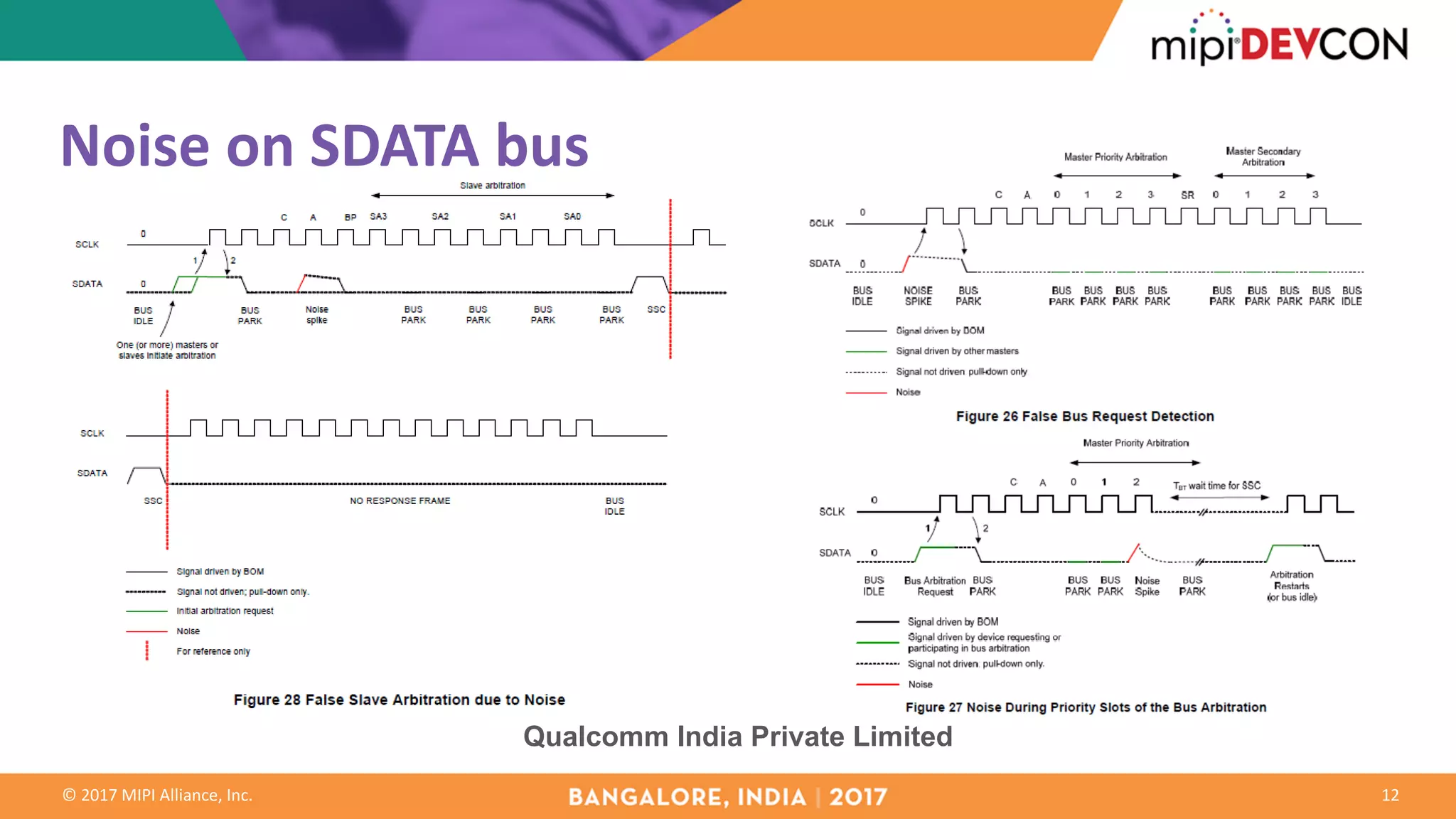

The document discusses the MIPI System Power Management Interface (SPMI) version 1.0, which is a two-wire serial interface enabling connections between multiple masters and slaves in power management systems. It outlines the multi-master verification architecture, verification challenges including bus arbitration and noise issues, and presents solutions for them. The conclusion highlights the protocol's importance in reducing chipset connections, notes areas for improvement, and references the MIPI specification for further details.