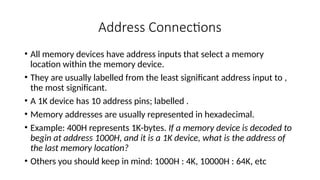

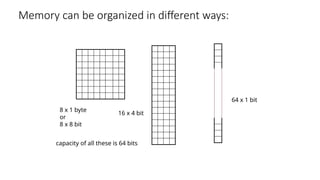

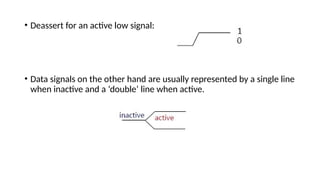

The document outlines the fundamentals of memory interfacing, including data storage, address generation, and memory organization. It discusses the importance of address and data connections, control inputs, and the significance of timing diagrams in communication protocols. Practical applications are noted, along with a brief assignment to explore various types of memory systems in industry.