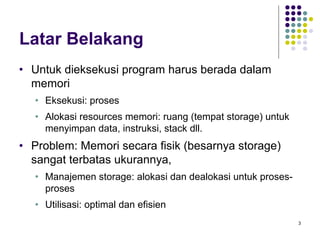

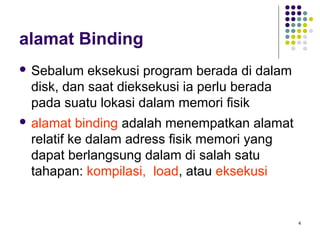

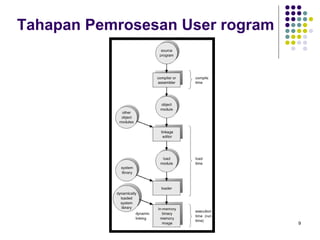

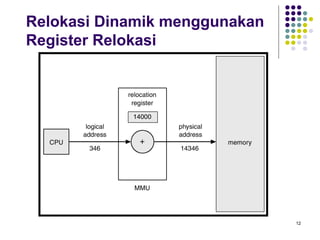

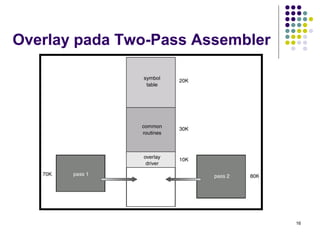

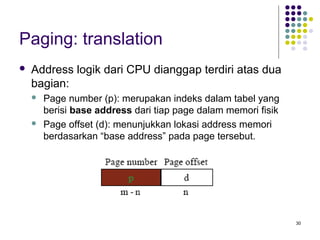

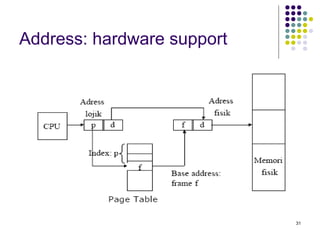

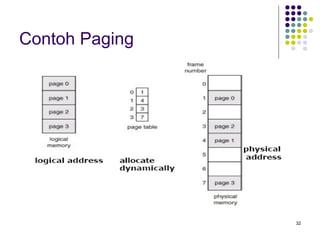

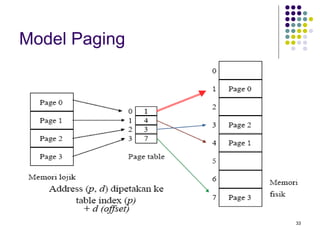

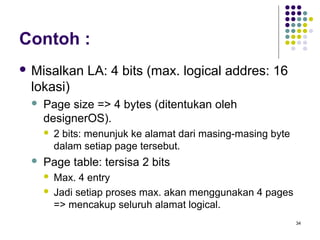

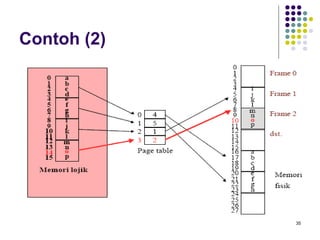

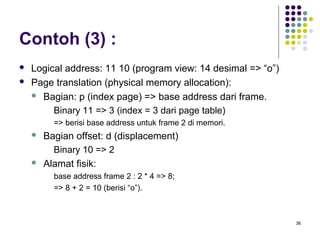

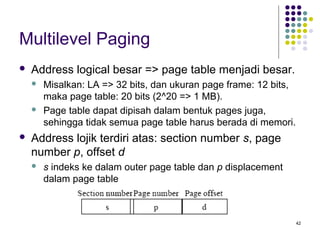

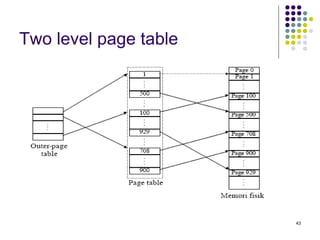

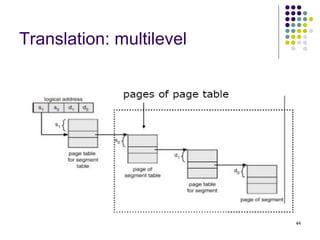

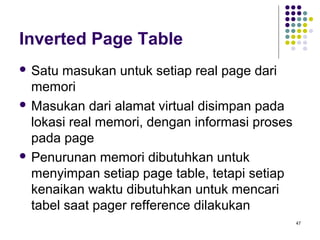

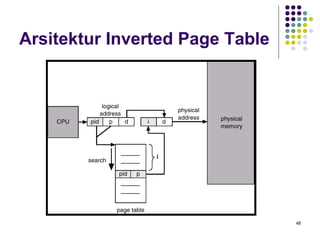

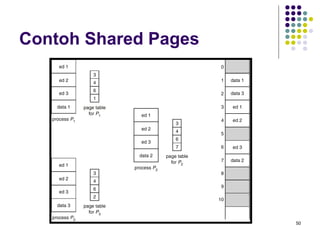

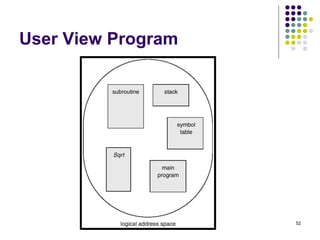

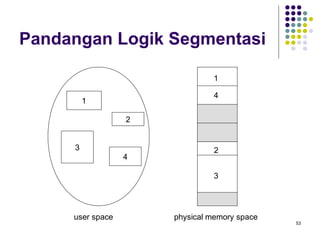

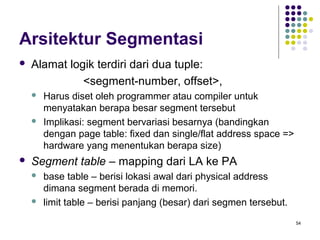

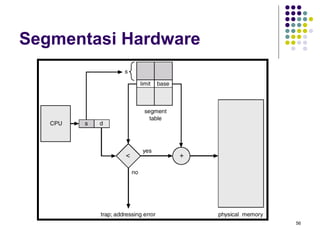

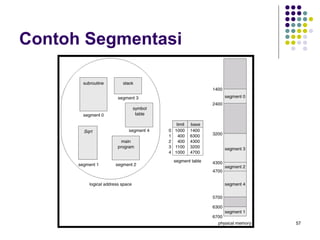

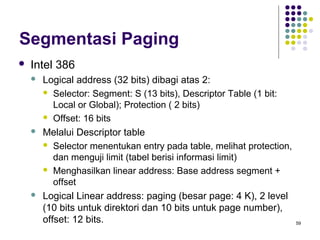

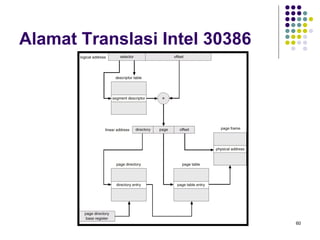

Dokumen ini membahas manajemen memori dalam sistem operasi, mencakup teknik seperti swapping, alokasi kontigu, paging, dan segmentasi. Memori dieksplorasi dari segi alokasi fisik dan logis, serta mekanisme yang berhubungan dengan binding alamat dan pengelolaan page table. Berbagai metode seperti dynamic loading, dynamic linking, dan overlay juga dijelaskan untuk meningkatkan efisiensi dan manajemen ruang memori.