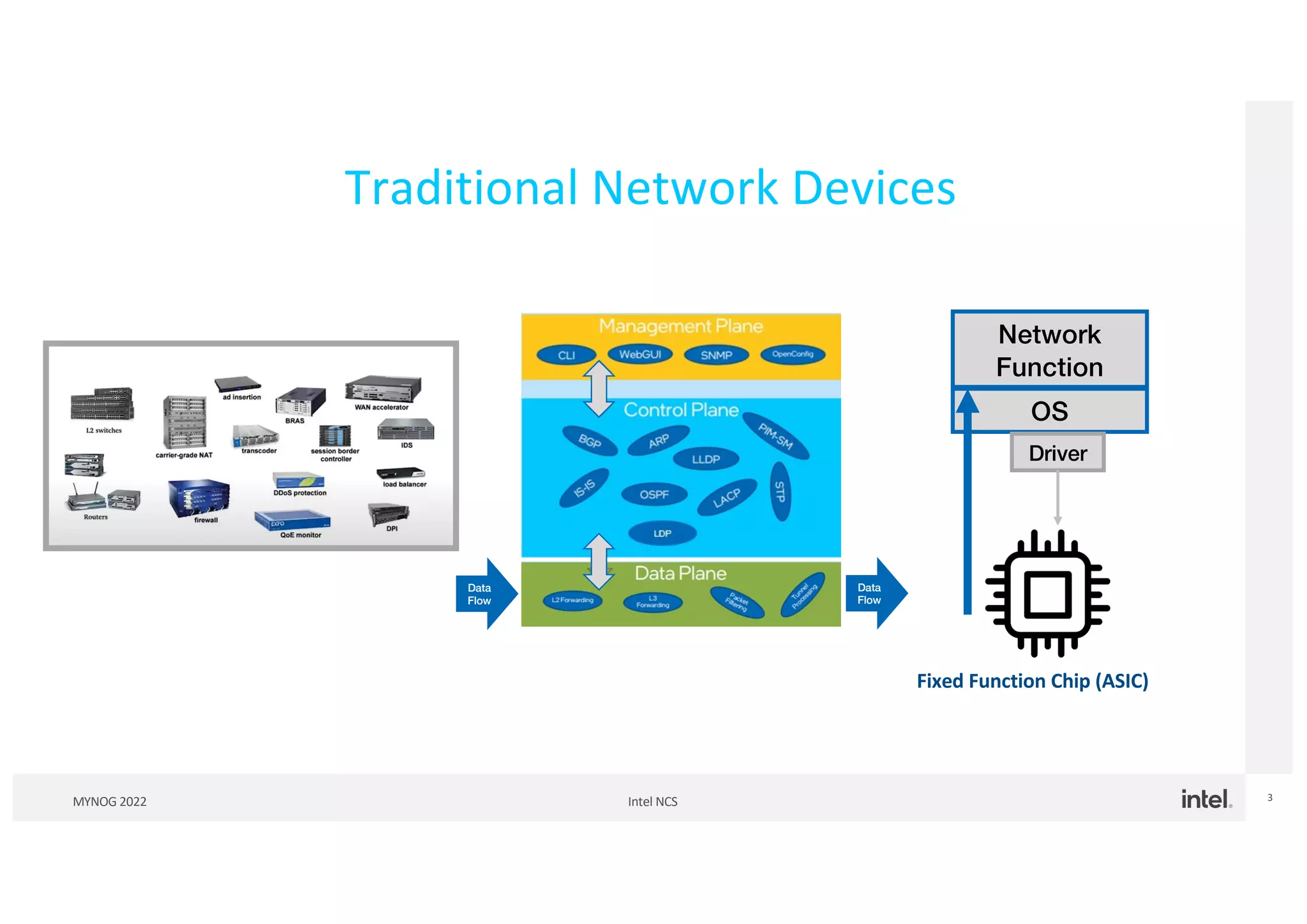

This document discusses programmable networks and introduces key concepts:

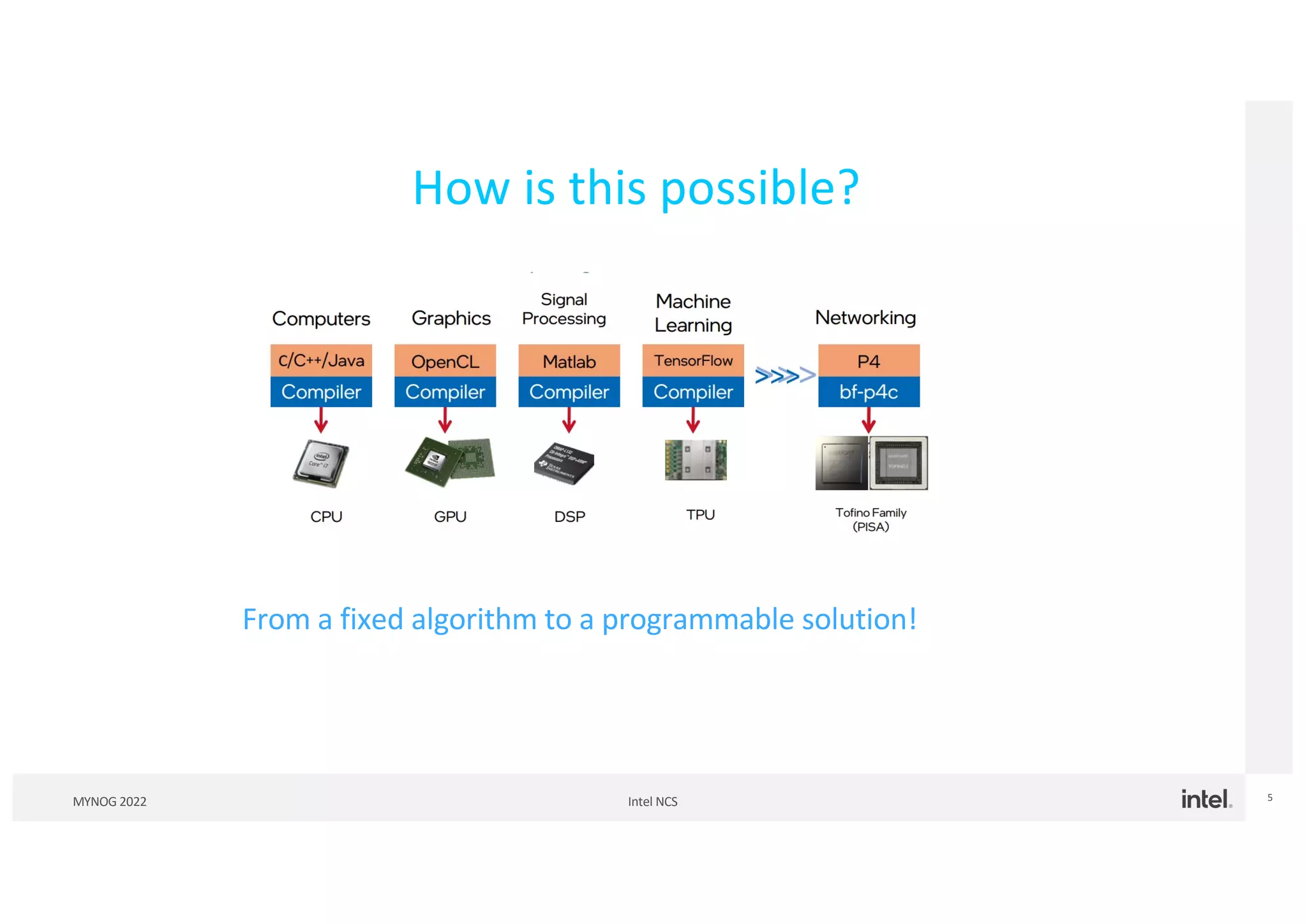

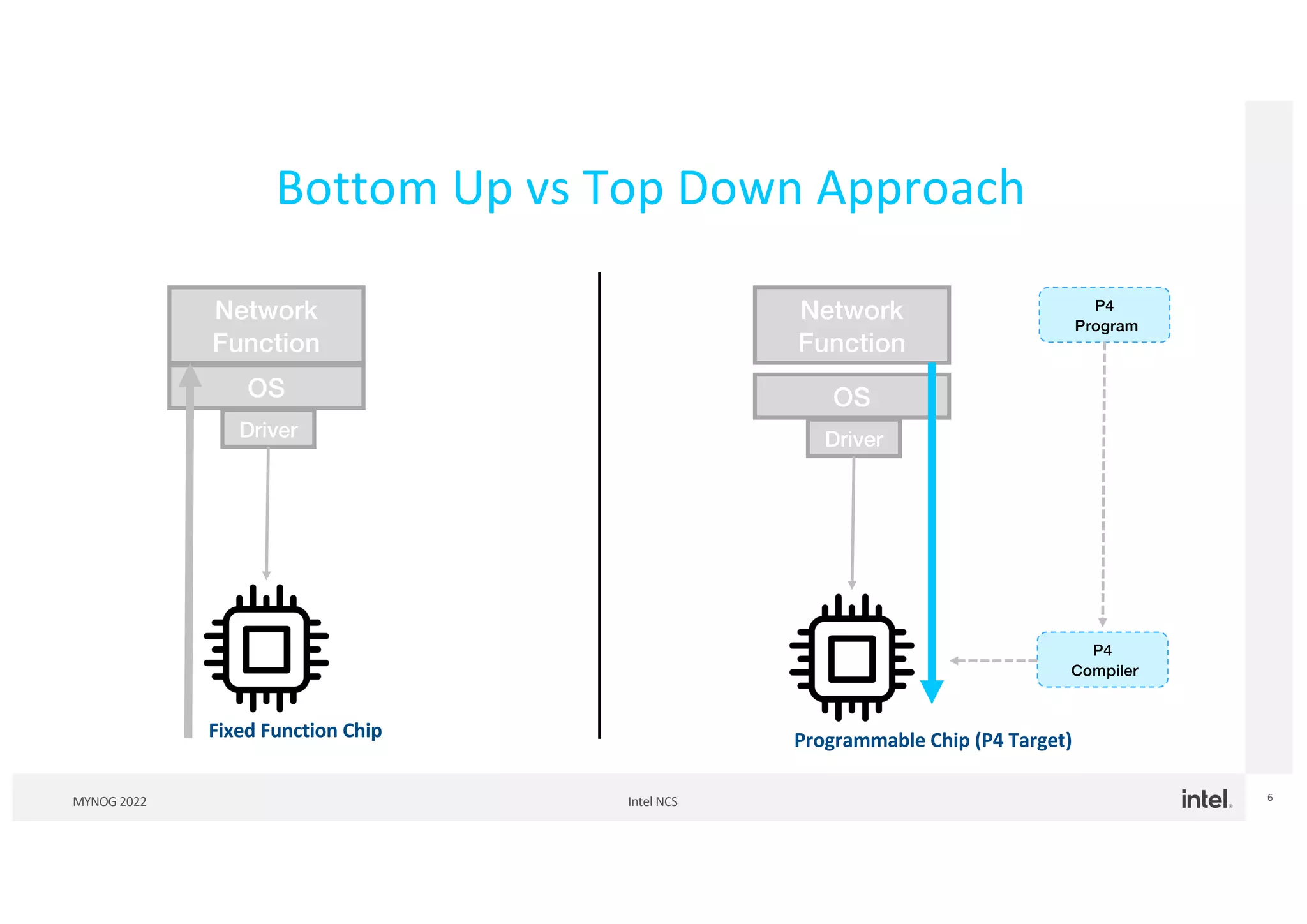

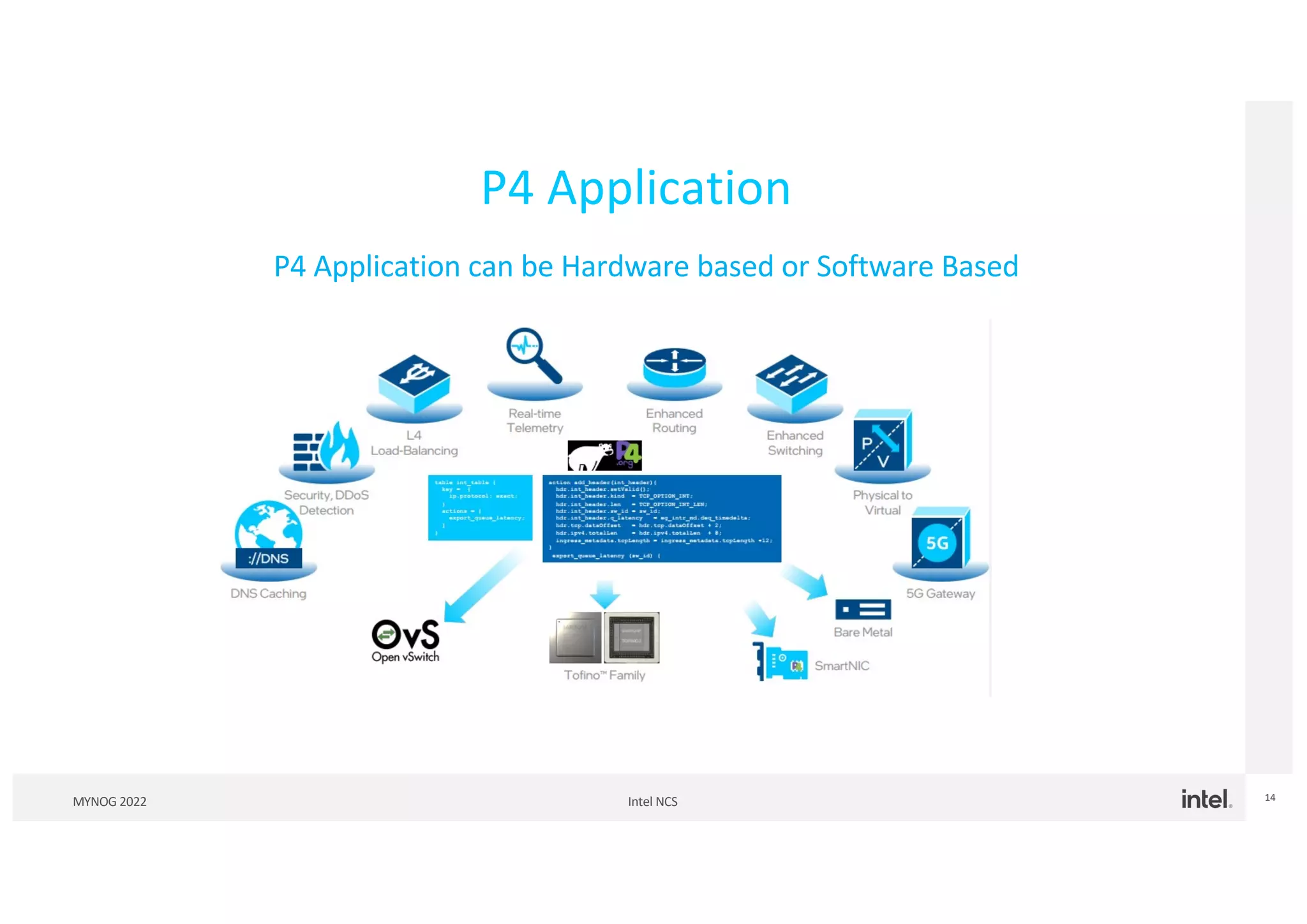

- Programmable networks allow for innovation by enabling the writing of packet processing algorithms rather than relying on fixed-function hardware. This is done through programmable switches and protocol-independent packet processors.

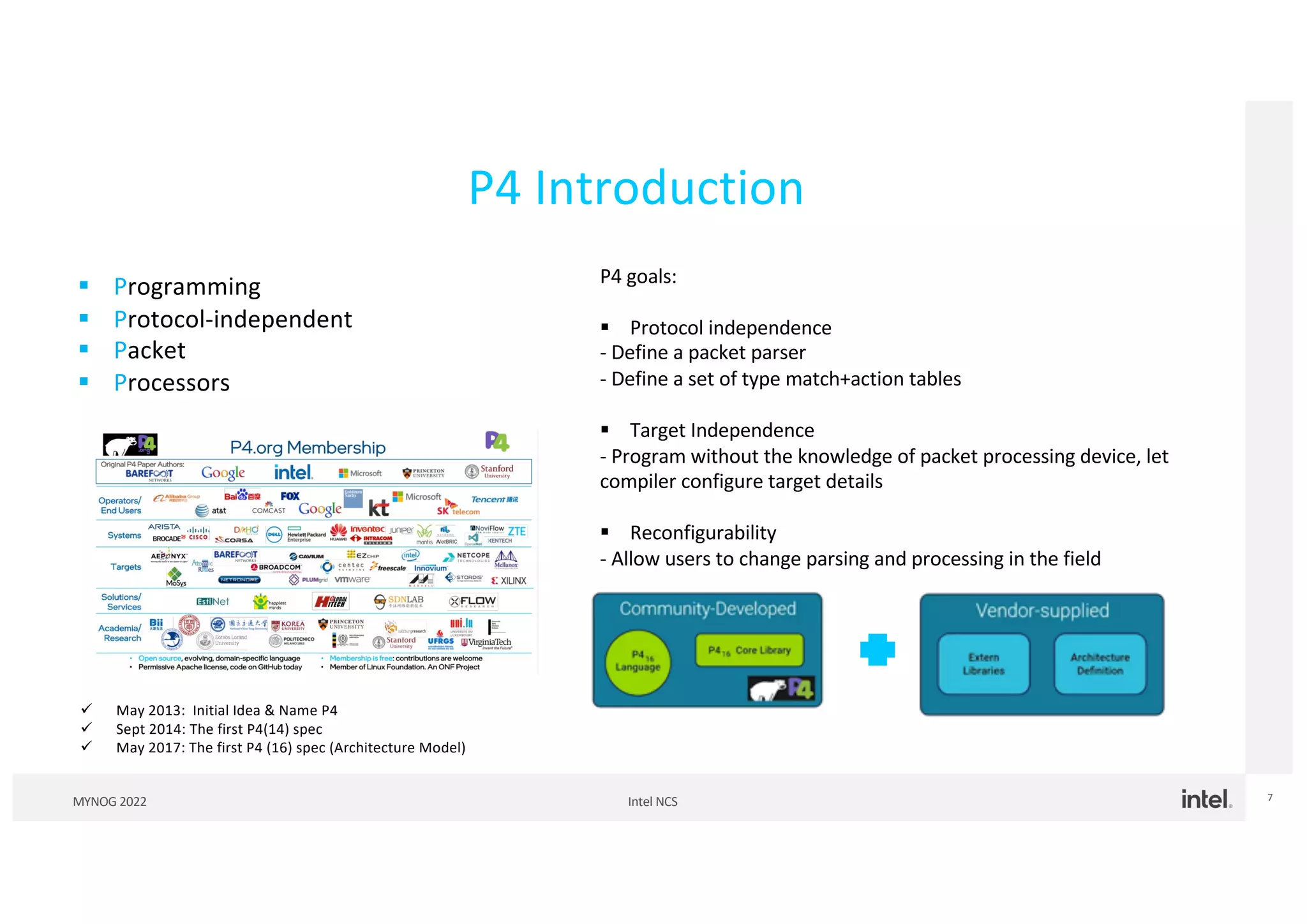

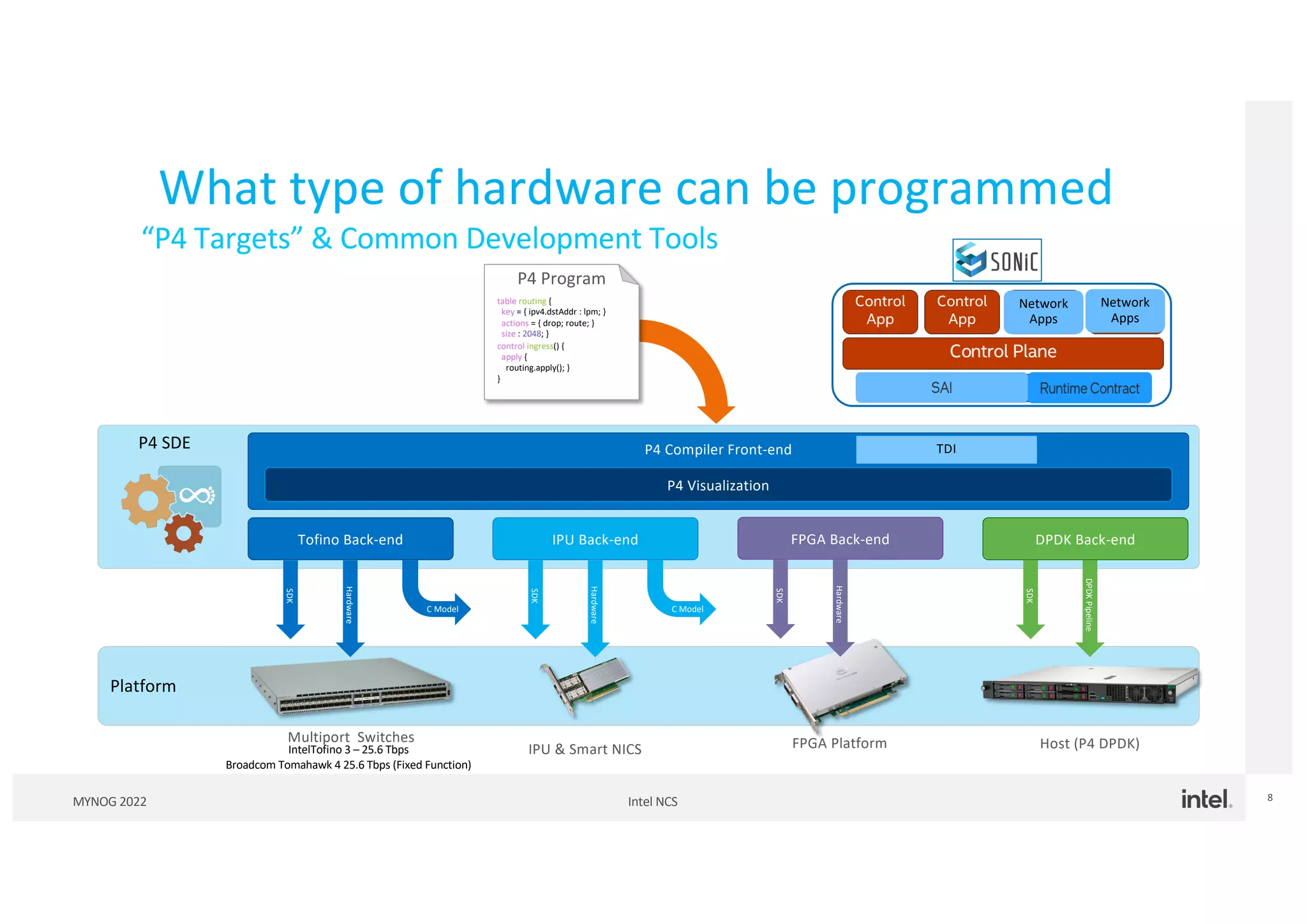

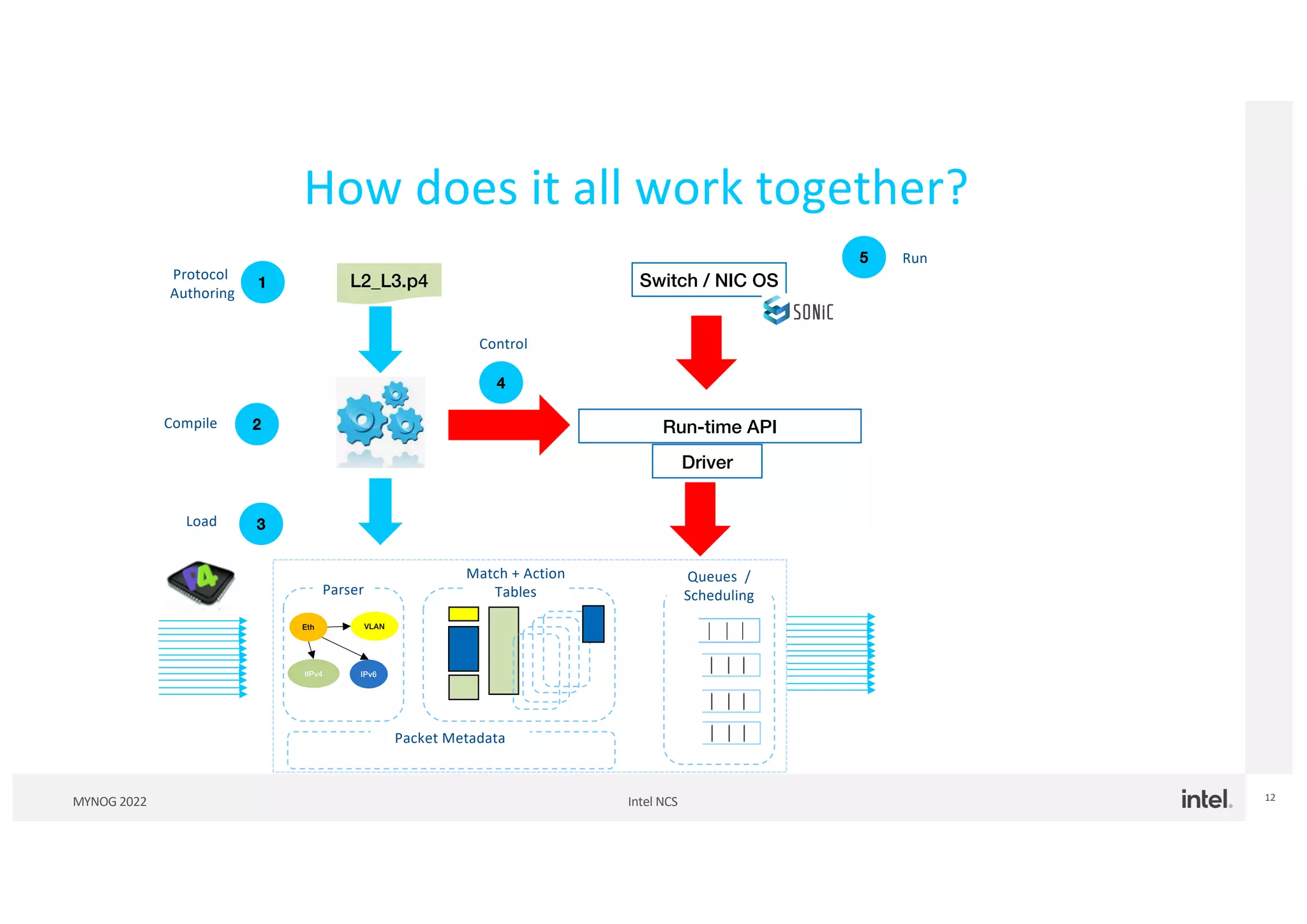

- P4 is a language that allows defining packet parsing, headers, tables, and processing logic in a target-independent way. It enables protocol and target independence.

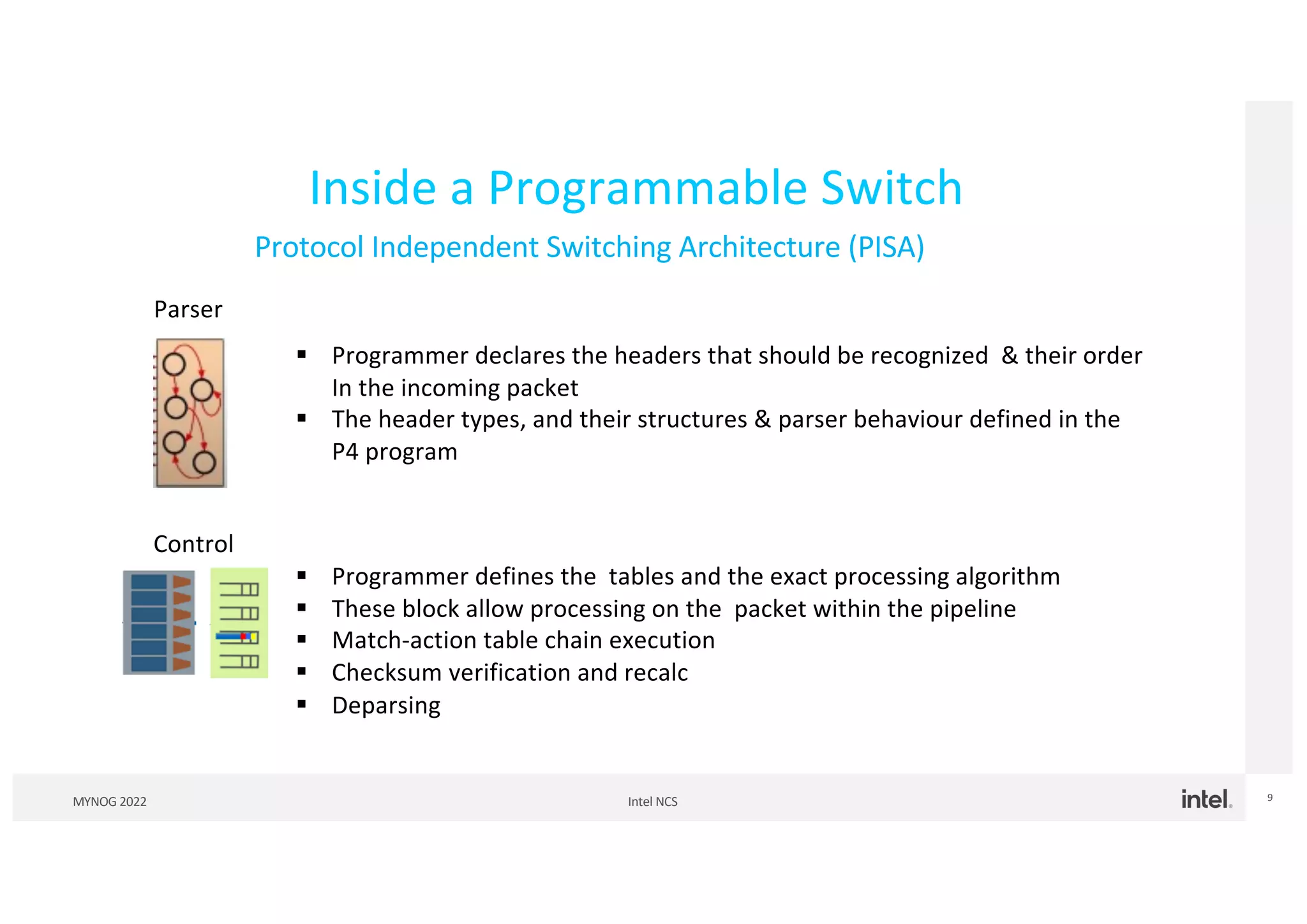

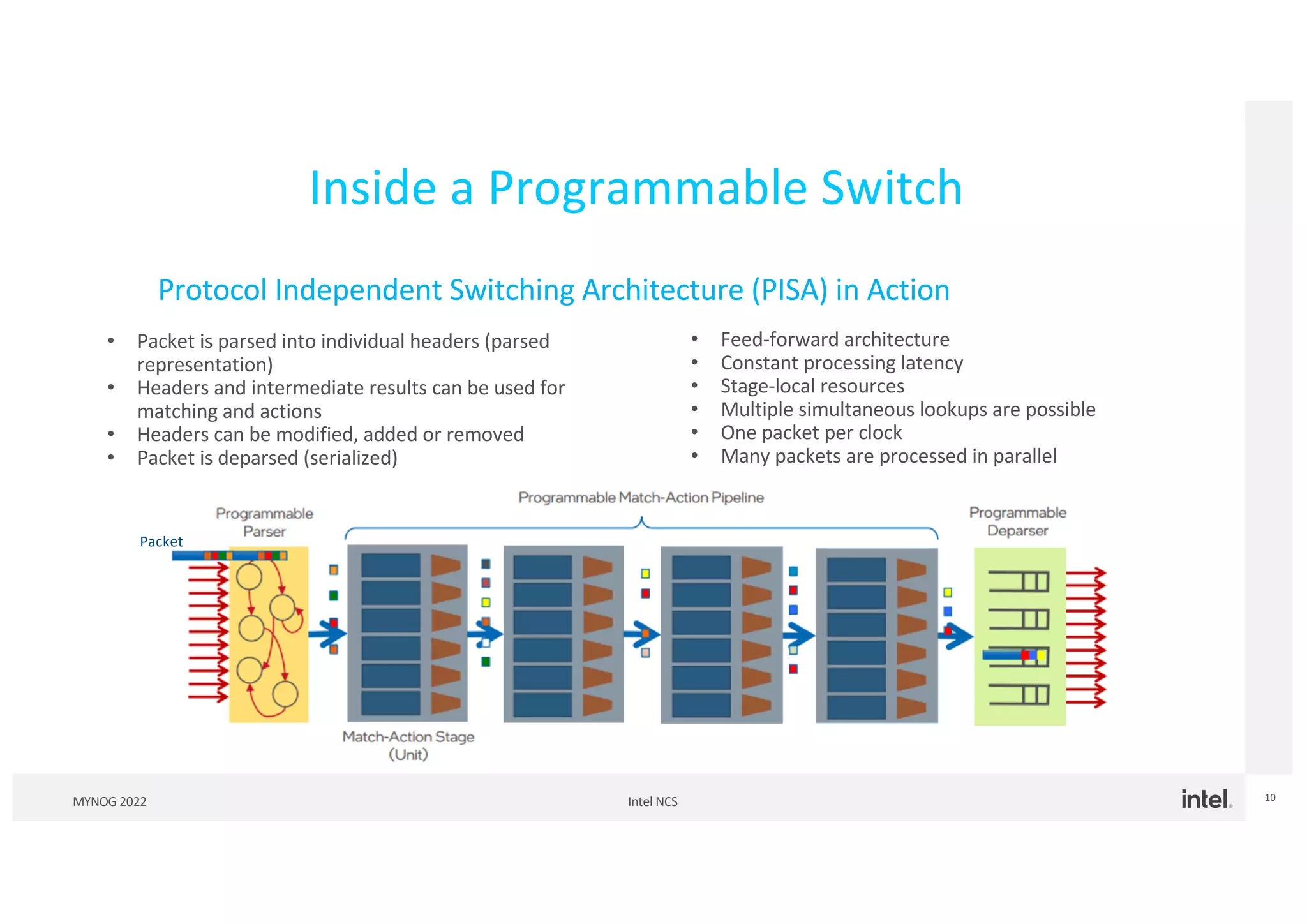

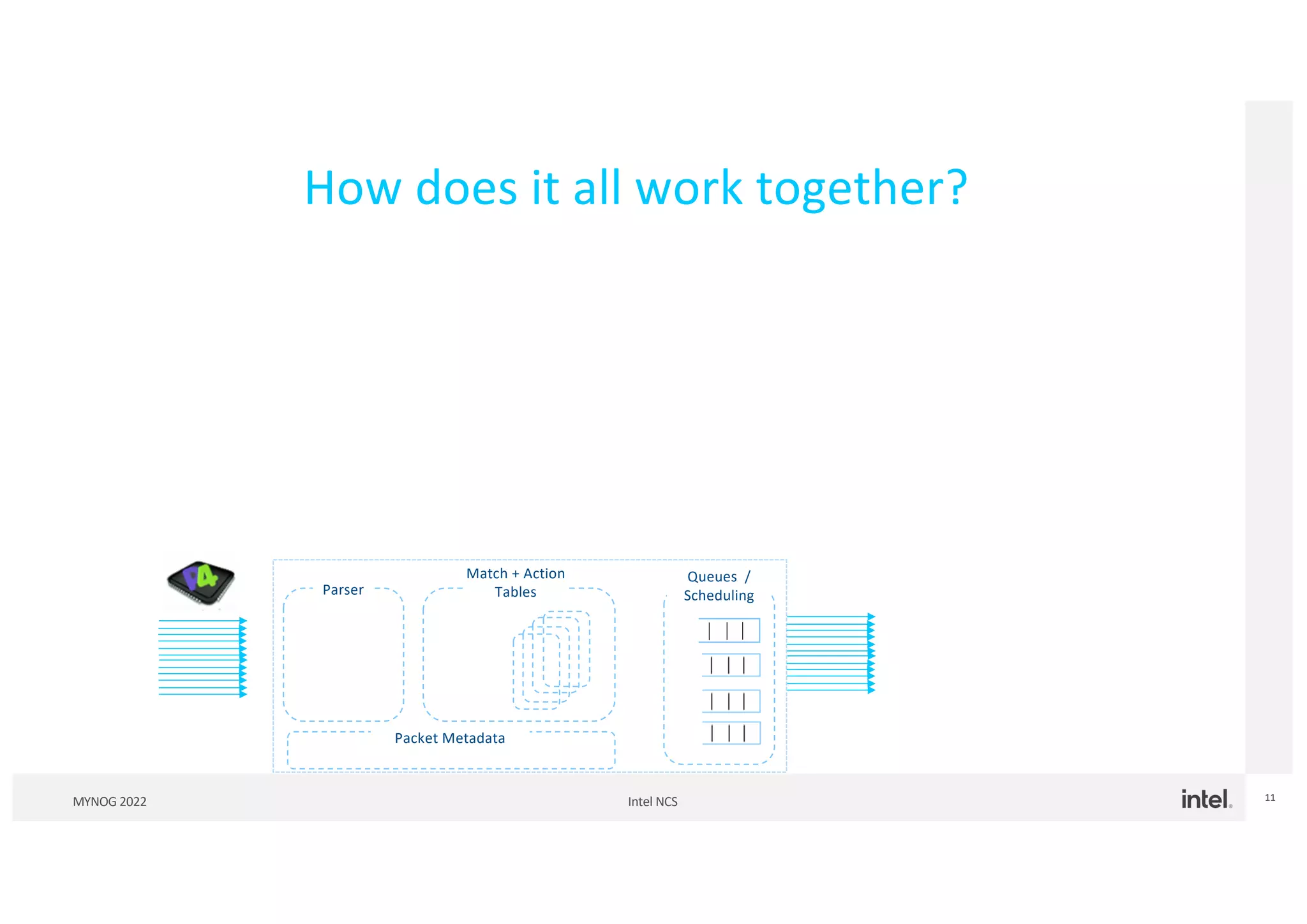

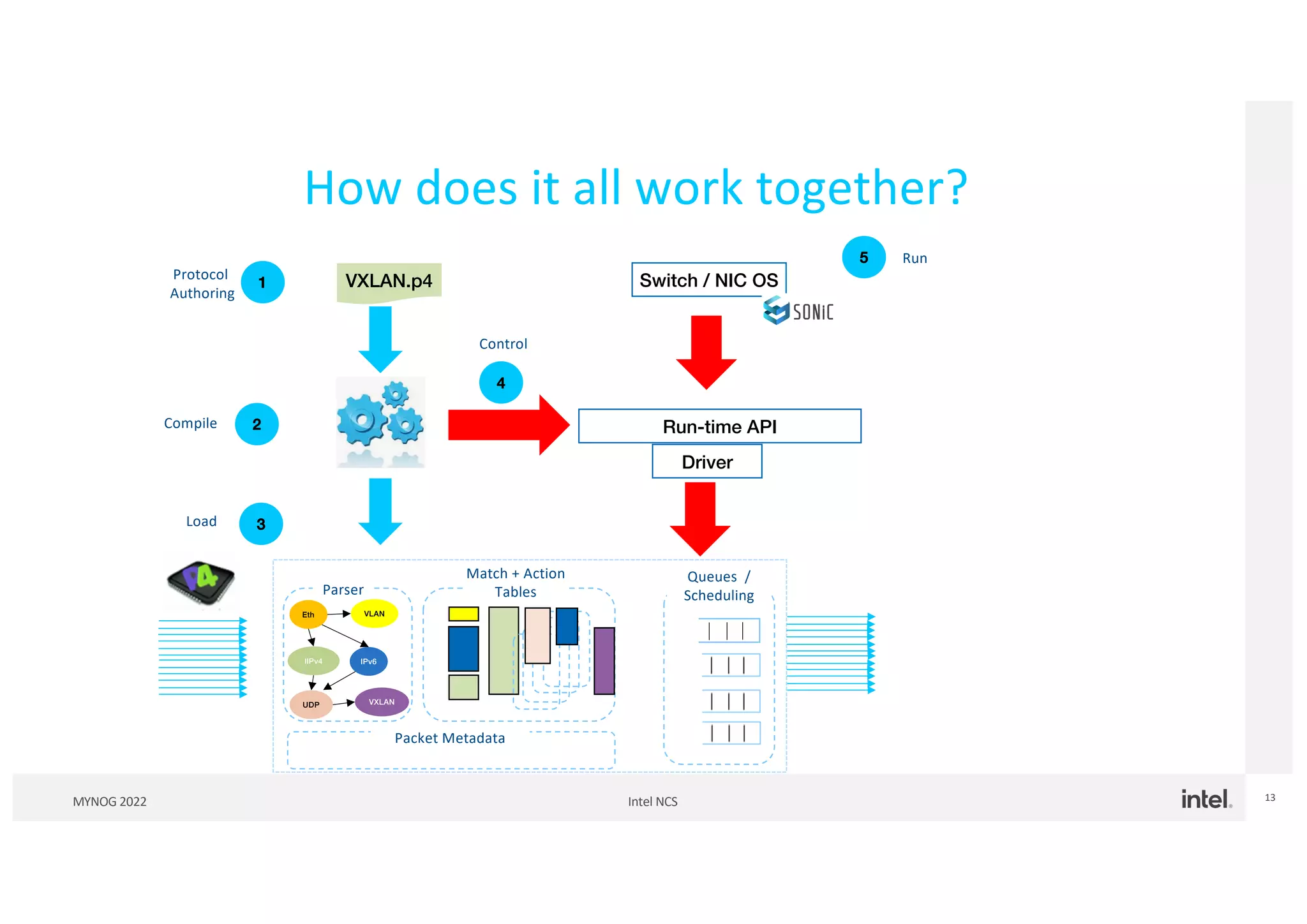

- Programmable switches implement the PISA model with a parser, match-action tables, and deparser. They can be programmed through a P4 program that is compiled for the target hardware.

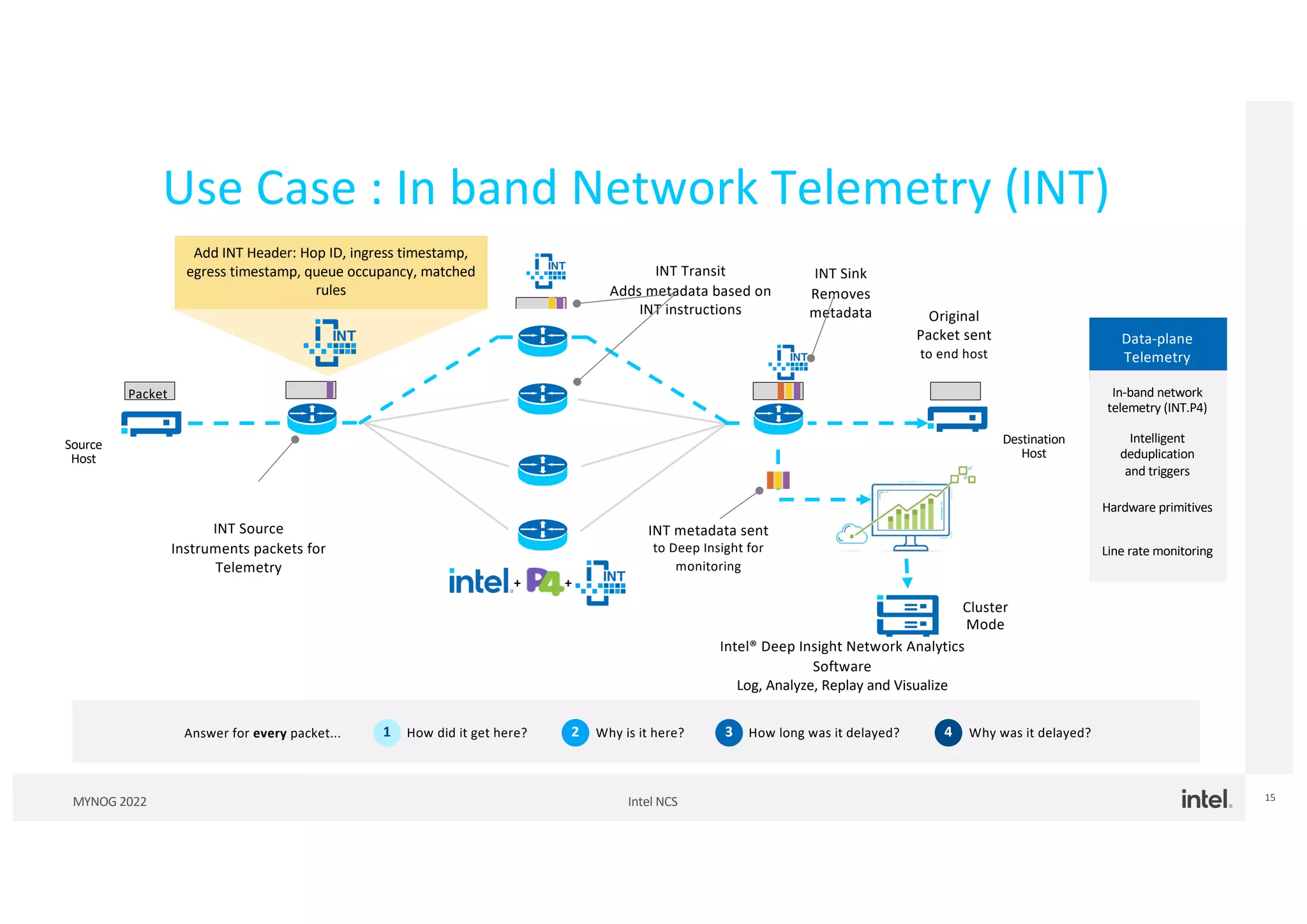

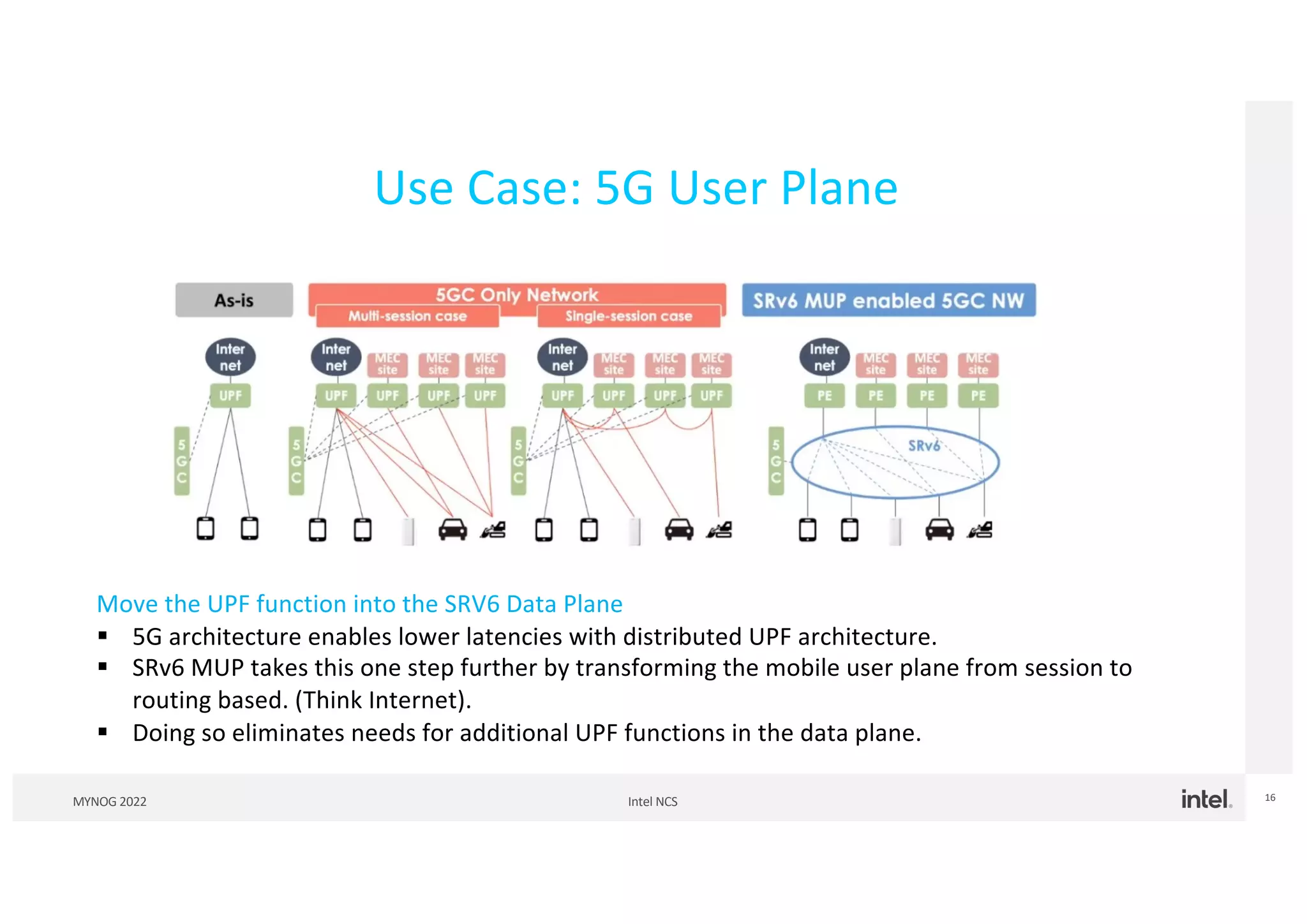

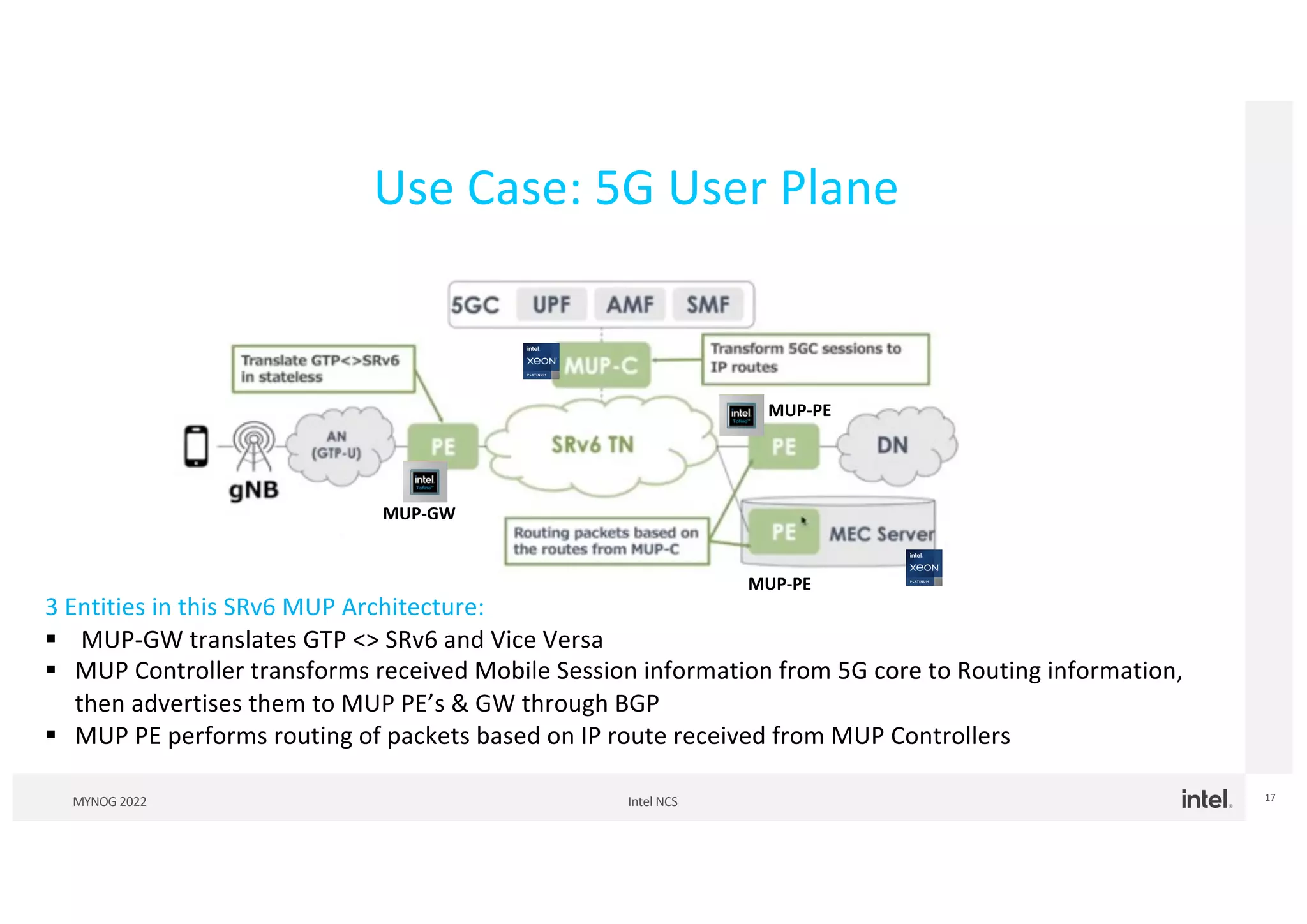

- Example applications discussed are in-band network telemetry and 5G