This document provides an alphabetical listing of instructions for the PLC-5 Programmable Instruction Controller. It includes the page number reference for each instruction. It also provides guidelines for choosing the appropriate instruction based on the desired operation in Table A and examples in Table B.

![GHVFULEHV VRPH LPSRUWDQW GLIIHUHQFHV EHWZHHQ

VROLG VWDWH HTXLSPHQW DQG KDUGZLUHG HOHFWURPHFKDQLFDO GHYLFHV

%HFDXVH RI WKLV GLIIHUHQFH DQG DOVR EHFDXVH RI WKH ZLGH YDULHW RI

XVHV IRU VROLG VWDWH HTXLSPHQW DOO SHUVRQV UHVSRQVLEOH IRU DSSOLQJ

WKLV HTXLSPHQW PXVW VDWLVI WKHPVHOYHV WKDW HDFK LQWHQGHG DSSOLFDWLRQ

RI WKLV HTXLSPHQW LV DFFHSWDEOH

,Q QR HYHQW ZLOO WKH $OOHQ%UDGOH RPSDQ EH UHVSRQVLEOH RU OLDEOH

IRU LQGLUHFW RU FRQVHTXHQWLDO GDPDJHV UHVXOWLQJ IURP WKH XVH RU

DSSOLFDWLRQ RI WKLV HTXLSPHQW

7KH H[DPSOHV DQG GLDJUDPV LQ WKLV PDQXDO DUH LQFOXGHG VROHO IRU

LOOXVWUDWLYH SXUSRVHV %HFDXVH RI WKH PDQ YDULDEOHV DQG UHTXLUHPHQWV

DVVRFLDWHG ZLWK DQ SDUWLFXODU LQVWDOODWLRQ WKH $OOHQ%UDGOH

RPSDQ FDQQRW DVVXPH UHVSRQVLELOLW RU OLDELOLW IRU DFWXDO XVH

EDVHG RQ WKH H[DPSOHV DQG GLDJUDPV

1R SDWHQW OLDELOLW LV DVVXPHG E $OOHQ%UDGOH RPSDQ ZLWK

UHVSHFW WR XVH RI LQIRUPDWLRQ FLUFXLWV HTXLSPHQW RU VRIWZDUH

GHVFULEHG LQ WKLV PDQXDO

5HSURGXFWLRQ RI WKH FRQWHQWV RI WKLV PDQXDO LQ ZKROH RU LQ SDUW

ZLWKRXW ZULWWHQ SHUPLVVLRQ RI WKH $OOHQ%UDGOH RPSDQ LV

SURKLELWHG

7KURXJKRXW WKLV PDQXDO ZH XVH QRWHV WR PDNH RX DZDUH RI

VDIHW FRQVLGHUDWLRQV

$77(17,21 ,GHQWLILHV LQIRUPDWLRQ DERXW SUDFWLFHV

RU FLUFXPVWDQFHV WKDW FDQ OHDG WR SHUVRQDO LQMXU RU

GHDWK SURSHUW GDPDJH RU HFRQRPLF ORVV

$WWHQWLRQV KHOS RX

‡ LGHQWLI D KD]DUG

‡ DYRLG WKH KD]DUG

‡ UHFRJQL]H WKH FRQVHTXHQFHV

,PSRUWDQW ,GHQWLILHV LQIRUPDWLRQ WKDW LV HVSHFLDOO LPSRUWDQW IRU

VXFFHVVIXO DSSOLFDWLRQ DQG XQGHUVWDQGLQJ RI WKH SURGXFW

@‡ur…r‡Ãv†ÃhÃ…rtv†‡r…rqÇ…hqr€h…xÂsÃD‡ryÃ8‚…ƒ‚…h‡v‚ÃYr…‚‘Ã8‚…ƒ‚…h‡v‚ÃhqÃ9 vtv‡hyÃ

@„ˆvƒ€r‡Ã8‚…ƒ‚…h‡v‚

9h‡hÃCvtuh’ÃQyˆ†Ã9CÃQG8ÃQG 8$ÃQG8$ Ã$!Ã$!%Ã$Ã$#Ã$#%Ã$#GÃ$%Ã$%GÃ

$'Ã$'%Ã$!@Ã$#@ÃhqÃ$'@Ãh…rÇ…hqr€h…x†Ã‚sÃS‚pxryyÃ6ˆ‡‚€ h‡v‚

6yyr7…hqyr’Ãv†ÃhÇ…hqr€h…xÂsÃS‚pxryyÃ6ˆ‡‚€ h‡v‚ÃhÃp‚…rÃiˆ†vr††Ã‚sÃS‚pxryyÃD‡r…h‡v‚hyÃ

8‚…ƒ‚…h‡v‚](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-3-320.jpg)

![Summary of Changes

Summary of Changes

New Information Added to 7KH OLVW EHORZ VXPPDUL]HV WKH FKDQJHV WKDW KDYH EHHQ PDGH WR WKLV

this Manual PDQXDO VLQFH WKH ODVW SULQWLQJ

For this Update Information: See Chapter:

Converting non-decimal numbers with the FRD instruction 6

How non-existing, indirect addresses affect the COP and 9

FLL instructions

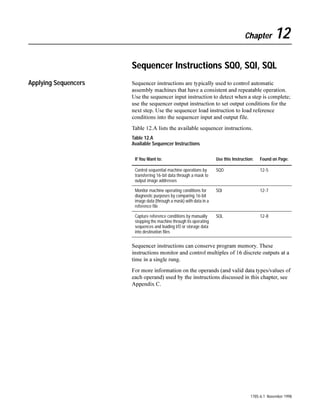

How the .POS value operates in sequencer instructions 12

Using a RET instruction 13

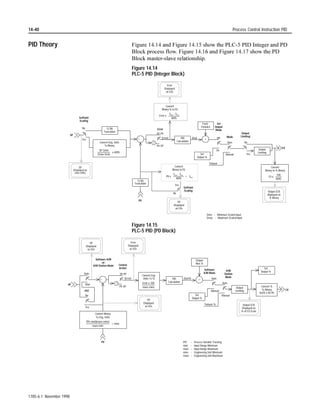

Using the PID bias term 14

Using the no zero crossing (.NOZC) and no back calculation 14

(.NOBC) features in the PD control block

Clarification to error code 89 for MSG instruction 16

Ethernet PLC-5 processors now support SLC Typed Read and 16

SLC Typed Write MSG instructions

Configuring a multihop MSG instruction over Ethernet or 16

over ControlNet

Monitoring the status of the .EN bit in a continuous 16

MSG instruction

7R KHOS RX ILQG QHZ LQIRUPDWLRQ DQG XSGDWHG LQIRUPDWLRQ LQ WKLV

UHOHDVH RI WKH PDQXDO ZH KDYH LQFOXGHG FKDQJH EDUV DV VKRZQ WR WKH

OHIW RI WKLV SDUDJUDSK

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-6-320.jpg)

![Preface

Preface

Conventions 7KLV PDQXDO XVHV WKH IROORZLQJ FRQYHQWLRQV

‡ 8QOHVV RWKHUZLVH VWDWHG

References to: Include these Allen-Bradley Processors:

Classic PLC-5 processors PLC-5/10™, -5/12™, -5/15™, -5/25™, and -5/VME™ processors.

Enhanced PLC-5 processors PLC-5/11™, -5/20™, -5/30™, -5/40™, -5/40L™, -5/60™,

-5/60L™, and -5/80™ processors.

Note: Unless otherwise specified, Enhanced PLC-5 processors include

Ethernet PLC-5, ControlNet PLC-5, Protected PLC-5 and VME PLC-5

processors.

Ethernet PLC-5 processors PLC-5/20E™, -5/40E™, and -5/80E™ processors.

ControlNet PLC-5 processors PLC-5/20C™, -5/40C™, -5/46C™, and -5/80C™ processors.

1

Protected PLC-5 processors PLC-5/26™, -5/46™, and -5/86™ processors.

VME PLC-5 processors PLC-5/V30™, -5/V40™, -5/V40L™, and -5/V80™ processors. See the

PLC-5/VME VMEbus Programmable Controllers User Manual for more

information.

Ã

Q…‚‡rp‡rqÃQG8$Ã…‚pr††‚…†Ãhy‚rÃq‚‡Ãr†ˆ…rÃQG8$Æ’†‡r€Ã†rpˆ…v‡’ÃT’†‡r€Ã†rpˆ…v‡’Ãv†ÃhÃp‚€ivh‡v‚ÂsÃ

‡urÃQ…‚‡rp‡rqÃQG8$Ã…‚pr††‚…ÇurÆ‚s‡h…rÃhqÃ’‚ˆ…Ãhƒƒyvph‡v‚Ãr‘ƒr…‡v†rÃ

‡ :RUGV LQ VTXDUH EUDFNHWV UHSUHVHQW DFWXDO NHV WKDW RX SUHVV

)RU H[DPSOH

Enter]; [F1] – Online Programming/Documentation

‡ :RUGV WKDW GHVFULEH LQIRUPDWLRQ WKDW RX KDYH WR SURYLGH DUH

VKRZQ LQ LWDOLFV )RU H[DPSOH LI RX KDYH WR WSH D ILOH QDPH WKLV

LV VKRZQ DV

filename

‡ 0HVVDJHV DQG SURPSWV WKDW WKH WHUPLQDO GLVSODV DUH VKRZQ DV

Press a function key

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-8-320.jpg)

![1-4 Relay-Type Instructions XIC, XIO, OTE, OTL, OTU, IIN, IOT, IDI, IDO

Energize (OTE)

Description: 8VH WKH 27( LQVWUXFWLRQ WR FRQWURO D ELW LQ PHPRU ,I WKH ELW

FRUUHVSRQGV WR DQ RXWSXW PRGXOH WHUPLQDO WKH GHYLFH ZLUHG WR WKLV

WHUPLQDO LV HQHUJL]HG ZKHQ WKH LQVWUXFWLRQ LV HQDEOHG DQG

Example: GHHQHUJL]HG ZKHQ WKH LQVWUXFWLRQ LV GLVDEOHG ,I WKH LQSXW FRQGLWLRQV

WKDW SUHFHGH WKH 27( LQVWUXFWLRQ DUH WUXH WKH SURFHVVRU HQDEOHV WKH

O:013 27( LQVWUXFWLRQ ,I WKH LQSXW FRQGLWLRQV WKDW SUHFHGH WKH 27(

LQVWUXFWLRQ DUH IDOVH WKH SURFHVVRU GLVDEOHV WKH 27( LQVWUXFWLRQ

01 :KHQ UXQJ FRQGLWLRQV EHFRPH IDOVH WKH FRUUHVSRQGLQJ GHYLFH

Turn ON bit O:013/01 of the output image table if GHHQHUJL]HV

the rung is true. Turn it OFF if the rung is false.

$Q 27( LQVWUXFWLRQ LV VLPLODU WR D UHOD FRLO 7KH 27( LQVWUXFWLRQ LV

This bit corresponds to output terminal 01 of a

module in /O group 3 of I/O rack 1. FRQWUROOHG E SUHFHGLQJ LQSXW LQVWUXFWLRQV WKH UHOD FRLO LV FRQWUROOHG

E FRQWDFWV LQ LWV KDUGZLUHG UXQJ

7KH 27( LQVWUXFWLRQ WHOOV WKH SURFHVVRU WR FRQWURO WKH DGGUHVVHG ELW

EDVHG RQ WKH UXQJ FRQGLWLRQ

If the Rung Is: Then the Processor Turns the Bit: Bit Logic State:

true on 1

false off 0

Latch (OTL)

Description: 7KH 27/ LQVWUXFWLRQ LV D UHWHQWLYH RXWSXW LQVWUXFWLRQ WKDW FDQ RQO

L WXUQ RQ D ELW LW FDQQRW WXUQ RII D ELW](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-31-320.jpg)

![LQVWUXFWLRQ ZLWK ERWK LQVWUXFWLRQV

Example: DGGUHVVLQJ WKH VDPH ELW

O:013

:KHQ RX DVVLJQ DQ DGGUHVV WR DQ 27/ LQVWUXFWLRQ WKDW FRUUHVSRQGV

L

01

WR D WHUPLQDO RI DQ RXWSXW PRGXOH WKH RXWSXW GHYLFH ZLUHG WR WKLV

WHUPLQDO LV HQHUJL]HG ZKHQ WKH SURFHVVRU VHWV HQDEOHV](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-33-320.jpg)

![WKH ELW UHPDLQV VHW

DQG WKH FRUUHVSRQGLQJ RXWSXW GHYLFH UHPDLQV HQHUJL]HG 8VH WKH 278

LQVWUXFWLRQ WR WXUQ 2)) WKH ELW RX ODWFKHG RQ ZLWK WKH 27/

LQVWUXFWLRQ

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-35-320.jpg)

![WKH ODVW WUXH 27/

LQVWUXFWLRQ FRQWLQXHV WR FRQWURO WKH ELW LQ PHPRU 7KH ODWFKHG RXWSXW

GHYLFH LV HQHUJL]HG HYHQ WKRXJK WKH UXQJ FRQGLWLRQV WKDW FRQWURO WKH

LQVWUXFWLRQ PD KDYH JRQH IDOVH

,PSRUWDQW 7KH 27/ LQVWUXFWLRQ LV UHWHQWLYH :KHQ WKH SURFHVVRU

ORVHV SRZHU LV VZLWFKHG WR 3URJUDP PRGH RU 7HVW

PRGH RU GHWHFWV D PDMRU IDXOW RXWSXWV JR RII EXW WKH

VWDWHV RI UHWHQWLYH RXWSXWV DUH UHWDLQHG LQ PHPRU

:KHQ WKH SURFHVVRU UHVXPHV RSHUDWLRQ LQ 5XQ PRGH

UHWHQWLYH RXWSXWV LPPHGLDWHO UHWXUQ WR WKHLU SUHYLRXV

VWDWHV 1RQUHWHQWLYH RXWSXWV VXFK DV 27( RXWSXWV DUH

UHVHW

Unlatch (OTU)

Description: 7KH 278 LQVWUXFWLRQ LV D UHWHQWLYH RXWSXW LQVWUXFWLRQ WKDW FDQ RQO

WXUQ RII D ELW LW FDQQRW WXUQ RQ D ELW](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-38-320.jpg)

![LV LQ

SURJUHVV DQG WKH ERWK RSHUDWH RQ WKH VDPH VHW RI GDWD WKH LQWHJULW RI

WKDW EORFN RI GDWD LV MHRSDUGL]HG

7R HQVXUH GDWDEORFN LQWHJULW ZULWH RXU 67, URXWLQH VR WKDW LW

RSHUDWHV RQ LWV RZQ FRS RI WKH GDWD EORFN WKDW LW QHHGV 8VH

RQWURO1HW ,PPHGLDWH 'DWD ,2 LQVWUXFWLRQV ,', DQG ,'2](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-61-320.jpg)

![RX PXVW HQWHU D SUHVHW YDOXH

IURP 7KH SURFHVVRU VWRUHV WKH SUHVHW YDOXH DV D ELW

LQWHJHU YDOXH

,PSRUWDQW 7KH 3UHVHW YDOXH RSHUDWHV GLIIHUHQWO LI RX DUH XVLQJ D

72) LQVWUXFWLRQ 6HH SDJH IRU PRUH LQIRUPDWLRQ

‡ $FFXPXODWHG 9DOXH LV WKH QXPEHU RI WLPH LQFUHPHQWV WKH

LQVWUXFWLRQ KDV FRXQWHG :KHQ HQDEOHG WKH WLPHU XSGDWHV WKLV

YDOXH FRQWLQXDOO 7SLFDOO HQWHU ]HUR ZKHQ SURJUDPPLQJ WKH

LQVWUXFWLRQ ,I RX HQWHU D YDOXH WKH LQVWUXFWLRQ VWDUWV FRXQWLQJ

WLPH EDVH LQWHUYDOV IURP WKDW YDOXH ,I WKH WLPHU LV UHVHW WKH

DFFXPXODWHG YDOXH LV ]HUR 7KH UDQJH IRU WKH DFFXPXODWHG YDOXH LV

7KH SURFHVVRU VWRUHV WKH DFFXPXODWHG YDOXH DV D ELW

LQWHJHU

,PSRUWDQW 7KH $FFXPXODWHG YDOXH RSHUDWHV GLIIHUHQWO LI RX DUH

XVLQJ D 72) LQVWUXFWLRQ 6HH SDJH IRU PRUH

LQIRUPDWLRQ

Timer Accuracy 7LPHU DFFXUDF UHIHUV WR WKH OHQJWK RI WLPH EHWZHHQ WKH PRPHQW WKH

SURFHVVRU HQDEOHV D WLPHU LQVWUXFWLRQ DQG WKH PRPHQW WKH SURFHVVRU

FRPSOHWHV WKH WLPHG LQWHUYDO 7LPHU DFFXUDF GHSHQGV RQ WKH

SURFHVVRU FORFN WROHUDQFH DQG WKH WLPH EDVH 7KH FORFN WROHUDQFH LV

± 7KLV PHDQV WKDW D WLPHU FRXOG WLPH RXW HDUO RU ODWH E

VHFRQGV PV](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-72-320.jpg)

![2-14 Timer Instructions TON, TOF, RTO Counter Instructions CTU, CTD Reset RES

‡ 3UHVHW VSHFLILHV WKH YDOXH ZKLFK WKH FRXQWHU PXVW UHDFK EHIRUH LW

VHWV WKH GRQH ELW '1 (QWHU D SUHVHW YDOXH IURP ± XS WR

7KH SUHVHW YDOXH LV VWRUHG DV D ELW LQWHJHU YDOXH

1HJDWLYH YDOXHV DUH VWRUHG LQ WZRV FRPSOHPHQW IRUP

‡ $FFXPXODWHG 9DOXH LV WKH FXUUHQW FRXQW EDVHG RQ WKH QXPEHU RI

WLPHV WKH UXQJ JRHV IURP IDOVH WR WUXH 7KH DFFXPXODWHG YDOXH LV

VWRUHG DV D ELW LQWHJHU YDOXH 1HJDWLYH YDOXHV DUH VWRUHG LQ

WZRV FRPSOHPHQW IRUP 7KH UDQJH RI WKH DFFXPXODWHG YDOXH LV ±

WR 7SLFDOO RX HQWHU D ]HUR YDOXH ZKHQ

SURJUDPPLQJ FRXQWHU LQVWUXFWLRQV ,I RX HQWHU D QRQ]HUR YDOXH

WKH LQVWUXFWLRQ VWDUWV FRXQWLQJ IURP WKDW YDOXH ,I WKH FRXQWHU LV

UHVHW WKH DFFXPXODWHG YDOXH LV VHW WR ]HUR

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-100-320.jpg)

![WKDW KDV WKH VDPH DGGUHVV DV

WKH FRXQWHU

Using Status Bits

([DPLQH VWDWXV ELWV LQ WKH ODGGHU SURJUDP WR WULJJHU VRPH HYHQW 7KH

SURFHVVRU FKDQJHV WKH VWDWHV RI VWDWXV ELWV ZKHQ WKH SURFHVVRU UXQV WKH

78 LQVWUXFWLRQ RX DGGUHVV WKH VWDWXV ELWV E PQHPRQLF

This Bit: Is Set: And Remains Set Until One of the Following Occurs:

Count Up when the rung goes true to indicate the • the rung goes false

Enable Bit .CU (bit 15) instruction has increased its count • a RES instruction resets the .DN bit

Note: During prescan, this bit is set to prevent

a false count when the program scan begins.

Count Up when the accumulated value is greater than or • the accumulated value counts below the preset, either

Done Bit .DN (bit 13) equal to the preset value by using a CTD instruction to count down or changing

the accumulated value

• a RES instruction resets the .DN bit

Count Up when the up counter has exceeded the upper • a RES instruction resets the .DN bit

Overflow Bit .OV (bit 12) limit of +32,767 and has wrapped around to – • counting back down to 32,767 with a CTD instruction

32,768. The CTU counts up from there. with the same address

$77(17,21 3ODFH FULWLFDO FRXQWHUV RXWVLGH DQ 05

]RQH RU MXPSHG VHFWLRQV RI ODGGHU SURJUDP WR JXDUG

DJDLQVW LQYDOLG UHVXOWV WKDW FRXOG OHDG WR GDPDJHG

HTXLSPHQW RU SHUVRQQHO LQMXU

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-102-320.jpg)

![WKDW KDV WKH VDPH DGGUHVV DV

WKH 7' LQVWUXFWLRQ

Using Status Bits

([DPLQH VWDWXV ELWV LQ WKH ODGGHU SURJUDP WR WULJJHU VRPH HYHQW 7KH

SURFHVVRU FKDQJHV WKH VWDWHV RI VWDWXV ELWV ZKHQ WKH SURFHVVRU UXQV

WKLV LQVWUXFWLRQ RX DGGUHVV WKH VWDWXV ELWV E PQHPRQLF

This Bit: Is Set: And Remains Set Until One of the Following Occurs:

Count Down when the rung goes true to indicate that the • the rung goes false

Enable Bit .CD (bit 14) counter is enabled as a down-counter. • a RES instruction resets the .DN bit

Note: During prescan, this bit is set to prevent

a false count when the program scan begins.

Count Down when the accumulated value is greater than or • the accumulated value counts below the preset

Done Bit .DN (bit 13) equal to the preset value. • another instruction changes the accumulated value

• a RES instruction resets the .DN bit

Count Down by the processor to show that the down • a RES instruction resets the .DN bit

Underflow Bit (.UN) (Bit 11) counter went below the lower limit of –32,768 • count back up to -32,768 with a CTU instruction

and has wrapped around to +32,767. The CTD

instruction counts down from there.

$77(17,21 3ODFH FULWLFDO FRXQWHUV RXWVLGH DQ 05

]RQH RU MXPSHG VHFWLRQV RI ODGGHU SURJUDP WR JXDUG

DJDLQVW LQYDOLG UHVXOWV WKDW FRXOG OHDG WR GDPDJHG

HTXLSPHQW RU SHUVRQQHO LQMXU

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-105-320.jpg)

![2-20 Timer Instructions TON, TOF, RTO Counter Instructions CTU, CTD Reset RES

Timer and Counter Reset (RES)

Description: 7KH 5(6 LQVWUXFWLRQ LV DQ RXWSXW LQVWUXFWLRQ WKDW UHVHWV D WLPHU RU

FRXQWHU 7KH 5(6 LQVWUXFWLRQ H[HFXWHV ZKHQ LWV UXQJ LV WUXH

RES

When Using a RES Instruction for a: The Processor Resets the:

Timer .ACC value

(Do not use a RES instruction for a TOF.) .EN bit

.TT bit

.DN bit

Counter .ACC value

.EN bit

.OV or .UN bit

.DN bit

,I WKH FRXQWHU UXQJ LV HQDEOHG WKH 8 RU ' ELW ZLOO EH UHVHW DV ORQJ

DV WKH 5(6 LQVWUXFWLRQ LV HQDEOHG

,PSRUWDQW RX FDQ XVH D QHJDWLYH SUHVHW YDOXH LQ D 78 RU 7'

LQVWUXFWLRQ LI RX LQWHQG WR XVH WKH 5(6 LQVWUXFWLRQ

+RZHYHU QRWH WKDW WKH 5(6 LQVWUXFWLRQ VHWV WKH

DFFXPXODWHG YDOXH WR ]HUR ZKLFK PD VHW WKH '1 ELW

DQG SUHYHQW WKH 78 RU 7' LQVWUXFWLRQ IURP RSHUDWLQJ

WKH QH[W WLPH LW LV HQDEOHG

$77(17,21 %HFDXVH WKH 5(6 LQVWUXFWLRQ UHVHWV WKH

DFFXPXODWHG YDOXH '1 ELW DQG 77 ELW RI D WLPLQJ

LQVWUXFWLRQ GR QRW XVH WKH 5(6 LQVWUXFWLRQ WR UHVHW D 72)

LQVWUXFWLRQ XQSUHGLFWDEOH PDFKLQH RSHUDWLRQ RU LQMXU

WR SHUVRQQHO PD RFFXU

Figure 2.13

Example RES Ladder Diagram

I:012 CTD

COUNT DOWN CD

10 Each time the input goes from false to true, the Counter C5:0

processor decrements the counter by 1.

Preset 4 DN

Accum 8

C5:0 Tells when the count is reached (ACC or = PRE) O:020

DN 01

I:017 Resets the counter C5:0

RES

12

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-108-320.jpg)

![4-4 Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY

)RU H[DPSOH LI YDOXH 1 DQG 1

YDOXH 1 DQG 1

UHVXOW 1 DQG 1

DQG RX ZDQW WR DGG YDOXH WR YDOXH RXU ODGGHU SURJUDP ZRXOG EH

I:012 ADD

]

] ADD

10 Add the lower words of value1 and value2. Source A N7:1

Source B N7:3

Dest N7:5

I:012 AND

ADD

]

] BITWISE AND

10 Capture the carry bit. S:0

Source A

Source B 1

Dest N7:4

I:012 ADD

]

] ADD

10 Add the high word of value1 to the carry bit.

Source A N7:0

Source B N7:4

Dest N7:4

I:012 ADD

]

]

ADD

10 Add the high word of value2 to this sum. Source A N7:2

Source B N7:4

Dest N7:4

Using Floating Point Data Types )RU DQ (QKDQFHG 3/ SURFHVVRU LI RX XVH IORDWLQJ SRLQW GDWD

WSHV DQG WKH UHVXOW LV WRR ODUJH RU LI LW LV XQGHILQHG LH QDWXUDO ORJ RI](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-149-320.jpg)

![Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY 4-9

Example:

I:012 CPT

]

] COMPUTE

10

Destination N7:20

Expression

(N7:1 * 5) | (N7:2 | 7)

If the input word 12, bit 10 is set, multiply the value of N7:1 by 5. Divide this result by the quotient of N7:2 divided by 7.

If N7:1=5 and N7:2=9, the result is 25. (The result is rounded to the nearest whole number because the constants 5 and 7

were specified as whole numbers.)

:KHQ RX XVH FRPSOH[ H[SUHVVLRQV LI DQ RSHUDQG LV IORDWLQJ SRLQW

WKH HQWLUH H[SUHVVLRQ LV HYDOXDWHG DV IORDWLQJ SRLQW

Example:

I:012 CPT

]

] COMPUTE

10 Destination N7:20

Expression

(N7:1 * 5.0) | (N7:2 | 7.0)

If the input word 12, bit 10 is set, multiply the value of N7:1 by 5. Divide this result by the quotient of N7:2 divided by 7. If N7:1=5 and

N7:2=9, the result is 19. (The result is rounded differently because the constants 5.0 and 7.0 were specified to 1 decimal place.

Entering the Destination

(QWHU D GLUHFW RU LQGLUHFW ORJLFDO DGGUHVV IRU WKH GHVWLQDWLRQ 7KH

LQVWUXFWLRQ VWRUHV WKH UHVXOW RI WKH RSHUDWLRQ LQ WKH GHVWLQDWLRQ DGGUHVV

,PSRUWDQW 7KH SURFHVVRU DXWRPDWLFDOO FRQYHUWV WKH GDWD WSH

VSHFLILHG E WKH VRXUFH DGGUHVV WR WKDW VSHFLILHG E WKH

GHVWLQDWLRQ DGGUHVV 7KH SURFHVVRU XVHV %' IRU GLVSOD

RU FRPSDWLELOLW ZLWK 3/ IDPLO SURFHVVRUV RX

PXVW SURJUDP DQ %' FRQYHUVLRQV

Using CPT Functions

8VH IXQFWLRQV WR RSHUDWH RQ RQH RU PRUH YDOXHV LQ WKH H[SUHVVLRQ RI D

37 LQVWUXFWLRQ WR SHUIRUP WKHVH WSHV RI RSHUDWLRQV

‡ FRQYHUW IURP RQH QXPEHU IRUPDW WR DQRWKHU

‡ PDQLSXODWH QXPEHUV

‡ SHUIRUP WULJRQRPHWULF IXQFWLRQV

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-165-320.jpg)

![Table 4.G

Updating Arithmetic Status Flags for an ACS Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) always resets

Example:

I:012 ACS

]

] ARCCOSINE

Source F8:19

10 0.7853982

Destination F8:20

0.6674572

If input word 12, bit 10 is set, take the arc cosine of the value in F8:19 and store the result in F8:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-172-320.jpg)

![Table 4.H

Updating Arithmetic Status Flags for an ADD Instruction

With this Bit: The Processor:

Carry (C) sets if carry generated; otherwise resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 ADD

]

] ADD

10 Source A N7:3

Source B N7:4

Destination N7:20

If input word 12, bit 10 is set, add the value in N7:3 to the value in N7:4 and store the result in N7:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-176-320.jpg)

![Table 4.I

Updating Arithmetic Status Flags for an ASN Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) always resets

Example:

I:012 ASN

]

]

ARCSINE

10 Source F8:17

0.7853982

Dest F8:18

0.9033391

If input word 12, bit 10 is set, take the arc sine of the value in F8:17 and store the result in F8:18.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-180-320.jpg)

![ARCTANGENT

Source

6HH 7DEOH - IRU VWDWXV IODJV IRU $71 LQVWUXFWLRQ

Destination

Table 4.J

Updating Arithmetic Status Flags for an ATN Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 ATN

ARCTANGENT

]

]

10 Source F8:21

0.7853982

Destination F8:22

0.6657737

If input word 12, bit 10 is set, take the arc tangent of the value in F8:21 and store the result in F8:22.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-184-320.jpg)

![4-16 Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY

Using Status Bits

7R XVH WKH $9( LQVWUXFWLRQ FRUUHFWO H[DPLQH VWDWXV ELWV LQ WKH

FRQWURO VWUXFWXUH $GGUHVV WKHVH ELWV E PQHPRQLF

This Bit: Is Set:

Enable .EN (bit 15) on a false-to-true rung transition to indicate that the instruction

is enabled. The instruction follows the rung condition.

Done .DN (bit 13) after the instruction finishes operating. After the rung goes

false, the processor resets the .DN bit on the next false-to-true

rung transition.

Error .ER (bit 11) when the operation generates an overflow. The instruction

stops until the ladder program resets the .ER bit.

,PSRUWDQW 7KH $9( LQVWUXFWLRQ FDOFXODWHV WKH DYHUDJH XVLQJ

IORDWLQJ SRLQW UHJDUGOHVV RI WKH WSH VSHFLILHG IRU WKH ILOH

RU GHVWLQDWLRQ SDUDPHWHUV

$77(17,21 7KH $9( LQVWUXFWLRQ LQFUHPHQWV WKH

RIIVHW YDOXH VWRUHG DW 6 0DNH VXUH RX PRQLWRU RU

ORDG WKH RIIVHW YDOXH RX ZDQW SULRU WR XVLQJ DQ LQGH[HG

DGGUHVV 2WKHUZLVH XQSUHGLFWDEOH PDFKLQH RSHUDWLRQ

FRXOG RFFXU ZLWK SRVVLEOH GDPDJH WR HTXLSPHQW DQGRU

LQMXU WR SHUVRQQHO

Example:

I:012 AVE

]

] AVERAGE FILE EN

10 File #N7:1

Dest N7:0 DN

Control R6:0

Length 4

Position 0

R6:0 O:010

]

]

EN 5

R6:0 O:010

]

]

DN 7

R6:0

RES

If input word 12, bit 10 is set, the AVE instruction is enabled. The values in N7:1, N7:2, N7:3, and N7:4 are

added together and divided by 4. The result is stored in N7:0. When the calculation is complete, output

word 10, bit 7 is set. Then the RES instruction resets the status bits of the control file R6:0.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-189-320.jpg)

![Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY 4-17

Clear (CLR)

Description: 8VH WKH /5 LQVWUXFWLRQ WR VHW DOO WKH ELWV RI D ZRUG WR ]HUR 7KH

CLR

GHVWLQDWLRQ PXVW EH D ZRUG DGGUHVV 6HH 7DEOH / IRU VWDWXV IODJV IRU

CLEAR /5 LQVWUXFWLRQ

Destination Table 4.L

Updating Arithmetic Status Flags for a CLR Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) always resets

Zero (Z) always sets

Sign (S) always resets

Example:

I:012 CLR

]

]

CLEAR

10 Destination N7:3

If input word 12, bit 10 is set, clear all of the bits in N7:3 to zero.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-190-320.jpg)

![DQG VWRUH WKH UHVXOW LQ WKH 'HVWLQDWLRQ 6HH 7DEOH 0 IRU

COS

VWDWXV IODJV IRU 26 LQVWUXFWLRQ

COSINE

Source 7KH 6RXUFH PXVW EH JUHDWHU WKDQ RU HTXDO WR ± DQG OHVV WKDQ

Destination RU HTXDO WR ,I LW LV QRW LQ WKLV UDQJH WKH SURFHVVRU UHWXUQV D

!INF! UHVXOW LQ WKH 'HVWLQDWLRQ 7KH UHVXOWLQJ YDOXH LQ WKH

'HVWLQDWLRQ LV DOZDV JUHDWHU WKDQ RU HTXDO WR ± DQG OHVV WKDQ RU

HTXDO WR

,PSRUWDQW )RU JUHDWHVW DFFXUDF WKH VRXUFH GDWD VKRXOG EH JUHDWHU

WKDQ RU HTXDO WR ±π DQG OHVV WKDQ RU HTXDO WR π

Table 4.M

Updating Arithmetic Status Flags for an COS Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 COS

]

] COSINE

10 Source F8:13

0.7853982

Destination F8:14

0.7071068

If input word 12, bit 10 is set, take the cosine of the value in F8:13 and store the result in F8:14.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-192-320.jpg)

![Table 4.N

Updating Arithmetic Status Flags for a DIV Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if division by zero or if overflow generated;

otherwise resets

Zero (Z) sets if result is zero; otherwise resets;

undefined if overflow is set

Sign (S) sets if result is negative; otherwise resets;

undefined if overflow is set

Example:

I:012 DIV

]

] DIVIDE

10 Source A N7:3

Source B N7:4

Destination N7:20

If input word 12, bit 10 is set, divide the value in N7:3 by the value in N7:4 and store the result in N7:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-196-320.jpg)

![4-20 Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY

Natural Log (LN)

(Enhanced PLC-5 Processors Only)

Description: 8VH WKH /1 LQVWUXFWLRQ WR WDNH WKH QDWXUDO ORJ RI WKH YDOXH LQ WKH

LN 6RXUFH DQG VWRUH WKH UHVXOW LQ WKH 'HVWLQDWLRQ 6HH 7DEOH 2 IRU VWDWXV

NATURAL LOG IODJV IRU /1 LQVWUXFWLRQ

Source

,I WKH 6RXUFH LV HTXDO WR WKH UHVXOW LQ WKH 'HVWLQDWLRQ ZLOO EH

Destination

!-INF! LI WKH YDOXH LQ WKH 6RXUFH LV OHVV WKDQ WKH UHVXOW LQ WKH

'HVWLQDWLRQ ZLOO EH !NAN! 7KH UHVXOWLQJ YDOXH LQ WKH 'HVWLQDWLRQ LV

DOZDV JUHDWHU WKDQ RU HTXDO WR ± DQG OHVV WKDQ RU HTXDO WR

Table 4.O

Updating Arithmetic Status Flags for an LN Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 LN

]

] NATURAL LOG

10 Source N7:0

5

Destination F8:20

1.609438

If input word 12, bit 10 is set, take the natural log of the value in N7:0 and store the result in F8:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-197-320.jpg)

![Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY 4-21

Log to the Base 10 (LOG)

(Enhanced PLC-5 Processors Only)

Description: 8VH WKH /2* LQVWUXFWLRQ WR WDNH WKH ORJ EDVH RI WKH YDOXH LQ WKH

LOG

6RXUFH DQG VWRUH WKH UHVXOW LQ WKH 'HVWLQDWLRQ 6HH 7DEOH 3 IRU VWDWXV

LOG BASE 10

IODJV IRU /2* LQVWUXFWLRQ

Source

,I WKH 6RXUFH LV HTXDO WR WKH UHVXOW LQ WKH 'HVWLQDWLRQ ZLOO EH

Destination

!-INF! LI WKH YDOXH LQ WKH 6RXUFH LV OHVV WKDQ WKH UHVXOW LQ WKH

'HVWLQDWLRQ ZLOO EH !NAN! 7KH UHVXOWLQJ YDOXH LQ WKH 'HVWLQDWLRQ LV

DOZDV JUHDWHU WKDQ RU HTXDO WR ± DQG OHVV WKDQ RU HTXDO WR

Table 4.P

Updating Arithmetic Status Flags for an LOG Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 LOG

]

] LOG BASE 10

10 Source N7:2

5

Destination F8:3

0.6989700

If input word 12, bit 10 is set, take the log base 10 of the value in N7:2 and store the result in F8:3.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-198-320.jpg)

![DQG SODFH WKH UHVXOW LQ WKH GHVWLQDWLRQ 6RXUFH $ DQG

MUL

6RXUFH % FDQ EH YDOXHV RU DGGUHVVHV 6HH 7DEOH 4 IRU VWDWXV IODJV IRU

MULTIPLY

08/ LQVWUXFWLRQ

Source A

Source B Table 4.Q

Updating Arithmetic Status Flags for a MUL Instruction

Destination

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 MUL

]

] MULTIPLY

10 Source A N7:3

Source B N7:4

Destination N7:20

If input word 12, bit 10 is set, multiply the value in N7:3 by the value in N7:4 and store the result in N7:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-201-320.jpg)

![Table 4.R

Updating Arithmetic Status Flags for a NEG Instruction

With this Bit: The Processor:

Carry (C) sets if the operation generates a carry

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 NEG

]

] NEGATE

10 Source N7:3

Destination N7:20

If input word 12, bit 10 is set, take the opposite sign of the value in N7:3 and store the result in N7:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-203-320.jpg)

![DQG VWRUH WKH UHVXOW LQ WKH 'HVWLQDWLRQ 6HH 7DEOH 6 IRU

SIN

SINE

VWDWXV IODJV IRU 6,1 LQVWUXFWLRQ

Source

7KH 6RXUFH PXVW EH JUHDWHU WKDQ RU HTXDO WR ± DQG OHVV WKDQ

Destination

RU HTXDO WR ,I LW LV QRW LQ WKLV UDQJH WKH SURFHVVRU UHWXUQV D

!INF! UHVXOW LQ WKH 'HVWLQDWLRQ 7KH UHVXOWLQJ YDOXH LQ WKH

'HVWLQDWLRQ LV DOZDV JUHDWHU WKDQ RU HTXDO WR ± DQG OHVV WKDQ RU

HTXDO WR

,PSRUWDQW )RU JUHDWHVW DFFXUDF WKH VRXUFH GDWD VKRXOG EH JUHDWHU

WKDQ RU HTXDO WR ±π DQG OHVV WKDQ RU HTXDO WR π

Table 4.S

Updating Arithmetic Status Flags for an SIN Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 SIN

]

] SINE

Source F8:11

10

0.7853982

Destination F8:12

0.7071068

If input word 12, bit 10 is set, take the sine of F8:11 and store the result in F8:12.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-205-320.jpg)

![Table 4.T

Updating Arithmetic Status Flags for a SQR Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated during floating-point

to integer conversion; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) always resets

Example:

I:012 SQR

]

] SQUARE ROOT

10 Source N7:3

Destination N7:20

If input word 12, bit 10 is set, take the square root of the value in N7:3 and store the result in N7:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-207-320.jpg)

![Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY 4-27

Using Status Bits

7R XVH WKH 657 LQVWUXFWLRQ FRUUHFWO WKH ODGGHU SURJUDP PXVW

H[DPLQH VWDWXV ELWV LQ WKH FRQWURO VWUXFWXUH RX DGGUHVV WKHVH ELWV

E PQHPRQLF

This Bit: Is Set:

Enable .EN (bit 15) on a false-to-true rung transition to indicate that the instruction is

enabled. The instruction follows the rung condition.

Done .DN (bit 13) after the instruction finishes operating. After the rung goes false,

the processor resets the .DN bit on the next false-to-true rung

transition.

Error .ER (bit 11) when the length value is less than or equal to zero or when the

position value is less than zero.

$77(17,21 7KH 657 LQVWUXFWLRQ PDQLSXODWHV WKH

RIIVHW YDOXH VWRUHG DW 6 0DNH VXUH RX PRQLWRU RU

ORDG WKH RIIVHW YDOXH RX ZDQW SULRU WR XVLQJ DQ LQGH[HG

DGGUHVV 2WKHUZLVH XQSUHGLFWDEOH PDFKLQH RSHUDWLRQ

FRXOG RFFXU ZLWK SRVVLEOH GDPDJH WR HTXLSPHQW DQGRU

LQMXU WR SHUVRQQHO

Example:

I:012 SRT

]

] SORT FILE EN

10 File #N7:1

Control R6:0

Length 4 DN

Position 0

R6:0 O:010

]

]

EN 5

R6:0 O:010

]

]

DN 7

If input word 12, bit 10 is set, the SRT instruction is enabled. The elements N7:1, N7:2, N7:3, and N7:4 are sorted into ascending

order. When the sort operation is complete, output word 10, bit 7 is set.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-209-320.jpg)

![4-30 Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY

,PSRUWDQW 7KH 67' LQVWUXFWLRQ FDOFXODWHV WKH VWDQGDUG GHYLDWLRQ

XVLQJ IORDWLQJ SRLQW UHJDUGOHVV RI WKH WSH VSHFLILHG IRU

WKH ILOH RU GHVWLQDWLRQ SDUDPHWHUV

$77(17,21 7KH 67' LQVWUXFWLRQ PDQLSXODWHV WKH

RIIVHW YDOXH VWRUHG DW 6 0DNH VXUH RX PRQLWRU RU

ORDG WKH RIIVHW YDOXH RX ZDQW SULRU WR XVLQJ DQ LQGH[HG

DGGUHVV 2WKHUZLVH XQSUHGLFWDEOH PDFKLQH RSHUDWLRQ

FRXOG RFFXU ZLWK SRVVLEOH GDPDJH WR HTXLSPHQW DQGRU

LQMXU WR SHUVRQQHO

Example:

I:012 STD

]

] STANDARD DEVIATION EN

10 File #N7:1

Destination N7:0

Control R6:0 DN

Length 4

Position 0

R6:0 O:010

]

]

EN 5

R6:0 O:010

]

]

DN 7

R6:0

RES

If input word 12, bit 10 is set, the STD instruction is enabled. The elements N7:1, N7:2, N7:3, and N7:4 are used to calculate the

standard deviation. When the calculation is complete, output word 10, bit 7 is set. Then the RES instruction resets the status bits of

the control file R6:0.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-215-320.jpg)

![Table 4.V

Updating Arithmetic Status Flags for a SUB Instruction

With this Bit: The Processor:

Carry (C) sets if borrow generated; otherwise resets

Overflow (V) sets if underflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 SUB

]

] SUBTRACT

10 Source A N7:3

Source B N7:4

Destination N7:20

If input word 12, bit 10 is set, subtract the value in N7:4 from the value in N7:3 and store the result in N7:20.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-219-320.jpg)

![DQG VWRUH WKH UHVXOW LQ WKH 'HVWLQDWLRQ 6HH 7DEOH : IRU

TAN

TANGENT

VWDWXV IODJV IRU 7$1 LQVWUXFWLRQ

Source

7KH YDOXH LQ WKH 6RXUFH PXVW EH JUHDWHU WKDQ RU HTXDO WR ±

Destination

DQG OHVV WKDQ RU HTXDO WR ,I LW LV QRW LQ WKLV UDQJH WKH

SURFHVVRU UHWXUQV D !INF! UHVXOW LQ WKH 'HVWLQDWLRQ 7KH UHVXOWLQJ

YDOXH LQ WKH 'HVWLQDWLRQ LV DOZDV D UHDO QXPEHU

,PSRUWDQW )RU JUHDWHVW DFFXUDF WKH VRXUFH GDWD VKRXOG EH JUHDWHU

WKDQ RU HTXDO WR ±π DQG OHVV WKDQ RU HTXDO WR π

Table 4.W

Updating Arithmetic Status Flags for an TAN Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 TAN

]

] TANGENT

10 Source F8:15

0.7853982

Destination F8:16

1.000000

If input word 12, bit 10 is set, take the tangent of the value in F8:15 and store the result in F8:16.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-221-320.jpg)

![DQG IRU LQWHJHUV LV HTXDO

WR ±.

Table 4.X

Updating Arithmetic Status Flags for an XPY Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 XPY

]

] X TO POWER OF Y

10 Source A N7:4

5

Source B N7:5

2

Destination N7:6

25

If input word 12, bit 10 is set, take the value in N7:4, raise it to the power of the value in N7:5, and stores

the result in N7:6.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-230-320.jpg)

![6-2 Conversion Instructions FRD and TOD, DEG and RAD

Convert to BCD (TOD)

Description: 8VH WKH 72' LQVWUXFWLRQ WR FRQYHUW DQ LQWHJHU YDOXH WR D %' YDOXH

,I WKH LQWHJHU YDOXH LV JUHDWHU WKDQ WKH SURFHVVRU VWRUHV DQG

TOD

VHWV WKH RYHUIORZ ELW ,I WKH LQWHJHU YDOXH LV QHJDWLYH WKH SURFHVVRU

TO BCD

VWRUHV LQ WKH GHVWLQDWLRQ DQG VHWV WKH RYHUIORZ DQG ]HUR VWDWXV ELWV

Source

Table 6.C

Destination

Updating Arithmetic Status Flags for a TOD Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if integer value is outside the range

0-9999; otherwise resets

Zero (Z) sets if destination value is negative or

zero; otherwise resets

Sign (S) always resets

Example:

I:012 TOD

]

] TO BCD

10 Source N7:3

Destination D9:3

If input word 12, bit 10 is set, convert the value in N7:3 to a BCD value and store the result in D9:3.

Convert from BCD (FRD)

Description: 8VH WKH )5' LQVWUXFWLRQ WR FRQYHUW D %' YDOXH WR DQ LQWHJHU YDOXH

RQYHUW %' YDOXHV WR LQWHJHU YDOXHV EHIRUH RX PDQLSXODWH WKRVH

FRD

YDOXHV ZLWK ODGGHU ORJLF EHFDXVH WKH SURFHVVRU WUHDWV %' YDOXHV DV

FROM BCD LQWHJHU YDOXHV 7KH DFWXDO %' YDOXH PD EH ORVW RU GLVWRUWHG

Source

Table 6.D

Destination

Updating Arithmetic Status Flags for a TOD Instruction

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) always resets

Zero (Z) sets if destination value is zero; otherwise resets

Sign (S) always resets

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-249-320.jpg)

![Conversion Instructions FRD and TOD, DEG and RAD 6-3

7KH )5' LQVWUXFWLRQ ZLOO FRQYHUW D QRQGHFLPDO QXPEHU ZLWKRXW DQ

HUURU FRQGLWLRQ )RU H[DPSOH LI D ³´ LV LQ WKH VRXUFH LW LV FRQYHUWHG

WR ³´ HYHQ WKRXJK ³´ LV QRW D YDOLG GHFLPDO QXPEHU

Example:

I:012 FRD

]

] FROM BCD

10 Source D9:3

Destination N7:3

If input word 12, bit 10 is set, convert the value in D9:3 to an integer value and store the result in N7:3.

Degree (DEG)

(Enhanced PLC-5 Processors Only)

Description: 8VH WKH '(* LQVWUXFWLRQ WR FRQYHUW UDGLDQV 6RXUFH](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-250-320.jpg)

![RADIANS TO DEGREE Table 6.E

Source Updating Arithmetic Status Flags for an DEG Instruction

Destination

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 DEG

]

] RADIANS TO DEGREE

10 Source F8:7

0.7853982

Destination F8:8

45

If input word 12, bit 10 is set, convert the value in F8:7 to degrees and store the result on F8:8.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-252-320.jpg)

![DEGREES TO RADIANS Table 6.F

Source Updating Arithmetic Status Flags for an RAD Instruction

Destination

With this Bit: The Processor:

Carry (C) always resets

Overflow (V) sets if overflow generated; otherwise resets

Zero (Z) sets if result is zero; otherwise resets

Sign (S) sets if result is negative; otherwise resets

Example:

I:012 RAD

]

] DEGREES TO RADIANS

10 Source N7:9

45

Destination F8:10

0.7853982

If input word 12, bit 10 is set, convert the value in N7:9 to radians and store the result on F8:10.

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-255-320.jpg)

![7KH PDVN PXVW EH WKH VDPH ZRUG VL]H DV WKH

VRXUFH DQG GHVWLQDWLRQ

:KHQ URXQGLQJ IORDWLQJ SRLQW QXPEHUV GXULQJ D PRYH WR DQ LQWHJHU

ZRUG WKH SURFHVVRU GRHV QRW FRUUHFWO URXQG QXPEHUV OHVV WKDQ ±

)RU PRUH LQIRUPDWLRQ RQ WKH RSHUDQGV DQG YDOLG GDWD WSHVYDOXHV RI

HDFK RSHUDQG](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-258-320.jpg)

![YDOXH LQ WKH FRQWURO VWUXFWXUH SRLQWV WR WKH ZRUG LQ WKH

GDWD EORFN WKDW WKH LQVWUXFWLRQ LV FXUUHQWO XVLQJ 2SHUDWLRQ VWRSV

ZKHQ WKH IXQFWLRQ FRPSOHWHV RU ZKHQ WKH SURFHVVRU GHWHFWV DQ HUURU

7KH IROORZLQJ WLPLQJ GLDJUDP VKRZV WKH UHODWLRQVKLS EHWZHHQ VWDWXV

ELWV DQG LQVWUXFWLRQ RSHUDWLRQ :KHQ WKH LQVWUXFWLRQ H[HFXWLRQ LV

FRPSOHWH WKH GRQH ELW LV WXUQHG RQ 7KH GRQH DQG HQDEOH ELWV DUH QRW

WXUQHG RII DQG WKH SRVLWLRQ YDOXH LV QRW ]HURHG XQWLO WKH UXQJ

FRQGLWLRQV DUH QR ORQJHU WUXH 2QO WKHQ FDQ DQRWKHU RSHUDWLRQ EH

WULJJHUHG E D QRWWUXHWRWUXH WUDQVLWLRQ RI WKH UXQJ FRQGLWLRQV

One

program

scan

Condition of rung that

controls file/block instruction

Enable (bit 15)

Done (bit 13)

The processor turns

off status bits and

zeroes position value.

Execution of the instruction

16640

Operation complete

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-281-320.jpg)

![File Instruction Concepts 8-7

:KHQ WKH LQVWUXFWLRQ H[HFXWLRQ LV FRPSOHWH WKH GRQH ELW LV WXUQHG RQ

,I WKH UXQJ LV WUXH DW FRPSOHWLRQ WKH HQDEOH ELW DQG GRQH ELW DUH QRW

WXUQHG RII XQWLO WKH UXQJ LV QR ORQJHU WUXH :KHQ WKH UXQJ LV QR ORQJHU

WUXH WKHVH ELWV DUH WXUQHG RII DQG WKH SRVLWLRQ YDOXH LV ]HURHG

,I WKH UXQJ LV QRW WUXH DW FRPSOHWLRQ WKH HQDEOH ELW LV WXUQHG RII

LPPHGLDWHO DQG RQH VFDQ DIWHU WKH HQDEOH ELW LV WXUQHG RII WKH GRQH

ELW LV WXUQHG RII DQG WKH SRVLWLRQ YDOXH LV ]HURHG

2QO DIWHU WKH HQDEOH DQG GRQH ELWV DUH WXUQHG RII FDQ DQRWKHU

RSHUDWLRQ EH WULJJHUHG E D QRWWUXHWRWUXH WUDQVLWLRQ RI WKH

UXQJ FRQGLWLRQV

Incremental Mode

,QFUHPHQWDO PRGH PDQLSXODWHV RQH ZRUG RI WKH ILOH HDFK WLPH WKH

UXQJ JRHV IURP QRW WUXH WR WUXH 7SH DQ , IRU WKH PRGH SDUDPHWHU

ZKHQ RX HQWHU WKH LQVWUXFWLRQ

File

Word

File Word

1-Word Operation 1st Rung Enable

Word #0 512

1-Word Operation 2nd Rung Enable

Word #1 513

1-Word Operation 3rd Rung Enable

Word #2 514

Word #3 515

Word File

Word #12 524

1-Word Operation 14th Rung Enable

Word #13 (last word) 525

16

7KH IROORZLQJ WLPLQJ GLDJUDP VKRZV WKH UHODWLRQVKLS EHWZHHQ VWDWXV

ELWV DQG LQVWUXFWLRQ RSHUDWLRQ

One or more

program

scans

Condition of rung that

controls file instruction

Enable (bit 15)

Done (bit 13)

Execution of instruction

The processor The processor turns

turns off enable bit. off status bits and

Operation complete zeroes position value.

16644

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-284-320.jpg)

![8-8 File Instruction Concepts

([HFXWLRQ RFFXUV RQO LQ D SURJUDP VFDQ LQ ZKLFK WKH UXQJ JRHV IURP

QRW WUXH WR WUXH (DFK WLPH WKLV GRHV RFFXU RQO RQH ZRUG RI WKH ILOH LV

RSHUDWHG RQ 7KH HQDEOH ELW LV RQ ZKHQ UXQJ ORJLF LV WUXH 7KH GRQH ELW

LV WXUQHG RQ ZKHQ WKH ODVW ZRUG LQ WKH ILOH KDV EHHQ RSHUDWHG RQ :KHQ

WKH ODVW ZRUG LQ WKH ILOH KDV EHHQ RSHUDWHG RQ DQG WKH UXQJ JRHV IURP

WUXH WR QRW WUXH WKH HQDEOH DQG GRQH ELWV DUH WXUQHG RII DQG WKH

SRVLWLRQ YDOXH LV ]HURHG ,I WKH UXQJ UHPDLQV WUXH IRU PRUH WKDQ RQH

SURJUDP VFDQ WKH ILOH LQVWUXFWLRQ LV QRW H[HFXWHG LQ VXEVHTXHQW VFDQV

DIWHU WKH WUDQVLWLRQ

,PSRUWDQW ,I RX DUH RSHUDWLQJ RQ DQ HQWLUH ILOH DYRLG XVLQJ WKH

UHVXOWV RI D ILOHEORFN LQVWUXFWLRQ XVLQJ LQFUHPHQWDO

PRGH XQWLO WKH GRQH ELW LV RQ WKH GDWD ZLOO

EH LQFRPSOHWH](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-285-320.jpg)

![9-2 File Instructions FAL, FSC, COP, FLL

File Arithmetic and Logic (FAL) 7KH )$/ LQVWUXFWLRQ SHUIRUPV FRS DULWKPHWLF ORJLF DQG IXQFWLRQ

RSHUDWLRQV RQ WKH GDWD VWRUHG LQ ILOHV 7KH )$/ LQVWUXFWLRQ SHUIRUPV

WKH VDPH RSHUDWLRQV DV WKH 37 LQVWUXFWLRQ 7KH GLIIHUHQFH LV WKDW WKH

)$/ LQVWUXFWLRQ SHUIRUPV RSHUDWLRQV RQ PXOWLSOH ZRUGV ZKLOH WKH

37 LQVWUXFWLRQ KDQGOHV VLQJOH ZRUGV

Description: 7KH )$/ LQVWUXFWLRQ LV DQ RXWSXW LQVWUXFWLRQ WKDW SHUIRUPV WKH

FAL RSHUDWLRQV GHILQHG E VRXUFH DGGUHVVHV DQG RSHUDWRUV RX ZULWH

FILE ARITH/LOGICAL EN LQ WKH H[SUHVVLRQ 7KH LQVWUXFWLRQ ZULWHV WKH UHVXOWV LQWR D

Control

Length GHVWLQDWLRQ DGGUHVV

DN

Position

Mode

ER

6HOHFW KRZ WKH SURFHVVRU GLVWULEXWHV WKH RSHUDWLRQ RYHU RQH RU PRUH

Destination

Expression SURJUDP VFDQV E RXU VHOHFWLRQ RI LQVWUXFWLRQ PRGH )RU PRUH

LQIRUPDWLRQ DERXW PRGHV RI ILOH RSHUDWLRQ VHH FKDSWHU

7KH )$/ LQVWUXFWLRQ DXWRPDWLFDOO FRQYHUWV WKH GDWD WSH DW WKH

VRXUFH DGGUHVVHV WR WKH GDWD WSH WKDW RX VSHFLI LQ WKH GHVWLQDWLRQ

DGGUHVV

RX FDQ XVH WKLV LQVWUXFWLRQ WR SHUIRUP RSHUDWLRQV VXFK DV

‡ ]HUR D ILOH

‡ FRS GDWD IURP RQH ILOH WR DQRWKHU

‡ PDNH DULWKPHWLF RU ORJLF FRPSXWDWLRQV RQ GDWD VWRUHG LQ ILOHV

‡ XQORDG D ILOH RI HUURU FRGHV RQH DW D WLPH IRU GLVSOD

$77(17,21 ,QVWUXFWLRQV ZLWK D VLJQ LQ DQ DGGUHVV

PDQLSXODWH WKH RIIVHW YDOXH VWRUHG DW 6 0DNH VXUH

RX PRQLWRU RU ORDG WKH RIIVHW YDOXH RX ZDQW SULRU WR

XVLQJ DQ LQGH[HG DGGUHVV 2WKHUZLVH XQSUHGLFWDEOH

PDFKLQH RSHUDWLRQ FRXOG RFFXU ZLWK SRVVLEOH GDPDJH WR

HTXLSPHQW DQGRU LQMXU WR SHUVRQQHO

1785-6.1 November 1998](https://image.slidesharecdn.com/instructionsetreferencebyallen-bradley-110210050104-phpapp01/85/Instruction-set-reference-by-allen-bradley-289-320.jpg)