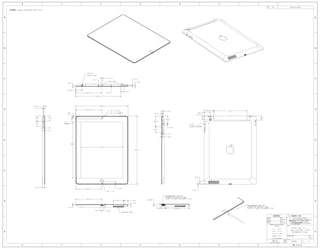

I pad 4 full Schematic Diagram

- 2. 4R7 U5902 R3740 R3750 L8112 L3750 L3740 U3750 U3740 FL3751 FL3750 FL3741 FL3740 J5950 L6111_RF U6102_RF C5934 U3060 J5900 L8105 L8106 L8107 U3600 U8100 D8258 D8228 D3000 D8100 U0600 LED9000 C1421 C1321 L3000 C3001 C3000 J6190_RF J6051 J6050 U5903 U3010 U3009 U3000 U3007 U5900 U1600 L8229 R3009 Y0602 L8104 C8124 L8102 L8109 L8100 L8103 L8101 L8110 Y8138 C8165 C8166 L8111 L8225 L8255 C1401 C1414 C1104 C1420 C1427 C1327 C1192 C1314 C1100 C1105 C1320 C1103 C1101 CA185 C1179 C8194 C1301 C1102 C8154C8155 R5961 R5960 R3744 R3745 R3754 R3755 R3025 R3030 R3031 R3033 R0721 R2205 R0760 R0718 R0717 R0716 R0720 R0715 R0711 R0713 R0714 R3155 R3160 R3742 R3743 R3752 R3753 R3614 R3060 R3173 R3171 R3071 R3070 R3631 R3630 R0708 R0710 R0709 R9000 R3101 R3032 L3620 R8222 R8281 R3751 R3741 R1022 R1420 R10234 R1020 R1021 R9002 R3190 R3066 R3012 C5960 C3756 C3746 C3060 C3110 C3108C3106 C3105 C3103 C3041 C3031 C3030 C5936 C5935 C5932 C5931 C3102 C3050 C1652 C1635 C1634 C1633 C1632 C1631 C1630 C1623 C1620 C1625 C1624 C1622 C1621 C6110_RF C1325 C1426 C1408 C1424 C1411 C1021 C1023C1144C1433 C1407 C1412 C1425 C1413 C1434 C1022 C1333 C1313 C1306 C1312 C1197C1311 C1307 C1326 C1308 C1020 C1334C1324 C1432 C1406 C3767 C3768 C3787 C3788 C3632 C3630 C3631 C3740 C3749 C3750 C3759 C3761 C3764 C3781 C3784 C3763 C3766 C3783 C3786 C3760 C3780 C1318 C3617 C3616 C3754 C3744 C3721 C3711 C3614 C0640 C3620 C3008 C3002 C8142 C8143 C8163 C8164 C1651 C1650 C8131 C3603 C5933 C5930 C3755 C3745 C3720 C3710 C8226 C8256 C8100 C8101 C8102 C8103 C8104 C8105 C8107 C8108 C8109 C8110 C8111 C8112 C8113 C8114 C8117 C8118 C8119C8120 C8121 C8122 C8123 C8195 C8126C8125 C8232 C8233 C8234 C8235 C8262 C8263 C8264 C8265 C8237 J7500 J3700 J2200 R5962 R8297 R8296 R6108_RF R6114_RF R5934 R5929 R0652 R5931 R5930 R1220 R5990 R6105_RF R6107_RF R6109_RF R6111_RF R6113_RF R1200 R1201 R1202 R1208 R1209 R1206 R1205 R1204 R1203 R5991 R0622 R0621R0620 R0608 R0730 R0700 R6112_RF R0650 R5935 R0651 R3611 R3610 R3613 R3612 R1455 R1456 R1095 R1096 R1083 R1084 R1453R1454 R1356 R1056 R1055 R1354 R1353 R1054 R1053 R1355 R0642 R0640 R0643 R0703 R0704 R3640 R0701 R0702 R3620 R5933 R5932 R3181 R3180 C3601 C3605 C3606 C3607 C3608 C3610 C3758 C3757 C3748 C3747 C6109 C3104 C8148 C3107 C8152 C3753 C3752 C3751 C3743 C3742 C3741 C8144 J5400 J5401 J3011J3010 C5991 C5944 C5943 C5942 C5941 C5940 C3691 C6103_RF C1422 C1456 C1463 C1095 C1096 C1430C1404 C1405 C1084 C1085 C1454C1462 C1363 C1330 C1304 C1056 C1058 C1054 C1362 C1354 C1331C1057 C1305 C1356 C1322 C8292 C1431 C3723 C3722 C3713 C3712 C6102_RF C6104_RF C1423 C1435 C1419 C1309 C1335 C1323 C1319 C1409 C0651 C0650 C3602 C3615 C1610 C1611 C1613 C1614 C1615 C6101_RF C1612 C3192 C3191 C3009 C3053 C3007 C3005 C3070 C1302 C1402 C1403 C1303 C3618 C8147 C8149 C3112 C3101 C8146 C8201 C8251 C8266 C8267 C5783 U5650 U5640 U5610 U5630 U5620 U5600 U5670 U5660 L2210 L2200 L2201 L5520 L5530 L2242 L5930 C8217 C8281 C8282 C8215 C8220 C8221 C8223 C8214 C2281C2282C2283C2285C2287 C2284C2286 C2280 C0632 C0633 C0634 C1141 C1177 C1154 C1178 C1153 C1137 C1140 C1165 C1166 C1139 C1138 C1136 C3770 C3771 C3773 C3772 C2241 R0921 R0920 R2285R2286R2287 R2280R2281R2282R2283R2284 R0843 R0842 R1691 R1690 R9030 R9020 R1305 R1306 R1351 R1452 R1451 R1405 R1406R1352 R9021 R9031 L5570 L5560 L5580 R5630 R5641 R5640 R5631 C0961 C0960 C1122C1120 C1126 C1184 C1185 C1123 C1121 C1152 C1151 C1119 C1195 C1125 C1196 C1124 C6 11 1_ RF C6107_RF C6108_RF C6 19 0_ RF C6 19 2_ RF C6191_RF L5701 L5700 L6192_RF L6191_RF L6190_RF R8173 R8203 R8130 R8116 R3601 R0610 R0950 R0613 R1654 FL7500 FL0910 FL5750 FL5710 FL5740 R8290 R8291 R2290 R8170 U1400U1300 C8236 C7527 C7526 C2270C2220 C2253C2233 C2271C2221 Q8200Q8201Q8203Q8202 C0933 C0934 C0932 C8172 C8196 R8100 R8219 Q8123 Q8104 U3101FL5990 CA199 DZ5791 DZ5792 DZ5750 DZ5710 DZ5740 DZ5760 L5757 D8230 DZ8120 DZ5900 DZ5901 DZ5902 DZ5903 DZ5990 L2212L2222L2232L2202 U2200 Q9010 Q9030 Q9020 C8239 C8238 C5581 C5551 C5561 C5571 C5731 U6101_RF J6191_RF U6104_RF J6000 U3003 U3100 D5990 L5540 L5500 L5510 L5931 C8153 C8145 C8151 C8209 C8136 C8135 C8139 C8140 C8141 C1113 C1115 C1316 C0614 C1116 CA195 C0980 CA198 C1118 C1117 C1417 C0935 C1114 C2202 C8134 C1328C1329 C1416C1428C1429 C1317 C8173 C8174 C8170 C8171 C3111 CA193 C1601 C1602 C1600 CA197 CA196 C0843 C0842 C1690 C1691 C0810 C0811 C0812 C0820 C0821 C0951 C0927 C0613 C0606 C0605 C0931 C0930 C1145 C0924 C0982 C8206 C8207 C1352 C0953 C0957 C0952 C0950 C0981 C0631 C0608 C0630 C1450 C0609 C0635 C1452 C1461 C1350 C1360 C1460 C1361 C3690 C5990 C0612 C0607 C0928 C0929 C0904 C11A0 C11A1 C11B0 C11B1 C11C0 C11C1 C11D0 C11D1 C11E0 C11E1 C0636 C11F0 C0637 C0621 C0623 C5920 C5910 C5900 C5722 C8130 C8162C8161C8160C8159C8158 C8157 C8156 C8187 C8188C8189C8190C8191C8192C8193 C3609 C8167 C8133 C8132 C8168 C3612 R1210 R1211 R0932 R0930 R0931R0933 R0706R0705 R2242 R2241R2240 R1260 R0831 R0832 R1655 R0941 R0942 R1207 R0604 R0900 R0940 C3611 C8138 C1150 C1182 C1171 C1172 C1169 C1170 C1149 C1183 C1157 C1160 C1158 C1159 C1193 C1194 C1176 C1175 C1174 C1173 C1164 C1163 C1162 C1161 C0910 C2232 C5553 C5563 C5573 C5584C5733 C2230 C7525 C5570 C5560 C5550C5580C5730 C7522 C7523 C5552 C5630 C5640 C7524 C5572 C5562 C2206 C5583 C5661 C5670C5671 C5660 C5732 C3604 C3613 C8291 C8290 C8137 C1418 C8169 C8210 CA186 C1198 C1133 CA187 CA188 C1199 CA190 C1605 CA192 C1606 C1604 C1130 C1135 C1131 C1132 C1134 CA191 CA189 CA150 CA151 CA152 CA153 C1143 C1129 C1142 C1410 C1128 C1310 C1332 C5721 C5750 C5765 C5766 C5711 C5710 C1607 C1608 C1609 C5740 C5741 C8212 C8204 C3006 C3109 C0956 C0909 C0907 C2239 C2246 C2247 C2240 C2248 C2249 C5582 C2250 C2251 C2242 C2243 C2203 C2244 C2245 C0903 C0908 C0955 R8231 R8240 R8232 R8261 R8227 R8239 R8265 R8270 R8262 R8269 R8235 R8257 R1321 R1421 R1320 R8282 R8216 R8218 R8280 FL0911 L5550 L5730 R9001 R8292 R8172 R3120 R8293 R0911 R8196 R5790 R3107 R9010 R9011 R0719 C1147C1148 C1167 C1168 C1156 C1106 CA194 C1180 C1155 C1181 C1108C1109 C1111 C1415C1190 C1110 C1107C1191C1315 820-3249-BOT MLB 820-3249-TOP MLB www.witesomtesla.comwww.mobile-files.com

- 3. TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_HEAD DRAWING TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_ITEM 2. ALL CAPACITANCE VALUES ARE IN MICROFARADS. PROPRIETARY PROPERTY OF APPLE INC. 3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ. DESCRIPTION OF REVISION CK APPD 2 1 1245678 B D 6 5 4 3 C A NOTICE OF PROPRIETARY PROPERTY: PAGE THE INFORMATION CONTAINED HEREIN IS THE C A D DATE R SHEET Apple Inc. THE POSESSOR AGREES TO THE FOLLOWING: DRAWING TITLE D SIZE REVISION DRAWING NUMBER BRANCH REV ECN 7 B 3 II NOT TO REPRODUCE OR COPY IT I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE IV ALL RIGHTS RESERVED III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART 1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%. 8 (JOE) (TERRY) (JOE) (TERRY) (TERRY) (AMANDA) (TERRY) (TERRY) (AMANDA) (AMANDA) (TERRY) (AMANDA) (TERRY) (TERRY) (TERRY) (TERRY) (AMANDA) (AMANDA) (AMANDA) (SYSTEM DRI) (SYSTEM DRI) (MATT) (JOE) (JOE) (MARK) (AMANDA) (MARK) (MARK) (MADHAVI) (MADHAVI) (MADHAVI) (AMANDA) (AMANDA) (AMANDA) (AMANDA) (AMANDA) (AMANDA) (MADHAVI) (AMANDA) (MADHAVI) (AMANDA) X140 MLB 1 OF 39 2012-07-26PRODUCTION RELEASED 1 OF 154 A.0.0 051-9385 A 0001554595 LAST_MODIFIED=Thu Jul 26 10:29:36 2012 NAND16 N/A13 N/A DDR 2 AND 314 N/A12 N/A 13 N/A11 N/ADDR 0 AND 1 12 N/AN/AAP: MISC & ALIASES10 BOM TABLES4 N/AN/A3 31 PMU: ADRIANA PAGE 3 MADHAVI 12/06/201183 AP: NAND8 N/A6 N/A CONTENTSPDF DATESYNC MASTERCSA MLB DRAWING DEBUG/MISC.32 MLB 11/09/201190 33 N/A N/A93 TEST/HOLES/FIDUCUALS 34 POWER ALIASES N/A N/A121 35 CONSTRAINTS: MLB RULES MIKE 11/30/2011150 7 AP: I/Os N/A5 N/A 7 AP: TV,DP,MIPI9 N/AN/A 10 N/A8 N/AAP: DDR AP: POWER11 N/A9 N/A ALIASES21 N/A14 N/A VIDEO: EDP CONNECTOR22 N/A15 N/A GRAPE: GROUNDHOG,CONN,BOOST30 N/A16 N/A GRAPE: Z1, Z231 N/A17 N/A AUDIO: L81 CODEC36 N/A18 N/A AUDIO: SPEAKER AMP37 N/A19 N/A SENSOR FLEX CONN54 N/A20 N/A SENSOR CONN FILTERS 155 N/A21 N/A SENSOR CONN FILTERS 256 N/A22 N/A E75 DOCK SUPPORT57 N/A23 N/A IO FLEX CONN58 N/A24 N/A TRISTAR59 N/A25 N/A CONNECTOR: CELLULAR60 N/A26 N/A 61 N/A27 N/AWIFI/BT 75 12/06/201128 MADHAVIPOWER: BATTERY CONNECTOR 82 12/06/201130 MADHAVIPMU: ADRIANA PAGE 2 154 11/30/2011MIKE39 CONSTRAINTS: POWER / GND CONSTRAINTS: DDR/FMI38 MIKE 11/30/2011153 AP: MAIN6 N/A4 N/A BLOCK DIAGRAM: SYSTEM2 N/A2 N/A MIKE152 CONSTRAINTS: DISPLAY/AUDIO37 11/30/2011 PMU: ADRIANA PAGE 181 12/06/201129 MADHAVI 36 CONSTRAINTS: LOW SPEED BUS MIKE 11/30/2011151 CONTENTSCSAPDF DATESYNC MASTER Table of Contents1 N/A1 N/A iPad 4th Gen

- 4. Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT XSP HP AMP AMP SPEAKER MIC2MIC1 L81 MBUS AUDIO CODEC ASP SPI1 SPI NCI2S4 I2S1 BATTERY I2S0 I2S3 SPI3 GROUNDHOG CSA 61 GPS CELLULAR/ GYRO SENSOR BOARD VGA FLEXSENSOR BOARD ACCELEROMETER ALS FF CAMERA VGA FLEX REAR CAMERA VA5 FLEX I2S2 LPDDR2 PROX SENSOR SENSOR BOARD COMPASS SENSOR BOARD ISP_I2C1 MIPI1C ISP_I2C0 DISPLAY/ USART SIM CARD CSA 31 CSA 13-14 NOT ON HSIC1 TRISTAR MIPI0C EDP DWI UART5 CSA 31 CSA 30 CSA 75 CSA 36 I2C2 I2C1 BACKLIGHT Z2 Z1 TOUCH PANEL I2C0 FMI0 FMI1 CSA 16 HSIC1_1 BT_I2S UART3 WIFI/BT BALI WIFI-ONLY CONFIG UART2 UART4 HSIC3 DIVERSITY CELLULAR ANT GPS ANT WIFI/BT ANT IPC CSA 59 USB2.0 UART1 UART6 NAND FLASH USART CSA 60 PRIMARY CELLULAR ANT PMU ADRIANA CSA 81,82 BUTTON FLEX HOME BUTTON HALL EFF 1 HALL EFF 2 USB11 BLOCK DIAGRAM: SYSTEM SYNC_MASTER=N/A SYNC_DATE=N/A 051-9385 A.0.0 2 OF 154 2 OF 39

- 5. CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM TABLE_5_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM TABLE_5_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) PART NUMBER ALTERNATE FORPART NUMBER BOM OPTION REF DES COMMENTS: TABLE_ALT_HEAD TABLE_ALT_ITEM TABLE_ALT_ITEM TABLE_5_ITEM BOM OPTIONSBOM GROUP TABLE_BOMGROUP_HEAD TABLE_BOMGROUP_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT TABLE_5_ITEM CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) CRITICAL BOM OPTION TABLE_5_HEAD PART# DESCRIPTIONQTY REFERENCE DESIGNATOR(S) TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM TABLE_5_ITEM MLB_E: LEGACY CELLULAR CONFIG MLB_D: LEGACY CELLULAR CONFIG MLB_C: CELLULAR CONFIG MLB_B: CELLULAR CONFIG MLB_A: WIFI ONLY CONFIG MLB: MLB BOARD ONLY DEV: DEV BOARD ONLY 64GB_PROD: 64 GB CONFIG 32GB_PROD: 32GB CONFIG 16GB_PROD: 16GB CONFIG BOM OPTIONS Power aliases required by this page: BOM options provided by this page: SCH AND BOARD P/N Page Notes BARCODE LABEL/EEEE CODES SOC/PMU MECHANICAL PARTS NAND 32GB FLASH CONFIGURATIONS NAND SDRAM PMU SOC Signal aliases required by this page: (NONE) (NONE) COMMON ALTERNATE AUDIO GRAPE MEMORY 16GB FLASH CONFIGURATIONS 64GB FLASH CONFIGURATIONS 128GB FLASH CONFIGURATIONS EEEE_MLB_C_64GEEEE_F1W91 CRITICALEEEE FOR 639-3743 (MLB C 64G)825-7838 EEEE_MLB_C_32GEEEE_F1WF CRITICAL1 EEEE FOR 639-3742 (MLB C 32G)825-7838 1 CRITICAL825-7838 EEEE_F80REEEE FOR 639-4178 (MLB C 128G) EEEE_MLB_C_128G EEEE_MLB_C_16GEEEE_F1WG CRITICAL1 EEEE FOR 639-3741 (MLB C 16G)825-7838 825-7838 1 EEEE FOR 639-3263 (MLB B 16G) CRITICALEEEE_DWKG EEEE_MLB_B_16G 825-7838 EEEE FOR 639-3740 (MLB B 64G)1 CRITICALEEEE_F1WC EEEE_MLB_B_64G 825-7838 1 EEEE FOR 639-3739 (MLB B 32G) CRITICALEEEE_F1W7 EEEE_MLB_B_32G 825-7838 1 CRITICALEEEE_F80PEEEE FOR 639-4177 (MLB B 128G) EEEE_MLB_B_128G 825-7838 1 CRITICALEEEE FOR 639-4176 (MLB A 128G) EEEE_F80Q EEEE_MLB_A_128G EEEE_MLB_A_64GEEEE_F1W8 CRITICAL1 EEEE FOR 639-3738 (MLB A 64G)825-7838 U16001 CRITICALTOSHIBA PPN1.5 128GB 128GB_PROD335S0912 CRITICAL1 U1600 64GB_PROD335S0880 TOSHIBA PPN1.5 64GB BOM TABLES SYNC_DATE=N/ASYNC_MASTER=N/A TOSHIBA PPN1.5 16GB335S0878 16GB_PRODU1600 CRITICAL1 BASIC COMMON,ALTERNATE CRITICAL1 U8100343S0622 IC,PMU,ADRIANA,D2018A1,FCBGA LPDDR2,533MHZ,ELPIDA,38NMU1400,U1400333S0638 333S0636 LPDDR2,533MHZ,HYNIX,38NM333S0637 U1300,U1400333S0636 CRITICAL2 U1300,U1400333S0636 LPDDR2,533MHZ,512MB,SAMSUNG,35NM 335S0879 TOSHIBA PPN1.5 32GB1 U1600 32GB_PRODCRITICAL U0600IC,SOC,H5G,FCBGA1089,0.5MM1343S0598 CRITICAL 1 CRITICALSCH,MLB,X140 SCH1051-9385 FENCE,NAND,TOP,MLB,X140806-4195 PD_FENCE_NAND1 CRITICAL FENCE,AMP,MLB,X140 CRITICAL806-3956 PD_FENCE_AMP1 FENCE,2,BTM,MLB,X1401806-3492 PD_FENCE_BTM2 CRITICAL FENCE,LARGE,TOP,MLB,X140806-3493 PD_FENCE_LARGE1 CRITICAL FENCE,1,BTM,MLB,X140806-4196 CRITICAL1 PD_FENCE_BTM1 825-7838 EEEE FOR 639-3737 (MLB A 32G)1 CRITICAL EEEE_MLB_A_32GEEEE_F1WH 825-7838 EEEE FOR 639-3736 (MLB A 16G)1 CRITICAL EEEE_MLB_A_16GEEEE_F1WD 1 CRITICAL820-3249 PCBF,MLB,X140 PCB1 051-9385 A.0.0 4 OF 154 3 OF 39

- 6. IN OUT IN IN OUT OUT IN VDD_ANA_PLL JTAG_TRST* CFSB CPU0_SWITCH CPU1_SWITCH DDR0_CKEIN DDR1_CKEIN DDR2_CKEIN DDR3_CKEIN FAST_SCAN_CLK FUSE1_FSRC HOLD_RESET HSIC_VDD121 HSIC_VDD122 HSIC_VDD123 HSIC_VSS121 HSIC_VSS122 HSIC_VSS123 HSIC1_DATA HSIC1_STB HSIC2_DATA HSIC2_DVDD102 HSIC2_DVSS HSIC2_STB HSIC3_DATA HSIC3_DVDD103 HSIC3_DVSS HSIC3_STB JTAG_SEL JTAG_TCK JTAG_TDI JTAG_TDO JTAG_TMS JTAG_TRTCK RESET* TESTMODE TST_CLKOUT TST_STPCLK USB_ANALOGTEST USB_ASW_VDD18 USB_ASW_VSS18 USB_BRICKID USB_BRICKID_DM_MON USB_DM USB_DP USB_DVDD USB_ID USB_REXT USB_VBUS USB_VDD330 USB_VSSA0 USB11_DM USB11_DP WDOG XI0 XO0 SYM 1 OF 12 SYM 11 OF 12 VSSVSS BI BI BI BI BI BI OUT OUT BI BI PP Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT TRISTAR NEEDED IF WE GO TO 9600 NEW TO BALI <1MA 30MA BB 8MA BCM4330 CHANGE TO USB 3.3V TO AVOID FAILURE IN CHARGE DETECT CIRCUIT AT 3.0V-5% MLB OPTION USED FOR FF PER PIN PER PIN 2.7MA 11.9MA CPU_VDD CONTROL ISSUE FOUND IN H5P: WLAN 5.4MA USB 1.1 BASEBAND/TRISTAR MDM9615NOSTUFF 010051/32W 5% MF 100K 01005 1/32W 1% MF 100K 25263039 01005 1/32W 5% MF 7.5K 16V 10% 1000PF 0201 X7R-CERM 01005 1/32W 1% MF 221K 25 MLB 01005 1/32W 0% MF 0.00 CRITICAL 01005 16V 5% CERM 22PF CRITICAL SM-2 24.000MHZ-16PF-60PPM CRITICAL 01005 16V 5% CERM 22PF01005 1/32W 5% MF 22 01005 1/32W 1% MF 1.00M 201 1% MF 68.1K 1/20W 201 1% 1/20W MF 43.2 01005 10% 6.3V 0.01UF X5R 01005 20% 6.3V 0.1UF X5R-CERM 01005 0.1UF 20% 6.3V X5R-CERM 01005 20% X5R-CERM 6.3V 0.1UF 01005 10% 6.3V X5R 0.01UF 01005 10% 6.3V X5R 0.01UF NP0-C0G-CERM 16V +/-0.5PF 8.2PF 01005 01005 1/32W 0% MF 0.00 01005 10% 6.3V X5R 0.01UF 10% 6.3V 402 CERM 1UF +/-0.5PF 8.2PF 01005 NP0-C0G-CERM 16V 01005 10% 6.3V X5R 0.01UF 01005 X5R 0.1UF 20% 4V 10 103639 010051/32W 5% 100K 1/32W 01005 5% 100K 010051/32W 5% 100K 10 10 10 OMIT_TABLE BALI-H5G BGA OMIT_TABLE BGA BALI-H5G 2636 2636 1436 1436 25 36 25 36 30 30 NP0-C0G-CERM +/-0.5PF 8.2PF 16V 01005 01005 X5R 0.1UF 20% 4V 01005 X5R 0.1UF 20% 4V +/-0.5PF 8.2PF 01005 NP0-C0G-CERM 16V +/-0.5PF 8.2PF 01005 NP0-C0G-CERM 16V +/-0.5PF 8.2PF 01005 NP0-C0G-CERM 16V 25 36 25 36 P4MMSM AP: MAIN SYNC_MASTER=N/A SYNC_DATE=N/A USB11_AP_BBMUX_N USB11_AP_BBMUX_P CPU1_SWITCH CPU0_SWITCH USB_AP_N USB_AP_P HSIC1_WLAN_STB HSIC1_WLAN_DATA HSIC3_BB_STB HSIC3_BB_DATA AP_HOLD_RESET AP_FAST_SCAN_CLK AP_TST_STPCLK JTAG_AP_TRST_L AP_TESTMODE AP_WDOG_RESET_IN RST_AP_L =PP1V8_H5 JTAG_AP_TCK =PP1V8_PLL_H5 TP_JTAG_AP_TDO AP_WDOG =PP1V2_HSIC_H5 PP1V8_PL0_F NET_SPACING_TYPE=PWR MAX_NECK_LENGTH=3MM MIN_LINE_WIDTH=0.2MM VOLTAGE=1.8V MIN_NECK_WIDTH=0.1MM JTAG_AP_SEL JTAG_AP_TMS JTAG_AP_TDI NC_HSIC2_DATANO_TEST=TRUE NO_TEST=TRUE NC_HSIC2_STB =PP1V8_H5 =PP1V8_H5 NC_USB_IDNO_TEST=TRUE AP_DDR1_CKEIN_1V2 NC_USB_BRICKIDNO_TEST=TRUE NC_USB_BRICKID_DM_MONNO_TEST=TRUE PPVBUS_USB NC_USB_ANALOGTESTNO_TEST=TRUE AP_24M_O USB_REXT0 USB_AP_VBUS0 XTAL_AP_24M_I NC_JTAG_AP_TRTCKNO_TEST=TRUE =PP1V0_USB_H5 =PP1V8_VDDIO18_H5 =PP3V3_USB_H5 XTAL_AP_24M_O =PP1V0_HSIC_H5 TP_AP_TST_CLKOUT R0608 1 2 R06421 2 R06401 2 C06401 2 R06431 2 R0652 1 2 C06511 2 Y0602 2 4 1 3 C06501 2 R0651 1 2 R06501 2 R06101 2 R06131 2 C06351 2 C06341 2 C06331 2 C06321 2 C06311 2 C06301 2 C06071 2 R0604 1 2 C06091 2 C06141 2 C06121 2 C06081 2 C06131 2 R0620 1 2 R0621 1 2 R0622 1 2 U0600 A18 N32 N24 L6 F9 AG10 AD5 N27 L31 G16 R33 T33 R31 T28 T25 T31 AN17 AF18 AG19 AM17 R27 R26 AF19 R28 T29 AG18 H17 J17 F16 H16 F17 K16 J16 G17 D18 C19 A19 D32 E32 R25 N26 P32 P31 P29 N33 M33 R30 P27 T30 P28 P26 R29 U18 C18 J33 K33 U0600 A1 A2 B2 N21 N23 P1 P8 P10 P12 P14 P16 P18 P20 B4 P22 P30 P33 R2 R6 R9 R11 R13 R15 R17 B9 R19 R21 R23 R32 T5 T6 T8 T10 T12 T14 B12 T16 T22 T24 T32 U1 U2 U4 U9 U11 U13 B15 U15 U17 U21 U23 U33 V8 V10 V12 V14 V16 B32 V19 V21 V23 V30 W3 W9 W11 W13 W15 W17 B33 W20 W22 W24 Y1 Y10 Y12 Y14 Y16 Y18 Y19 C7 Y21 Y23 Y25 Y28 Y32 AA2 AA9 AA11 AA13 AA15 C10 AA17 AA20 AA22 AA24 C13 C33 C16 A3 D3 D5 D8 D11 D14 D17 U19 E10 F1 E22 E24 E25 F2 F5 F22 F24 F25 F30 A31 A11 G3 G18 G21 G22 G26 V18 H4 H9 H10 H11 A14 H12 H13 H14 H21 H22 H28 H33 J2 J9 J11 A17 J13 J15 J21 T18 K3 K8 K10 K12 K14 K22 A32 K26 K30 L1 L4 L9 L11 L13 L15 L17 L19 A33 L21 L33 M2 M3 M8 M10 M12 M14 M16 M18 B1 M20 M22 M28 N3 N9 N11 N13 N15 N17 N19 C06361 2 C06061 2 C06051 2 C06371 2 C06211 2 C06231 2 PP0600 1 6 OF 154 051-9385 A.0.0 4 OF 39 4571034 2536 34 36 34 39 10 2536 36 4571034 4571034 29 36 36 34 6 7 9 34 34 36 34

- 7. OUT OUT IN OUT OUT OUT IN OUT OUT IN OUT OUT OUT IN IN IN OUT BI OUT BI OUT BI OUT OUT IN OUT OUT IN IN IN OUT IN IN IN OUT IN IN OUT IN IN IN IN IN IN OUT IN OUT IN OUT IN OUT IN OUT IN OUT IN OUT OUT OUT IN IN OUT IN IN IN SWI_DATA SPI3_SSIN SPI3_SCLK SPI3_MOSI SPI3_MISO SPI2_SSIN SPI2_SCLK SPI2_MOSI SPI2_MISO SPI1_SSIN SPI1_SCLK SPI1_MOSI SPI1_MISO SPI0_SSIN SPI0_SCLK SPI0_MOSI SPI0_MISO SPDIF I2S4_MCK I2S4_LRCK I2S4_DOUT I2S4_DIN I2S4_BCLK I2S3_MCK I2S3_LRCK I2S3_DOUT I2S3_DIN I2S3_BCLK I2S2_MCK I2S2_LRCK I2S2_DIN I2S2_BCLK I2S1_MCK I2S1_LRCK I2S1_DOUT I2S1_DIN I2S1_BCLK I2S0_MCK I2S0_LRCK I2S0_DOUT I2S0_DIN I2S0_BCLK I2C2_SDA I2C2_SCL I2C1_SDA I2C1_SCL I2C0_SDA I2C0_SCL DWI_DO DWI_DI DWI_CLK I2S2_DOUT SYM 3 OF 12 UART6_TXD UART6_RXD UART6_RTSN UART6_CTSN UART5_TXD UART5_RXD UART4_TXD UART4_RXD UART4_RTSN UART4_CTSN UART3_TXD UART3_RXD UART3_RTSN UART3_CTSN UART2_TXD UART2_RXD UART2_RTSN UART2_CTSN UART1_TXD UART1_RXD UART1_RTSN UART1_CTSN UART0_TXD UART0_RXD TMR32_PWM2 TMR32_PWM1 TMR32_PWM0 GPIO9 GPIO8 GPIO7 GPIO6 GPIO5 GPIO4 GPIO39 GPIO38 GPIO37 GPIO36 GPIO35 GPIO34 GPIO33 GPIO32 GPIO31 GPIO30 GPIO3 GPIO29 GPIO28 GPIO27 GPIO26 GPIO25 GPIO24 GPIO23 GPIO22 GPIO21 GPIO20 GPIO2 GPIO19 GPIO18 GPIO17 GPIO16 GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO1 GPIO0 GPIO_VSEL25_SPI3 GPIO_VSEL25_I2C2 GPIO_SVSEL25_FMI GPIO_SVSEL18_FMI GPIO_3V1 GPIO_3V0 EHCI_PORT_PWR3 EHCI_PORT_PWR2 EHCI_PORT_PWR1 EHCI_PORT_PWR0 GPIO10 SYM 2 OF 12 IN IN OUT IN IN IN IN IN OUT IN OUT IN IN OUT OUT OUT IN OUT OUT OUT IN IN IN IN OUT OUT IN OUT IN OUT OUT IN IN OUT OUT OUT OUT IN OUT IN Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT OS CURRENTLY SUPPORTS USB1.1 FOR DEBUG. TO SENSOR BOARD: 3.0V 1.8V WIFI DEBUG 1.8V TO TRISTAR MDM9600 TO TRISTAR AND SIZE THESE RESISTORS NEED TO CHARACTERIZE RISE TIME AD7149 PROX 0101100X TO SENSOR BOARD: NOT USED 1.8V BT L81 CODEC XSP 1.8V 1.8V IO AND SW UPDATE TO BB GRAPE VSEL25_SPI3 HIGH => SPI3 3.0V VSEL25_I2C2 HIGH => I2C2 3.0V VSEL18_FMI AND VSEL25_FMI LOW => FMI CHANNEL AT 1.8V TO BT UART BCM4330 AP3GDL8 GYRO 1101000X CT809 ALS 0111001X TO: TRISTAR 0011010X TO BB UART 1.8V 1.8V AKM8975B COMPASS 0001110X L81 CODEC ASP ADRIANA PMU 0111100X L19 LEFT 1000000X L19 RIGHT 1000001X I2C PULL-UPSBUTTON PULLUPS L19 AMPLIFIERS USED FOR DEBUG LIS331DLH ACCEL 0011001X MF 220K 5% 1/20W 201 5% 1/20W 220K MF 201 220K MF 201 1/20W 5% NOSTUFF 100K MF 201 5% 1/20W NOSTUFF 1/20W 5% 201 MF 100K100K MF 201 5% 1/20W 100K MF 201 5% 1/20W 1/32W 01005 MF 33.2 1% 1436 1436 1436 1436 1836 1836 1836 1836 1836 1836 1836 1836 1836 10 10 10 100K MF 201 5% 1/20W 2636 5 19 25 30 36 5 19 25 30 36 5 22 36 5 22 36 5 22 36 5 22 36 30 36 30 36 30 36 14 22 26 26 526 2636 20 26 530 10 532 5 10 10 10 10 10 25 36 25 36 26 36 26 36 25 26 36 25 26 36 14 36 14 36 14 36 14 36 14 36 14 36 25 36 25 36 2639 28 30 20 22 51436 30 18 52030 OMIT_TABLE BALI-H5G BGA OMIT_TABLE BALI-H5G BGA 19 26 26 26 MF 01005 1/32W 5% 1.00K1.00K MF 01005 5% 1/32W 1.00K MF 01005 5% 1/32W 1.00K MF 01005 5% 1/32W 2.2K MF 01005 5% 1/32W 2.2K MF 01005 5% 1/32W 1436 2636 52330 52030 519 22 26 10 100K MF 201 5% 1/20W 1636 1636 1636 1636 1836 1836 1836 1836 100K MF 201 5% 1/20W 100K MF 201 5% 1/20W 22 22 22 2530 16 16 516 15 14 NOSTUFF MF 201 5% 1/20W 100K 33.2 MF 01005 1% 1/32W 19 26 19 19 26 519 19 19 19 19 100K MF 201 5% 1/20W 1/20W 5% 201 MF 100K 10 SYNC_MASTER=N/A SYNC_DATE=N/A AP: I/Os I2S2_BT_BCLK I2S2_BT_LRCK I2S2_BT_DIN I2S2_BT_DOUT I2S3_CODEC_XSP_BCLK I2S3_CODEC_XSP_LRCK I2S3_CODEC_XSP_DIN I2S0_CODEC_ASP_BCLK I2S0_CODEC_ASP_LRCK I2S0_CODEC_ASP_DIN I2S0_CODEC_ASP_DOUT I2S0_CODEC_ASP_MCK_R I2S3_CODEC_XSP_DOUT GPIO_BOARD_ID_2 GPIO_BOARD_ID_0 GPIO_BOARD_ID_1 GPIO_BB_HSIC_HOST_RDY I2C0_SCL_1V8 I2C0_SDA_1V8 I2C1_SDA_1V8 I2C2_SCL_3V0 I2C2_SDA_3V0 DWI_AP_CLK DWI_AP_DI DWI_AP_DO GPIO_BT_WAKE GPIO_ALS_IRQ_L GPIO_AP_MODEM_WAKE GPIO_BB_RESET_DET_L GPIO_BB_RADIO_ON_L GPIO_BB_HSIC_RESUME GPIO_PMU_KEEPACT GPIO_BOOT_CONFIG_1 GPIO_FORCE_DFU GPIO_DFU_STATUS GPIO_BOOT_CONFIG_2 GPIO_BOOT_CONFIG_3 GPIO_BRD_REV0 GPIO_BRD_REV1 GPIO_BRD_REV2 UART6_AP_RXD UART6_AP_TXD UART1_BB_CTS_L UART1_BB_RTS_L UART1_BB_RXD UART1_BB_TXD UART3_BT_CTS_L UART3_BT_RTS_L UART3_BT_RXD UART3_BT_TXD UART4_WLAN_RXD UART4_WLAN_TXD UART2_TS_ACC_RXD UART2_TS_ACC_TXD GPIO_BB_RST_L UART5_BATTERY_TRXD GPIO_BTN_VOL_UP_L GPIO_WLAN_HSIC_HOST_RDY GPIO_PMU_IRQ_L GPIO_CODEC_IRQ_L GPIO_BTN_SRL_L SPK_ID BB_JTAG_TRST_RF_L BB_JTAG_TDI_RF BB_JTAG_TDO_RF GPIO_WLAN_HSIC_DEV_RDY GPIO_BB_HSIC_DEV_RDY GPIO_BTN_HOME_L GPIO_BTN_ONOFF_L GPIO_SPKAMP_RST_L GPIO_PROX_IRQ_L GPIO_BB_GPS_SYNC GPIO_BOOT_CONFIG_0 SPI3_GRAPE_MISO SPI3_GRAPE_MOSI SPI3_GRAPE_SCLK SPI3_GRAPE_CS_L SPI1_CODEC_MISO SPI1_CODEC_MOSI SPI1_CODEC_SCLK SPI1_CODEC_CS_L GPIO_GYRO_IRQ1 GPIO_GYRO_IRQ2 GPIO_ACCEL_IRQ1_L PMU_GPIO_TS_INT GPIO_GRAPE_FW_DNLD_EN_L GPIO_GRAPE_RST_L GPIO_GRAPE_IRQ_L PM_LCDVDD_PWREN GPIO_WL_HSIC_RESUME I2S1_SPKAMP_MCK_R BB_JTAG_TMS_RF GPIO_SPKAMP_RIGHT_IRQ_L GPIO_SPKAMP_LEFT_IRQ_L BB_JTAG_TCK_RF GPIO_SPKAMP_KEEPALIVE I2S1_SPKAMP_BCLK I2S1_SPKAMP_LRCK I2S1_SPKAMP_DIN I2S1_SPKAMP_DOUT GPIO_BTN_VOL_DOWN_L GPIO_ACCEL_IRQ2_L GPIO_BB_GSM_TXBURST GPIO_BOARD_ID_3 =PP1V8_S2R_MISC =PP1V8_ALWAYS GPIO_BTN_ONOFF_L NC_UART0_RXDNO_TEST=TRUE NC_TMR32_PWM2_APNO_TEST=TRUE NC_UART2_RTSNNO_TEST=TRUE NC_UART6_RTSNNO_TEST=TRUE NC_UART6_CTSNNO_TEST=TRUE NC_UART5_TXDNO_TEST=TRUE NC_EHCI_PORT_PWR3_APNO_TEST=TRUE NC_UART4_CTS_L NO_TEST=TRUE NC_UART0_TXD NO_TEST=TRUE I2C2_SCL_3V0 I2C1_SCL_1V8 I2C1_SDA_1V8 I2C2_SDA_3V0 I2C0_SCL_1V8 PP3V0_SENSOR_FLT NC_SWI_APNO_TEST=TRUE NC_I2S4_MCK NO_TEST=TRUE NC_I2S4_LRCK NO_TEST=TRUE NC_I2S4_DIN NO_TEST=TRUE NC_I2S4_BCLK NO_TEST=TRUE GPIO_VSEL25_SPI3 GPIO_VSEL25_I2C2 =PP1V8_H5 GPIO_GRAPE_IRQ_L I2C0_SDA_1V8 =PP1V8_H5 =PP1V8_H5 I2S1_SPKAMP_MCK NC_I2S2_MCK NO_TEST=TRUE NC_I2S3_MCK NO_TEST=TRUE TP_SPI0_SSIN I2S0_CODEC_ASP_MCK GPIO_BTN_SRL_L GPIO_SPKAMP_RST_L GPIO_WLAN_HSIC_HOST_RDY GPIO_BB_RADIO_ON_L GPIO_DFU_STATUS GPIO_FORCE_DFU GPIO_PMU_KEEPACT GPIO_SPKAMP_KEEPALIVE =PP1V8_S2R_MISC NC_UART4_RTC_L NO_TEST=TRUE NC_I2S4_DOUT NO_TEST=TRUE NC_AP_GPIO216 NO_TEST=TRUE GPIO_BTN_HOME_L I2C1_SCL_1V8 R0708 1 2 R0709 1 2 R0710 1 2 R07151 2 R07141 2 R07131 2 R07111 2 R0700 1 2 R07201 2 U0600 T26 W32 W28 Y33 U29 W27 W29 H20 B19 M29 M32 M26 N31 M27 L24 M24 N30 L23 H30 L29 L26 L25 L28 J29 E29 J25 M30 K32 L32 H25 K31 J32 K28 F31 K29 Y31 V28 V32 V29 AB29 Y29 AA28 AA32 AB28 AB33 AC29 W33 D19 G20 E19 F19 AB27 U0600 AK28 AJ25 AK26 AK27 AK20 AJ19 AJ18 AJ23 AK23 AJ20 AJ22 AJ24 AL25 AM26 AK25 AN26 AK22 F26 E26 J31 F29 E30 H31 J30 H32 G27 E27 AK19 F32 J28 G31 G32 G28 G33 J26 G30 G29 F27 AK21 AK24 AJ21 AK18 AL26 AH25 H19 J19 H27 G25 E31 H29 V33 W31 V27 K18 K19 AM27 AM28 AN27 AN28 Y30 AC27 AC33 AD33 AB32 AC30 AC32 AD32 Y27 AA29 AB31 AC31 J18 K17 AC28 W30 AA30 AA31 R07061 2 R07051 2 R07041 2 R07031 2 R07021 2 R07011 2 R07161 2 R07171 2 R07181 2 R07601 2 R0730 1 2 R07191 2 R07211 2 051-9385 A.0.0 7 OF 154 5 OF 39 53234 34 52030 35 52236 52236 52236 52236 519253036 2021 4571034 516 519253036 4 5 7 10 34 4571034 36 52030 5 19 5 14 36 5 26 5 5 32 5 30 5 19 53234 52330

- 8. OUT BI BI BI BI BI BI BI BI OUT OUT OUT OUT OUT OUT BI BI BI BI BI BI BI BI OUT OUT OUT OUT OUT PVDDP_GRP3 PVDDP_GRP2 PVDDP_GRP1 FMI1_WENN FMI1_WEN FMI1_REN FMI1_IO7 FMI1_IO6 FMI1_IO5 FMI1_IO4 FMI1_IO3 FMI1_IO2 FMI1_IO1 FMI1_IO0 FMI1_DQVREF FMI1_DQSN FMI1_DQS FMI1_CLE FMI1_CEN7 FMI1_CEN6 FMI1_CEN5 FMI1_CEN4 FMI1_CEN3 FMI1_CEN2 FMI1_CEN1 FMI1_CEN0 FMI1_ALE FMI0_WENN FMI0_IO4 FMI0_IO3 FMI0_IO2 FMI0_IO1 FMI0_IO0 FMI0_DQVREF FMI0_DQSN FMI0_CLE FMI0_CEN7 FMI0_CEN6 FMI0_CEN5 FMI0_CEN4 FMI0_CEN3 FMI0_CEN2 FMI0_CEN1 FMI0_CEN0 FMI0_ALE FMI0_IO7 FMI0_IO6 FMI0_IO5 FMI0_WEN FMI0_REN FMI0_DQS PVDDP_GRP4 PVDDP_GRP5 FMI1_VREFFMI0_VREF SYM 4 OF 12 VSS VSS SYM 12 OF 12 Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT 61338 1338 1338 1338 1338 1338 1338 1338 1338 1338 1338 1338 1338 1338 6 13 38 13 38 13 38 13 38 13 38 13 38 13 38 13 38 13 38 13 38 1/32W 5% 01005 MF 100K 13 38 13 38 13 38 13 38 51.1K 1/32W 1% 01005 MF 51.1K 1/32W 1% 01005 MF 01005 X5R 4V 20% 0.1UF 01005 4V 20% X5R 0.1UF OMIT_TABLE BGA BALI-H5G CKPLUS_WAIVE=PDIFPR_BADTERMCKPLUS_WAIVE=PDIFPR_BADTERM OMIT_TABLE BGA BALI-H5G 4V 20% 01005 X5R 0.1UF 4V 20% 01005 X5R 0.1UF 4V 20% 01005 X5R 0.1UF 4V 20% 01005 X5R 0.1UF 4V 20% 01005 X5R 0.1UF 1/32W 5% 01005 MF 100K AP: NAND SYNC_DATE=N/ASYNC_MASTER=N/A FMI_DQVREF_H5FMI_DQVREF_H5 =PP1V8_NAND_H5 =PP1V8_NAND_H5 =PP1V8_VDDIO18_H5 =PP1V8_VDDIO18_H5=PP1V8_NAND_H5 NO_TEST=TRUENC_FMI0_CE4_L NO_TEST=TRUENC_FMI0_CE6_L FMI0_CE0_L NO_TEST=TRUENC_FMI0_CE7_L FMI1_CE0_L NO_TEST=TRUE NC_FMI1_CE4_L NO_TEST=TRUE NC_FMI1_CE5_L NO_TEST=TRUE NC_FMI1_CE7_L NO_TEST=TRUE NC_FMI1_CE6_L NO_TEST=TRUE NC_FMI1_CE3_L NO_TEST=TRUE NC_FMI1_CE2_L NO_TEST=TRUE NC_FMI1_CE1_L NO_TEST=TRUENC_FMI0_CE3_L =PP1V8_NAND_H5 NO_TEST=TRUE NC_FMI1_DQSNNO_TEST=TRUENC_FMI0_DQSN NO_TEST=TRUENC_FMI0_CE5_L NO_TEST=TRUENC_FMI0_RE NO_TEST=TRUE NC_FMI1_RE NO_TEST=TRUENC_FMI0_CE1_L NO_TEST=TRUENC_FMI0_CE2_L FMI1_DQS FMI1_RE_L FMI1_WE_L FMI1_CLE FMI1_ALE FMI1_AD<7> FMI1_AD<6> FMI1_AD<5> FMI1_AD<4> FMI1_AD<3> FMI1_AD<2> FMI1_AD<1> FMI1_AD<0> FMI1_CE0_L FMI0_CLE FMI0_DQS FMI0_WE_L FMI0_RE_L FMI0_ALE FMI0_AD<7> FMI0_AD<6> FMI0_AD<5> FMI0_AD<4> FMI0_AD<3> FMI0_AD<2> FMI0_AD<1> FMI0_AD<0> FMI0_CE0_L R08311 2 R08321 2 R08421 2 R08431 2 C08421 2 C08431 2 U0600 AJ28 AN29 AM30 AL28 AL27 AJ32 AJ31 AM31 AL30 AH29 AL31 AL32 AG27 AM29 AK33 AJ30 AK31 AH28 AJ29 AN30 AH27 AK30 AG28 AK32 AK29 AJ33 AF29 AF30 AE29 AD30 AF27 AE27 AF28 AE28 AH31 AF32 AF33 AD27 AE33 AH33 AG33 AG30 AD31 AE31 AG29 AD29 AF31 AD28 AG32 AG31 AF26 AB26 P25 G19 K24 U0600 AB8 AB10 AB12 AB14 AB16 AB18 AB19 AB21 AB23 AB25 AB30 AC1 AC3 AC9 AC11 AC13 AC15 AC17 AC20 AC22 AC24 AD8 AD10 AD12 AD14 AD16 AD18 AD19 AD21 AD23 AD25 AE4 AE9 AE10 AE11 AE12 AE13 AE14 AE15 AE17 AE22 AE30 AE32 A6 AF3 AF16 AG2 AG16 AG17 AG25 AH5 AH10 AH15 AH16 AH17 AH30 AH32 P24 AJ17 AJ27 AK2 AK8 AK14 AK17 AH1 AL3 AL7 AL10 AL13 AL16 AL17 AL18 AL19 AL20 AL21 AL22 AL23 AL24 AL1 AL29 AM1 AM2 AM6 AM9 AM12 AM15 AM32 AM33 AN1 AN2 AL33 T20 AN11 AN14 AN32 AN33 AN3 AN31 AN6 C1 C08201 2 C08211 2 C08101 2 C08111 2 C08121 2 051-9385 A.0.0 8 OF 154 6 OF 39 66 6934 6934 467934 4 6 7 9 346934 61338 61338 6 9 34

- 9. IN OUT OUT BI BI OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT MIPI_VSS ISP0_FLASH ISP0_PRE_FLASH ISP0_SCL ISP0_SDA ISP1_FLASH ISP1_PRE_FLASH ISP1_SCL ISP1_SDA MIPI_VDD10 MIPI_VSYNC MIPI0C_DNCLK MIPI0C_DNDATA0 MIPI0C_DNDATA1 MIPI0C_DNDATA2 MIPI0C_DNDATA3 MIPI0C_DPCLK MIPI0C_DPDATA0 MIPI0C_DPDATA1 MIPI0C_DPDATA2 MIPI0C_DPDATA3 MIPI0D_VDD10_PLL MIPI0D_VDD18 MIPI0D_VREG_0P4V MIPI1C_DNCLK MIPI1C_DNDATA0 MIPI1C_DNDATA1 MIPI1C_DPCLK MIPI1C_DPDATA0 MIPI1C_DPDATA1 MIPI1D_VDD10_PLL MIPI1D_VDD18 MIPI1D_VREG_0P4V SENSOR0_CLK SENSOR0_RST SENSOR1_CLK SENSOR1_RST SYM 5 OF 12 EDP_PAD_TX3P EDP_PAD_TX3N EDP_PAD_TX2P EDP_PAD_TX2N EDP_PAD_TX1P EDP_PAD_TX1N EDP_PAD_TX0P EDP_PAD_TX0N EDP_PAD_R_BIAS EDP_PAD_DVSS EDP_PAD_DVDD EDP_PAD_DC_TP EDP_PAD_AVSSX EDP_PAD_AVSSP0 EDP_PAD_AVSS3 EDP_PAD_AVSS2 EDP_PAD_AVSS1 EDP_PAD_AVSS0 EDP_PAD_AVSS_AUX EDP_PAD_AVDDX EDP_PAD_AVDDP0 EDP_PAD_AVDD3 EDP_PAD_AVDD2 EDP_PAD_AVDD1 EDP_PAD_AVDD0 EDP_PAD_AVDD_AUX EDP_PAD_AUXP EDP_PAD_AUXN EDP_HPD DP_PAD_TX3P DP_PAD_TX3N DP_PAD_TX2P DP_PAD_TX2N DP_PAD_TX1P DP_PAD_TX1N DP_PAD_TX0P DP_PAD_TX0N DP_PAD_R_BIAS DP_PAD_DVSS DP_PAD_DVDD DP_PAD_DC_TP DP_PAD_AVSSX DP_PAD_AVSSP0 DP_PAD_AVSS3 DP_PAD_AVSS2 DP_PAD_AVSS1 DP_PAD_AVSS0 DP_PAD_AVSS_AUX DP_PAD_AVDDX DP_PAD_AVDDP0 DP_PAD_AVDD3 DP_PAD_AVDD2 DP_PAD_AVDD1 DP_PAD_AVDD0 DP_PAD_AVDD_AUX DP_PAD_AUXP DP_PAD_AUXN DP_HPD DAC_VREF DAC_OUT3 DAC_OUT2 DAC_OUT1 DAC_IREF DAC_AVSS18D DAC_AVSS18A DAC_AVDD18D DAC_AVDD18A DAC_COMP SYM 6 OF 12 OUT OUT OUT OUT OUT IN IN IN IN IN IN IN IN IN IN PART NUMBER ALTERNATE FORPART NUMBER BOM OPTION REF DES COMMENTS: TABLE_ALT_HEAD Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT TABLE_ALT_ITEM SOCHOT1_L PULL-UP ON CSA 90 3.3MA 3.3MA 15MA 65MA 2MA 40MA PER PIN 65MA 22MA 15MA 10MA PER PIN 16MA 22MA PER PIN 15MA NOTE: 0.6V ANALOG REF FRONT FACING CAM 15MA 16MA 10MA SHUTDOWN IS ACTIVE LOW SHUTDOWN IS ACTIVE HIGH REAR FACING CAM NOTE: 0.6V ANALOG REF 56PF 5% 6.3V NP0-C0G 01005 4V 20% 0.1UF X5R 0100556PF 5% 6.3V NP0-C0G 01005 0 MF 5% 1/20W 20156PF 5% 6.3V NP0-C0G 01005 0.22UF 402 20% 6.3V X5R 0.22UF 402 20% 6.3V X5R 0.22UF 20% 6.3V 402 X5R 0.01UF 6.3V X5R 10% 01005 0.01UF 6.3V X5R 10% 01005 4V 20% 0.1UF X5R 01005 25V CER 0201 +/-0.1PF% 8.2PF 0.1UF 6.3V X5R 201 10% 240-OHM-0.2A-0.8-OHM 0201 NOSTUFF 0.1UF 6.3V NOSTUFF X5R 201 10% 6.34K 1% 1/20W NOSTUFF 201 MF 0.1UF 6.3V NOSTUFF X5R 201 10% 1537 MF 5% 1/32W 1.00K 01005 MF 5% 1/32W 1.00K 01005 22 36 22 36 22 36 22 36 1.00K MF 5% 1/32W 01005 1.00K MF 5% 1/32W 01005 01005 0% 1/32W 0.00 MF 0.00 MF0% 1/32W 01005 0.1UF 6.3V X5R 201 10% 0.1UF 6.3V X5R 201 10% 0.1UF 6.3V X5R 201 10% 1UF CERM 402 6.3V 10% 0201 2.2NF 10% 10V X5R-CERM 10V X5R-CERM 10% 2.2NF 0201 56PF 5% 6.3V NP0-C0G 01005 1UF CERM 402 6.3V 10% 0.01UF 6.3V X5R 10% 01005 80-OHM-0.2A-0.4-OHM 0201-1 0.01UF 6.3V NOSTUFF X5R 10% 01005 4.99K MF 1% 1/32W 01005 1537 1537 1537 1537 1537 1537 4.99K MF 1% 1/32W 01005 1537 1537 1537 1537 0.01UF 6.3V NOSTUFF X5R 10% 01005 BALI-H5G BGA OMIT_TABLE BALI-H5G BGA OMIT_TABLE 22 22 36 22 22 36 22 21 37 21 37 21 37 21 37 2137 2137 2137 2137 2137 2137 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM +/-0.5PF 8.2PF 01005 100K MF 5% 1/32W NOSTUFF 01005 100K MF 5% 1/32W 01005 SYNC_MASTER=N/A SYNC_DATE=N/A AP: TV,DP,MIPI FL0910155S0725 155S0359 ? RDAR://PROBLEM/11104943 =PP1V0_MIPI_H5 =PP1V8_MIPI_H5 EDP_AUX_P EDP_AUX_N =PP1V8_VDDIO18_H5 MIN_LINE_WIDTH=0.2MM NET_SPACING_TYPE=PWRPP0V4_MIPI0D VOLTAGE=0.4V MIN_NECK_WIDTH=0.1MM MAX_NECK_LENGTH=3MM MAX_NECK_LENGTH=3MM MIN_NECK_WIDTH=0.1MM PP0V4_MIPI1D VOLTAGE=0.4V MIN_LINE_WIDTH=0.2MM NET_SPACING_TYPE=PWR VOLTAGE=1.8V MIN_LINE_WIDTH=0.2MM NET_SPACING_TYPE=PWR MAX_NECK_LENGTH=3MM MIN_NECK_WIDTH=0.1MM PP1V8_EDP_AVDD_AUX EDP_HPD ISP0_CAM_RF_I2C_SDA EDP_DATA_P<0> EDP_DATA_N<0> EDP_DATA_P<1> EDP_DATA_N<1> EDP_DATA_P<2> EDP_DATA_N<2> EDP_DATA_P<3> ISP1_CAM_FF_CLK MIPI1C_CAM_FF_CLK_P MIPI1C_CAM_FF_CLK_N MIPI1C_CAM_FF_DATA_N<0> MIPI1C_CAM_FF_DATA_P<0> MIPI0C_CAM_RF_CLK_P MIPI0C_CAM_RF_DATA_N<1> MIPI0C_CAM_RF_DATA_P<1> MIPI0C_CAM_RF_DATA_N<0> MIPI0C_CAM_RF_DATA_P<0> SOCHOT0_L SOCHOT1_L =PP1V8_H5 SOCHOT0_L SOCHOT1_L ISP0_CAM_RF_CLK_R NC_MIPI1C_CAM_FF_DATA_P<1>NO_TEST=TRUE NC_DAC_AP_OUT3NO_TEST=TRUE =PP1V0_MIPI_PLL_H5 NC_MIPI1C_CAM_FF_DATA_N<1>NO_TEST=TRUE NC_MIPI0C_CAM_RF_DATA_P<3> NO_TEST=TRUE NC_MIPI0C_CAM_RF_DATA_P<2> NO_TEST=TRUE NC_MIPI0C_CAM_RF_DATA_N<3> NO_TEST=TRUE NC_MIPI0C_CAM_RF_DATA_N<2> NO_TEST=TRUE DAC_AP_COMP NC_DAC_AP_OUT2NO_TEST=TRUE TP_DP_AP_ANALOG_TEST NC_DP_DATA_N<2>NO_TEST=TRUE NC_DP_DATA_P<2>NO_TEST=TRUE NC_DP_DATA_N<3>NO_TEST=TRUE NC_DP_DATA_P<3>NO_TEST=TRUE DP_R_BIAS NC_MIPI_VSYNC_H5 NO_TEST=TRUE NC_DP_DATA_N<1>NO_TEST=TRUE NC_DP_DATA_P<1>NO_TEST=TRUE NC_DP_DATA_N<0>NO_TEST=TRUE NC_DP_DATA_P<0>NO_TEST=TRUE NC_DP_AUX_NNO_TEST=TRUE VOLTAGE=1.0V NET_SPACING_TYPE=PWR MAX_NECK_LENGTH=3MM MIN_LINE_WIDTH=0.2MM MIN_NECK_WIDTH=0.1MM PP1V0_MIPI_PLL_F NC_DAC_AP_OUT1NO_TEST=TRUE NC_DP_HPDNO_TEST=TRUE NC_DP_AUX_PNO_TEST=TRUE =PP1V8_VDDIO18_H5 =PP1V0_DP_PAD_DVDD_H5 =PP1V8_EDP_H5 DAC_AP_COMP_FTR DAC_AP_IREF =PP1V8_VDDIO18_H5 =PP1V8_H5 ISP0_CAM_RF_RST_L ISP0_CAM_RF_CLK ISP1_CAM_FF_I2C_SCL =PP1V8_DP_H5 =PP1V0_EDP_PAD_DVDD_H5 ISP0_CAM_RF_SHUTDOWN ISP1_CAM_FF_CLK_R ISP1_CAM_FF_SHUTDOWN_L ISP1_CAM_FF_I2C_SDA ISP0_CAM_RF_I2C_SCL NO_TEST=TRUE NC_ISP0_CAM_RF_FLASH TP_EDP_AP_ANALOG_TEST EDP_DATA_N<3> AP_EDP_R_BIAS DAC_AP_VREF MIPI0C_CAM_RF_CLK_N C09241 2 C09271 2C09301 2 R0911 1 2 C09311 2 C09321 2 C09331 2 C09341 2 C09531 2 C09521 2 C09511 2 C09101 2 C09091 2 FL0911 1 2 C09561 2 R09501 2 C09551 2 R09331 2 R09321 2 R09311 2 R09301 2 R09001 2 R09401 2 C09071 2 C09031 2 C09081 2 C09351 2 C09611 2 C09601 2 C09821 2 C09801 2 C09811 2 FL0910 1 2 C09501 2 R09211 2 R09201 2 C09571 2 U0600 M25 M31 AA27 U28 N25 L30 AA33 U30 AN20 AN22 AN21 AN19 AN18 AM20 AM22 AM21 AM19 AM18 AH21 AH19 AH20 AN24 AN23 AN25 AM24 AM23 AM25 AH22 AH24 AH23 AF20 AF21 AF22 AF23 AF24 AG20 AG21 AG22 AG23 AG24 U27 V31 U32 U31 T27 U0600 H24 H23 G24 G23 K23 J24 F33 E33 D33J23 B18 A25 A26 E21 E20 B20 A20 D22 D21 C23 F21 F20 D20 C20 B22 B21 A23 F23 C24 A24 E23 D23 D24 B23 B24 C21 C22 A21 A22 E18 C29 C30 C28 C27 D26 D25 D30 D29 B31 A28 A27 B26 B25 B30 B29 C32 F28 C31 D31 E28 A29 A30 D27 D28 B27 B28 C25 C26 C09291 2 C09281 2 C09041 2 R09421 2 R09411 2 051-9385 A.0.0 9 OF 154 7 OF 39 34 34 4 6 7 9 34 39 7 732 4 5 7 10 34 7 7 32 36 34 39 467934 34 34 4 6 7 9 34 4 5 7 10 34 34 34 36 39

- 10. BI BI BI BI BI BI BI OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT BI BI BI BI BI BI BI BI OUT OUT OUT OUT BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT BI BI BI BI BI BI BI BI OUT OUT OUT OUT BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI OUT BI BI BI BI OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT BI BI BI BI BI BI BI BI OUT BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI OUT OUT OUT OUT BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT DDR1_VREF_DQ DDR1_VDD_CKE DDR1_RREF DDR1_PDQS3 DDR1_PDQS2 DDR1_PDQS1 DDR1_PDQS0 DDR1_NDQS3 DDR1_NDQS2 DDR1_NDQS1 DDR1_NDQS0 DDR1_DQ9 DDR1_DQ8 DDR1_DQ7 DDR1_DQ6 DDR1_DQ5 DDR1_DQ4 DDR1_DQ31 DDR1_DQ30 DDR1_DQ3 DDR1_DQ29 DDR1_DQ28 DDR1_DQ27 DDR1_DQ26 DDR1_DQ25 DDR1_DQ24 DDR1_DQ23 DDR1_DQ22 DDR1_DQ21 DDR1_DQ20 DDR1_DQ2 DDR1_DQ19 DDR1_DQ18 DDR1_DQ17 DDR1_DQ16 DDR1_DQ15 DDR1_DQ14 DDR1_DQ13 DDR1_DQ12 DDR1_DQ11 DDR1_DQ10 DDR1_DQ1 DDR1_DQ0 DDR1_DM3 DDR1_DM2 DDR1_DM1 DDR1_DM0 DDR1_CSN1 DDR1_CSN0 DDR1_CKE1 DDR1_CKE0 DDR1_CKB DDR1_CK DDR1_CA9 DDR1_CA8 DDR1_CA7 DDR1_CA6 DDR1_CA5 DDR1_CA4 DDR1_CA3 DDR1_CA2 DDR1_CA1 DDR1_CA0 DDR0_VREF_DQ DDR0_VDD_CKE DDR0_RREF DDR0_PDQS3 DDR0_PDQS2 DDR0_PDQS1 DDR0_PDQS0 DDR0_NDQS3 DDR0_NDQS2 DDR0_NDQS1 DDR0_NDQS0 DDR0_DQ9 DDR0_DQ8 DDR0_DQ7 DDR0_DQ6 DDR0_DQ5 DDR0_DQ4 DDR0_DQ31 DDR0_DQ30 DDR0_DQ3 DDR0_DQ29 DDR0_DQ28 DDR0_DQ27 DDR0_DQ26 DDR0_DQ25 DDR0_DQ24 DDR0_DQ23 DDR0_DQ22 DDR0_DQ21 DDR0_DQ20 DDR0_DQ2 DDR0_DQ19 DDR0_DQ18 DDR0_DQ17 DDR0_DQ16 DDR0_DQ15 DDR0_DQ13 DDR0_DQ12 DDR0_DQ10 DDR0_DQ1 DDR0_DQ0 DDR0_DM3 DDR0_DM2 DDR0_DM1 DDR0_DM0 DDR0_CSN1 DDR0_CSN0 DDR0_CKE1 DDR0_CKE0 DDR0_CKB DDR0_CK DDR0_CA9 DDR0_CA8 DDR0_CA7 DDR0_CA6 DDR0_CA5 DDR0_CA4 DDR0_CA3 DDR0_CA2 DDR0_CA1 DDR0_CA0 DDR0_DQ14 DDR0_DQ11 SYM 7 OF 12 DDR2_CA0 DDR2_CA1 DDR2_CA2 DDR2_CA3 DDR2_CA8 DDR2_CA9 DDR2_CK DDR2_CKB DDR2_CKE0 DDR2_CKE1 DDR2_CSN1 DDR2_DM1 DDR2_DM2 DDR2_DM3 DDR2_DQ1 DDR2_DQ14 DDR2_DQ31 DDR2_DQ5 DDR2_DQ6 DDR2_DQ7 DDR2_DQ8 DDR2_NDQS1 DDR2_NDQS2 DDR2_NDQS3 DDR2_PDQS3 DDR2_RREF DDR2_VREF_DQ DDR3_CA0 DDR3_CA1 DDR3_CA2 DDR3_CA3 DDR3_CA7 DDR3_CA8 DDR3_CA9 DDR3_CK DDR3_CKB DDR3_CKE0 DDR3_CKE1 DDR3_CSN0 DDR3_CSN1 DDR3_DM0 DDR3_DM1 DDR3_DM2 DDR3_DQ0 DDR3_DQ1 DDR3_DQ10 DDR3_DQ11 DDR3_DQ13 DDR3_DQ15 DDR3_DQ17 DDR3_DQ18 DDR3_DQ19 DDR3_DQ20 DDR3_DQ21 DDR3_DQ22 DDR3_DQ23 DDR3_DQ24 DDR3_DQ25 DDR3_DQ27 DDR3_DQ28 DDR3_DQ29 DDR3_DQ3 DDR3_DQ30 DDR3_DQ31 DDR3_DQ4 DDR3_DQ5 DDR3_NDQS0 DDR3_PDQS3 DDR3_RREF DDR3_DM3 DDR3_PDQS0DDR2_PDQS0 DDR2_NDQS0 DDR2_PDQS1 DDR2_PDQS2 DDR3_CA4 DDR2_DQ12 DDR2_VDD_CKE DDR2_CSN0 DDR2_DQ13 DDR2_DQ15 DDR2_DQ16 DDR2_DQ17 DDR2_DQ18 DDR2_DQ19 DDR2_DQ20 DDR2_DQ21 DDR2_DQ22 DDR2_DQ0 DDR2_DQ2 DDR2_DQ4 DDR2_DQ3 DDR2_CA7 DDR2_CA6 DDR2_CA5 DDR2_CA4 DDR2_DQ30 DDR2_DQ11 DDR2_DQ10 DDR2_DQ9 DDR3_DQ26 DDR3_CA5 DDR3_DQ12 DDR3_DQ14 DDR3_DQ16 DDR3_DQ2 DDR3_CA6 DDR2_DQ29 DDR2_DQ27 DDR2_DQ26 DDR2_DQ25 DDR2_DQ24 DDR2_DQ23 DDR2_DQ28 DDR2_DM0 DDR3_PDQS1 DDR3_PDQS2 DDR3_DQ9 DDR3_DQ8 DDR3_DQ7 DDR3_DQ6 DDR3_VDD_CKE DDR3_VREF_DQ DDR3_NDQS3 DDR3_NDQS2 DDR3_NDQS1 SYM 8 OF 12 BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 1238 11 38 11 38 11 38 11 38 11 38 0.01UF X5R 01005 10% 6.3V 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 4.7K MF 01005 1% 1/32W 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 4.7K MF 01005 1% 1/32W 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 11 38 0.01UF X5R 01005 10% 6.3V 11 38 11 38 11 38 11 38 11 38 11 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 4.7K MF 01005 1% 1/32W 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 4.7K MF 01005 1% 1/32W 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 12 38 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V BALI-H5G BGA OMIT_TABLE BALI-H5G BGA OMIT_TABLE 0.01UF X5R 01005 10% 6.3V 4.7K MF 01005 1% 1/32W 4.7K MF 01005 1% 1/32W 0.01UF X5R 01005 10% 6.3V 4.7K MF 01005 1% 1/32W 4.7K MF 01005 1% 1/32W 240 MF 201 1% 1/20W 240 MF 201 1% 1/20W 240 MF 201 1% 1/20W 240 MF 201 1% 1/20W 0.01UF X5R 01005 10% 6.3V 0.01UF X5R 01005 10% 6.3V 0.01UF X5R 01005 10% 6.3V 0.01UF X5R 01005 10% 6.3V 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 1138 SYNC_MASTER=N/A SYNC_DATE=N/A AP: DDR =PP1V2_S2R_H5 PPVREF_DDR1_DQ_H5 =PP1V2_VDDIOD_H5 MAX_NECK_LENGTH=3 MM VOLTAGE=0.6V MIN_LINE_WIDTH=0.3MM MIN_NECK_WIDTH=0.2MM NET_SPACING_TYPE=PWR PPVREF_DDR3_DQ_H5 MAX_NECK_LENGTH=3 MM VOLTAGE=0.6V MIN_LINE_WIDTH=0.3MM MIN_NECK_WIDTH=0.2MM NET_SPACING_TYPE=PWR PPVREF_DDR2_DQ_H5 =PP1V2_VDDIOD_H5 =PP1V2_VDDIOD_H5 MAX_NECK_LENGTH=3 MM VOLTAGE=0.6V MIN_LINE_WIDTH=0.3MM MIN_NECK_WIDTH=0.2MM NET_SPACING_TYPE=PWR PPVREF_DDR1_DQ_H5 MAX_NECK_LENGTH=3 MM VOLTAGE=0.6V MIN_LINE_WIDTH=0.3MM MIN_NECK_WIDTH=0.2MM NET_SPACING_TYPE=PWR PPVREF_DDR0_DQ_H5 =PP1V2_VDDIOD_H5 H5G_DDR1_ZQ PPVREF_DDR0_DQ_H5 H5G_DDR0_ZQ H5G_DDR2_ZQ PPVREF_DDR2_DQ_H5 H5G_DDR3_ZQ =PP1V2_S2R_H5 PPVREF_DDR3_DQ_H5 NC_DDR0_CKE<1> NO_TEST=TRUE NC_DDR0_CSN<1> NO_TEST=TRUE =PP1V2_S2R_H5 =PP1V2_S2R_H5 NC_DDR2_CSN<1>NO_TEST=TRUE NC_DDR2_CKE<1>NO_TEST=TRUE NC_DDR1_CSN<1>NO_TEST=TRUE NC_DDR1_CKE<1>NO_TEST=TRUE NC_DDR3_CSN<1>NO_TEST=TRUE NC_DDR3_CKE<1>NO_TEST=TRUE DDR0_DQ<24> DDR0_DQ<23> DDR0_DQ<22> DDR0_DQ<21> DDR0_DQ<20> DDR0_DQ<19> DDR0_DQ<18> DDR0_DQ<17> DDR0_DQ<16> DDR0_DQ<15> DDR0_DQ<14> DDR0_DQ<13> DDR0_DQ<12> DDR0_DQ<11> DDR0_DQ<10> DDR0_DQ<9> DDR0_DQ<8> DDR0_DQ<7> DDR0_DQ<6> DDR0_DQ<5> DDR0_DQ<3> DDR0_DQ<4> DDR0_DQ<2> DDR0_DQ<1> DDR0_DQ<0> DDR3_CSN<0> DDR3_CKE<0> DDR3_CK_N DDR3_CK_P DDR3_CA<7> DDR3_CA<6> DDR3_CA<5> DDR3_CA<4> DDR3_DM<3> DDR3_DM<2> DDR3_DM<1> DDR3_DM<0> DDR3_CA<8> DDR3_CA<9> DDR3_DQS_P<2> DDR3_DQS_N<2> DDR3_DQS_P<3> DDR3_DQS_N<3> DDR3_DQS_P<0> DDR3_DQS_N<0> DDR3_DQS_P<1> DDR3_DQS_N<1> DDR3_DQ<20> DDR3_DQ<19> DDR3_DQ<18> DDR3_DQ<17> DDR3_DQ<16> DDR3_DQ<27> DDR3_DQ<26> DDR3_DQ<25> DDR3_DQ<24> DDR3_DQ<23> DDR3_DQ<22> DDR3_DQ<21> DDR3_DQ<31> DDR3_DQ<30> DDR3_DQ<29> DDR3_DQ<28> DDR3_CA<0> DDR3_CA<1> DDR3_CA<2> DDR3_CA<3> DDR3_DQ<0> DDR3_DQ<1> DDR3_DQ<2> DDR3_DQ<3> DDR3_DQ<4> DDR3_DQ<5> DDR3_DQ<6> DDR3_DQ<13> DDR3_DQ<12> DDR3_DQ<11> DDR3_DQ<10> DDR3_DQ<9> DDR3_DQ<8> DDR3_DQ<7> DDR3_DQ<15> DDR3_DQ<14> DDR1_CSN<0> DDR1_DQS_N<1> DDR1_DQS_P<1> DDR1_DQS_N<0> DDR1_DQS_P<0> DDR1_DQS_N<3> DDR1_DQS_P<3> DDR1_DQS_N<2> DDR1_DQS_P<2> DDR1_CA<9> DDR1_CA<8> DDR1_CK_P DDR1_CK_N DDR1_CKE<0> DDR1_DM<0> DDR1_DM<1> DDR1_DM<2> DDR1_DM<3> DDR1_CA<4> DDR1_CA<5> DDR1_CA<6> DDR1_CA<7> DDR1_CA<3> DDR1_CA<2> DDR1_CA<1> DDR1_DQ<28> DDR1_DQ<29> DDR1_DQ<30> DDR1_DQ<31> DDR1_CA<0> DDR1_DQ<21> DDR1_DQ<22> DDR1_DQ<23> DDR1_DQ<24> DDR1_DQ<25> DDR1_DQ<26> DDR1_DQ<27> DDR1_DQ<14> DDR1_DQ<15> DDR1_DQ<16> DDR1_DQ<17> DDR1_DQ<18> DDR1_DQ<19> DDR1_DQ<20> DDR1_DQ<7> DDR1_DQ<8> DDR1_DQ<9> DDR1_DQ<10> DDR1_DQ<11> DDR1_DQ<12> DDR1_DQ<13> DDR1_DQ<6> DDR1_DQ<5> DDR1_DQ<4> DDR1_DQ<3> DDR1_DQ<2> DDR1_DQ<1> DDR1_DQ<0> DDR2_CSN<0> DDR2_CKE<0> DDR2_CK_P DDR2_CK_N DDR2_DQS_P<3> DDR2_DQS_N<3> DDR2_DQS_N<2> DDR2_DQS_P<2> DDR2_DQS_N<1> DDR2_DQS_N<0> DDR2_DQS_P<1> DDR2_DQS_P<0> DDR2_DM<3> DDR2_DM<1> DDR2_DM<2> DDR2_DM<0> DDR2_CA<9> DDR2_CA<7> DDR2_CA<8> DDR2_CA<6> DDR2_CA<5> DDR2_CA<4> DDR2_CA<2> DDR2_CA<3> DDR2_CA<1> DDR2_CA<0> DDR2_DQ<31> DDR2_DQ<30> DDR2_DQ<29> DDR2_DQ<27> DDR2_DQ<28> DDR2_DQ<26> DDR2_DQ<25> DDR2_DQ<24> DDR2_DQ<22> DDR2_DQ<23> DDR2_DQ<21> DDR2_DQ<20> DDR2_DQ<19> DDR2_DQ<17> DDR2_DQ<18> DDR2_DQ<16> DDR2_DQ<15> DDR2_DQ<14> DDR2_DQ<13> DDR2_DQ<12> DDR2_DQ<11> DDR2_DQ<9> DDR2_DQ<10> DDR2_DQ<8> DDR2_DQ<7> DDR2_DQ<6> DDR2_DQ<5> DDR2_DQ<4> DDR2_DQ<3> DDR2_DQ<2> DDR2_DQ<1> DDR2_DQ<0> DDR0_CSN<0> DDR0_CK_N DDR0_CKE<0> DDR0_CK_P DDR0_DQS_P<3> DDR0_DQS_N<2> DDR0_DQS_N<1> DDR0_DQS_P<2> DDR0_DQS_P<1> DDR0_DQS_N<0> DDR0_DQS_P<0> DDR0_DM<3> DDR0_DM<2> DDR0_DM<1> DDR0_DM<0> DDR0_CA<9> DDR0_CA<8> DDR0_CA<7> DDR0_CA<6> DDR0_CA<5> DDR0_CA<4> DDR0_CA<3> DDR0_CA<2> DDR0_CA<1> DDR0_CA<0> DDR0_DQ<31> DDR0_DQ<30> DDR0_DQ<29> DDR0_DQ<28> DDR0_DQ<27> DDR0_DQ<26> DDR0_DQ<25> DDR0_DQS_N<3> C10561 2 R10551 2 R10561 2 C10541 2 R10531 2 R10541 2 C10841 2 R10831 2 R10841 2 C10961 2 R10951 2 R10961 2 R10201 2 R10211 2 R10221 2 R102341 2 C10571 2 C10581 2 C10951 2 C10851 2 C10201 2 C10211 2 C10221 2 C10231 2 U0600 G5 G6 H5 H6 J5 M5 M6 N6 P5 P6 P4 N4 J1 K1 K6 J6 E12 E9 C14 D6 B14 B13 B8 C8 B7 B6 C6 D7 B17 C17 B16 E17 D13 D16 E16 C15 D15 E6 B5 C5 E5 C4 D4 C12 B3 C3 D12 B11 C11 B10 C9 D9 A12 A8 A15 A5 A13 A7 A16 A4 M4 H15 D10 E15 F15 F14 E14 F13 E8 F8 F7 E7 F6 F11 F12 A10 A9 F10 E13 L5 N5 G4 R5 H2 H3 P3 R3 T2 R4 T3 T4 C2 D2 E2 E4 J3 E3 F3 F4 G2 U3 V2 V3 U5 V4 V5 J4 U6 V6 K2 L2 K4 K5 N2 P2 H1 M1 E1 R1 G1 N1 D1 T1 E11 H8 L3 U0600 AH6 AG6 AH7 AG7 AH8 AH11 AG11 AG12 AH12 AG13 AH14 AH13 AN10 AN9 AG9 AG8 AD4 AG4 AB6 AK4 AB2 AB3 AG5 AH2 AJ2 AG3 AH3 AJ3 W2 W4 Y2 Y3 AC2 Y4 AA3 AA4 AA5 AK3 AL2 AM3 AM4 AL4 AL5 AC4 AK5 AJ5 AD2 AD3 AE2 AE3 AF2 AF4 AB1 AF1 W1 AJ1 AA1 AG1 V1 AK1 AH9 Y8 AB4 W5 W6 Y5 Y6 AA6 AD6 AE5 AE6 AF6 AF5 AH4 AJ4 AD1 AE1 AC6 AC5 AK11 AG14 AJ8 AG15 AL8 AL9 AK12 AJ12 AM13 AK13 AJ13 AJ14 AM5 AL6 AK6 AJ6 AK9 AM7 AK7 AJ7 AM8 AM14 AL14 AJ15 AK15 AL15 AJ16 AJ9 AK16 AM16 AM10 AJ10 AK10 AL11 AM11 AL12 AN8 AN12 AN5 AN15 AN7 AN13 AN4 AN16 AB5 AE8 AJ11 051-9385 A.0.0 10 OF 154 8 OF 39 8 34 8 8934 88 8934 8934 8 8 8934 8 8 8 34 8 834 834

- 11. VDD VDD SYM 10 OF 12 SYM 9 OF 12 VDD_ANA_TMPSADC1 VDD_ANA_TMPSADC0 VDD_ANA1 VDD_ANA0 VDDIOD3 VDDIOD2 VDDIOD0 VDDIOD VDDIO30_GRP3 VDDIO30_GRP2 VDDIO30_GRP1 VDDIO18_GRP6 VDDIO18_GRP5 VDDIO18_GRP4 VDDIO18_GRP3 VDDIO18_GRP2 VDDIO18_GRP1 VDD_SRAM VDD_CPU1 VDD_CPU0 VDD_CPUB VDDIOD1 Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT PART NUMBER ALTERNATE FORPART NUMBER BOM OPTION REF DES COMMENTS: TABLE_ALT_HEAD TABLE_ALT_ITEM FAST SCAN CLK 12MA 12MA 10MA 35MA 18MA 45MA 45MA 52MA GPIO_3V0 FMI0-3 (1.8V) 9500MA MAX 2MA TEMP SENSOR ANALOG 45MA 5MA 5MA 2MA I2C2 SPI3 2.5A@1.1V 2.5A@1.1V USB11 FMI1-3 (1.8V) 1000MA@1.2V 550MA@1.1V 1.1A@1.1V 6.3V 20% 603 X5R 10UF 10UF X5R 603 20% 6.3V 0.22UF 20% 6.3V X5R 0201 0.22UF 20% 6.3V 0201 X5R 0.22UF X5R 0201 20% 6.3V 10UF X5R 603 20% 6.3V 0.22UF X5R 0201 20% 6.3V 4.3UF X5R-CERM 0610 20% 4V 56PF 5% 6.3V NP0-C0G 01005 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 4.3UF X5R-CERM 20% 4V 0610 4.3UF X5R-CERM 20% 4V 0610 4.3UF X5R-CERM 0610 20% 4V 4.3UF X5R-CERM 0610 20% 4V 10UF X5R 603 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF 0201 20% X5R 6.3V 0.22UF 20% 6.3V 0201 X5R 10UF X5R 603 20% 6.3V 4.3UF X5R-CERM 0610 20% 4V 4.3UF 0610 20% 4V X5R-CERM 4.3UF X5R-CERM 0610 20% 4V 4.3UF X5R-CERM 0610 20% 4V 0610 4V 4.3UF 20% X5R-CERM 4V 20% 0610 4.3UF X5R-CERM 10UF X5R 603 20% 6.3V 10UF X5R 603 20% 6.3V 10UF X5R 603 20% 6.3V 10UF X5R 20% 6.3V 603 0.22UF 20% 6.3V 0201 X5R 1UF CERM 402 10% 6.3V 1UF CERM 402 10% 6.3V 1UF CERM 402 10% 6.3V 1UF CERM 402 10% 6.3V 1UF CERM 402 10% 6.3V 1UF CERM 402 10% 6.3V 0.1UF X5R-CERM 20% 6.3V 01005 0.1UF X5R-CERM 20% 6.3V 01005 0.1UF 20% 6.3V X5R-CERM 01005 0.1UF 20% 6.3V X5R-CERM 01005 0.1UF 20% 6.3V X5R-CERM 01005 0.1UF 20% 6.3V X5R-CERM 01005 0.1UF 20% 6.3V X5R-CERM 01005 0.1UF 20% 6.3V X5R-CERM 01005 4.3UF X5R-CERM 0610 20% 4V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 10UF CERM-X5R 0402-1 20% 6.3V 6.3V CERM-X5R 0402-1 10UF 20% 6.3V CERM-X5R 0402-1 10UF 20% 6.3V 10% 402 CERM 1UF 4V 20% X5R-CERM 0610 4.3UF 402 CERM 6.3V 1UF 10% 4V 20% 0204 X7S 0.47UF CRITICAL 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.1UF X5R-CERM 20% 6.3V 01005 0.1UF X5R-CERM 20% 6.3V 01005 4.3UF X5R-CERM 0610 20% 4V 4.3UF X5R-CERM 0610 20% 4V 0.1UF X5R-CERM 20% 6.3V 01005 0.1UF X5R-CERM 20% 6.3V 01005 1UF X5R 0201 20% 6.3V 4.3UF X5R-CERM 0610 20% 4V 4.3UF X5R-CERM 0610 20% 4V 20% 6.3V X5R 0201 1UFBALI-H5G BGA OMIT_TABLE BALI-H5G BGA OMIT_TABLE 1UF X5R 0201 20% 6.3V 6.3V 20% 0201 X5R 1UF 1UF X5R 0201 20% 6.3V 20% 6.3V X5R 0201 1UF 20% 6.3V X5R 0201 1UF 20% 6.3V X5R 0201 1UF 1UF 0201 20% 6.3V X5R 1UF X5R 0201 6.3V 20% CERM-X5R-1 201 20% 4V 0.47UF 0.47UF 20% 4V CERM-X5R-1 201 1UF X5R 0201 20% 6.3V 1UF X5R 0201 20% 6.3V 1UF X5R 0201 20% 6.3V 1UF X5R 0201 20% 6.3V 20% 6.3V X5R 0201 1UF 20% 6.3V X5R 0201 1UF 20% 6.3V X5R 0201 1UF 20% 6.3V X5R 0201 1UF 1UF X5R 0201 20% 6.3V 1UF X5R 0201 20% 6.3V 0.47UF CERM-X5R-1 201 20% 4V 201 20% 4V 0.47UF CERM-X5R-1 0.47UF CERM-X5R-1 201 20% 4V 0.47UF CERM-X5R-1 201 20% 4V 0.47UF CERM-X5R-1 201 20% 4V 0.47UF CERM-X5R-1 201 20% 4V 0.47UF CERM-X5R-1 201 20% 4V 0.47UF CERM-X5R-1 20% 4V 201201 CERM-X5R-1 4V 20% 0.47UF0.47UF 201 20% 4V CERM-X5R-1 1UF X5R 0201 20% 6.3V 1UF X5R 0201 20% 6.3V 0.47UF CERM-X5R-1 201 20% 4V 0.47UF CERM-X5R-1 201 20% 4V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 0.22UF X5R 0201 20% 6.3V 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 16V NP0-C0G-CERM 01005 8.2PF +/-0.5PF 0.22UF 20% 6.3V X5R 0201 20% 6.3V 0.22UF 0201 X5R 0.22UF 20% 6.3V 0201 X5R 20% 6.3V 0201 X5R 0.22UF AP: POWER SYNC_DATE=N/ASYNC_MASTER=N/A 138S0702 138S0657 QTY 21 RDAR://PROBLEM/8837828 C1106,C1107,C1108,C1109,C1110,C1111,C1147,C1148,C1155,C1156,C1167,C1168,C1180,C1181,C1190,C1191,C1315,C1321,C1415,C1421,CA194 =PPVDD_SOC_H5 =PPVDD_SOC_H5 =PPVDD_CPU0_H5 =PPVDD_CPUB_H5 =PP1V8_NAND_H5 =PP3V0_VDDIO30_H5 =PP1V8_VDDIO18_H5 =PP1V8_VDDIO18_H5 =PP3V0_VDDIO30_H5 =PP1V2_VDDIOD_H5 =PPVDD_SRAM_H5 =PPVDD_CPU1_H5 C1135 1 2 C11341 2 C11331 2 C11321 2 C11311 2 C11301 2 C11291 2 C1128 1 2 C1100 1 2 C1101 1 2 C1142 1 2 C1192 1 2 C11971 2 C1191 1 2 C11451 2 C11991 2 C11981 2 CA1921 2 CA1911 2 C1147 1 2 C1148 1 2 C1181 1 2 C1180 1 2 C1179 1 2 CA1881 2 CA1871 2 CA1861 2 CA185 1 2 C1111 1 2 C1110 1 2 C1109 1 2 C1108 1 2 C1107 1 2 C1106 1 2 C1103 1 2 C1102 1 2 C1105 1 2 C1104 1 2 C11151 2 C11141 2 C11131 2 C11181 2 C11171 2 C11161 2 C1153 1 2 C1154 1 2 C1136 1 2 C1137 1 2 C1138 1 2 C1139 1 2 C1140 1 2 C1141 1 2 C1190 1 2 C11431 2 C11441 2 CA1931 2 CA1971 2 CA1961 2 CA1951 2 CA1941 2 CA1981 2 CA1991 2 CA1901 2 CA1891 2 C1178 1 2 C1177 1 2 C1167 1 2 C1168 1 2 C1166 1 2 C1165 1 2 C1157 1 2 C1156 1 2 C1155 1 2 C1161 1 2 U0600 J8 J10 L8 AD11 AD13 AD15 AD17 AE16 AE18 AF17 U20 R18 R24 L10 L12 L14 L16 L18 L20 L22 M9 M11 J12 M13 M15 M17 M19 M21 M23 N8 N10 N12 N14 J14 N16 N18 N20 N22 P9 P11 P15 P17 P19 P21 J22 P23 R8 R10 R12 R14 R16 R20 R22 T9 T11 K9 T13 T15 T17 T21 T23 U8 U10 U12 U14 U16 K11 U22 U24 V9 V11 V13 V15 V17 V25 W8 W10 K13 W12 W14 W16 T19 W26 Y9 Y11 Y13 Y15 Y17 K15 Y26 AA8 AA10 AA12 AA14 AA16 AA18 AA26 AB9 AB11 K21 AB13 AB15 AB17 AC8 AC10 AC12 AC14 AC16 AC18 AD9 U0600 AE20 AE24 W18 P13 AA21 AB20 AB22 AC19 AC21 AD20 AE19 AE21 AA23 AB24 AC23 AC25 AD22 AD24 AE23 AE25 V20 V22 V24 Y20 Y22 Y24 AA19 AA25 W19 W21 W23 W25 H18 H26 J27 K27 L27 N29 U25 U26 V26 AF25 AH18 N28 F18 K25 J20 K20 AG26 AH26 AJ26 AC26 AD26 AE26 G7 G8 J7 K7 L7 M7 N7 P7 R7 T7 U7 V7 G9 W7 Y7 AA7 AB7 AC7 AD7 AE7 AF7 AF8 AF9 G10 AF10 AF11 AF12 AF13 AF14 AF15 G11 G12 G13 G14 G15 H7 C1158 1 2 C1159 1 2 C1160 1 2 C1162 1 2 C1163 1 2 C1164 1 2 C1149 1 2 C1150 1 2 C1151 1 2 C1152 1 2 C1169 1 2 C1170 1 2 C1171 1 2 C1172 1 2 C1173 1 2 C1174 1 2 C1175 1 2 C1176 1 2 C1182 1 2 C1183 1 2 C1184 1 2 C1185 1 2 C1126 1 2 C1125 1 2 C1124 1 2 C1123 1 2 C1122 1 2 C1121 1 2 C1120 1 2 C1119 1 2 C1193 1 2 C1194 1 2 C1195 1 2 C1196 1 2 CA1531 2 CA1521 2 CA1511 2 CA1501 2 C11B0 1 2 C11B1 1 2 C11C0 1 2 C11C1 1 2 C11D1 1 2 C11D0 1 2 C11E1 1 2 C11E0 1 2 C11A1 1 2 C11A0 1 2 C11F01 2 051-9385 A.0.0 11 OF 154 9 OF 39 934 934 34 34 634 934 467934 4 6 7 9 34 934 8 34 34 34

- 12. OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUTIN OUT Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT 011 DVT EVT010 CURRENT SETTING ---> X140 AP BB_26 (MLB E) X140 DEV BB_42 X140 AP WLAN (MLB A) 0010 SPI0 W/TEST BOARD_ID[2] BOARD_ID[1] BOARD_ID[3] X140 DEV BB_26 X140 DEV BB_26A X140 AP BB_26A (MLB D) X140 AP BB_42 (MLB C) X140 DEV BB_41 X140 AP BB_41 (MLB B) BOARD ID 0101 0100 0010 0011 1011 1010 1110 1111 0000 0001 000 BRD_REV[2-0] PROTO 3. READ 2. ENABLE PU AND DISABLE PD S/W READ FLOW 1. SET GPIO AS INPUT FOR REFERENCE 1110 3. READ 1101 FMI0/1 4/4 CS 3. READ BOOT_CONFIG[2] BOOT_CONFIG[3] BOOT_CONFIG[1] BOOT_CONFIG[0] 0001 SPI1 FMI0/1 2/2 CS1100 1101 0100 FMI0 2CS BOOT_CONFIG[3:0] 1111 RESERVED 1100 FMI0/1 2/2 CS STUFF FOR FORM FACTOR BOARD FMI0/1 4/4 CS FMI0/1 4/4 CS WITH TEST S/W READ FLOW JTAG 1110 FMI0/1 4/4 CS W/TEST 1010 FMI1 4CS W/TEST 1000 FMI1 2 CS 0111 RESERVED 0011 SPI1 W/TEST 1001 FMI1 4 CS 0110 FMI0 4CS W/TEST 0000 SPI0 2. DISABLE PU AND ENABLE PD S/W READ FLOW 1. SET GPIO AS INPUT X140 DEV WLAN BOARD_ID[3-0] BOOT CONFIG ID BOOT_CONFIG[3-0] 2. DISABLE PU AND ENABLE PD 1. SET GPIO AS INPUTCURRENT SETTING ---> PROTO 2001 0101 FMI0 4CS BOARD_ID[0] BOARD REVISION 01005 1/32W 5% MF 10K MLB_B&MLB_D 4 4 36 39 1/32W 5% 01005 MF 10K 1/32W 5% 01005 MF 10K NOSTUFF 1/32W 5% 01005 MF 10K 1/32W 5% 01005 MF 10K DEV 1/32W 5% 01005 MF 10K MLB_C&MLB_E 1/32W 5% 01005 MF 100K SHORT-01005 NOSTUFF SHORT-01005 NOSTUFF SHORT-01005 NOSTUFF 5 5 5 5 5 5 5 5 5 5 4 4 4 4 3025 MLB_D&MLB_E 1/32W 5% 01005 MF 10K 5 NOSTUFF 1/32W 5% 01005 MF 10K 5% 100 MF 01005 1/32W 5% 100 MF 01005 1/32W NOSTUFF 10K 5% MF 01005 1/32W NOSTUFF 10K MF 01005 5% 1/32W 10K MF 01005 5% 1/32W SYNC_MASTER=N/A SYNC_DATE=N/A AP: MISC & ALIASES GPIO_BOARD_ID_3 =PP1V8_H5 GPIO_BOARD_ID_2 GPIO_BOARD_ID_1 GPIO_BRD_REV0 GPIO_BRD_REV1 GPIO_BRD_REV2 PMU_USB_BRICKID JTAG_AP_SEL GPIO_BOOT_CONFIG_1 GPIO_BOOT_CONFIG_2 AP_TST_STPCLK AP_FAST_SCAN_CLK AP_HOLD_RESET AP_TESTMODE JTAG_AP_TRST_L =PP1V8_H5 GPIO_BOOT_CONFIG_3 GPIO_BOOT_CONFIG_0 USB_BRICKID MAKE_BASE=TRUE GPIO_BOARD_ID_0 R12051 2 R12021 2 R1210 1 2 R1211 1 2 R12071 2 R12081 2 R12091 2 R12011 2 R12001 2 R12031 2 R12061 2 R12041 2 R1260 1 2 XW1200 12 XW1201 12 XW1202 12 R12201 2 051-9385 A.0.0 12 OF 154 10 OF 39 4571034 4571034

- 13. CK_1 DQ13_2 DQ14_2 DQ2_2 DQ1_2 DQ0_2 CKB_2 CKE_2 DQ21_1 DQ12_1 DQ11_1 DQ10_1 DQ0_1 DQ1_1 DQ2_1 DQ3_1 DQ4_1 DQ5_1 CSB_1 CKE_1 CKB_1 CA9_1 CA8_1 CA7_1 CA6_1 CA5_1 CA4_1 CA3_1 CA2_1 CA1_1 CA0_1 DQSB2_1 DQS2_1 DQ20_1 DQ19_1 DQ22_1 DQ23_1 DQ18_1 DQ16_1 DQ17_1 DQ15_1 DQ14_1 DQ13_1 DQ9_1 DQ7_1 DQ8_1 DQ6_1 DQ24_1 DQ31_1 DQ30_1 DQ31_2 DQ29_2 DQ30_2 DQ28_2 DQ26_2 DQ27_2 DQ25_2 DQ24_2 DQ23_2 DQ21_2 DQ22_2 DQ20_2 DQ19_2 DQ18_2 DQ17_2 DQ16_2 DQ15_2 DQ12_2 DQ11_2 DQ10_2 DQ8_2 DQ9_2 DQ6_2 DQ7_2 DQ5_2 DQ4_2 DQ3_2 DQSB3_2 DQS3_2 CA7_2 CA8_2 CA9_2 CK_2 DQS1_2 VREFCA_1 VREFCA_2 VREFDQ_1 VREFDQ_2 2_QZ1_QZ DQSB3_1 DQSB2_2 DQSB1_2DQSB1_1 DQSB0_2DQSB0_1 DQS3_1 DQS2_2 DQS1_1 DQS0_2DQS0_1 DQ29_1 DQ28_1 DQ27_1 DQ26_1 DQ25_1 CA6_2 CA5_2 CA4_2 CA3_2 CA2_2 CA1_2 CA0_2 DM0_1 DM1_1 DM2_1 DM3_1 CSB_2 DM0_2 DM1_2 DM2_2 DM3_2 DDR_1 DDR_2 SYM 1 OF 2 VDD1_3 VDD1_1 VSS55 VSS51 VSS6 VSS49 VSS4 VSS3 VDDQ33 VDDCA1 VDDCA2 VSS46 VDD1_0 VDD1_8 VDD1_5 VDD1_6 VDD1_7 VSS52 VSS0 VSS2 VSS7 VSS9 VSS10 VSS13 VSS18 VSS20 VSS32 VSS33 VSS34 VSS42 VSS43 VSS44 VSS29 VSS28 VSS27 VSS26 VSS25 VSS23 VSS22 VSS47 VSS53 VSS48 VSS50 VSS1 VSS12 VDD1_11 VDD2_3 VDD2_2 VDD1_2 VDD2_6 VDD2_7 VDD2_13 VDD2_14 VDD2_16 VDDQ27 VDDQ32 VDDQ31 VDDQ VDDQ6 VDDQ23 VDDQ30 VDDQ22 VDDQ16 VDDQ34 VDDQ17 VDDQ21 VDDQ19 VDDQ24 VDDQ20 VDDQ28 VDDCA3 VDDCA4 VDDCA5 VDDCA6 VDDCA7 VDDCA8 VDD2_1 VDDQ26 VDDQ25 VSS24 VDD2_9 VDD2_8 VDDQ1 VDD1_9 VDD1_10 VDDCA9 VDDCA10 VDDQ29 VDDQ3 VDD1_4 VDD2_5 VDD2_4 VDD2_15 VSS41 VSS40 VSS39 VSS54 VSS36 VSS35 VDD2_10 VDD2_11 VDD2_12 VSS45 VDD2VDDQVDDCAVDD1 VSS SYM 2 OF 2 Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT X5R 20% 10UF 6.3V 603 X5R 20% 0201 6.3V 0.22UF 10% X5R 0.01UF 6.3V 01005 X5R 20% 0.22UF 0201 6.3V 6.3V 5% 01005 NP0-C0G 56PF X5R 20% 0.22UF 0201 6.3V 10% 10V 0.01UF 0201 X5R-CERM X5R 20% 0.22UF 0201 6.3V X5R 20% 0.22UF 0201 6.3V 10% 6.3V 402 CERM 1UF X5R 20% 0.22UF 0201 6.3V 10% X5R 0.01UF 01005 6.3V X5R 20% 0.22UF 0201 6.3V 10% X5R 0.01UF 6.3V 01005 NP0-C0G 01005 6.3V 56PF 5% 10% X5R 0.01UF 6.3V 01005 X5R 0.22UF 20% 0201 6.3V 10% 6.3V 1UF CERM 402 X5R 20% 0.22UF 0201 6.3V X5R 20% 0.22UF 0201 6.3V 10% 6.3V 402 CERM 1UF 10% X5R 0.01UF 6.3V 01005 20% 4.3UF 0610 4V X5R-CERM 20% 0610 X5R-CERM 4V 4.3UF X5R 20% 6.3V 10UF 603 X5R 10UF 20% 6.3V 603 6.3V 5% 01005 NP0-C0G 56PF 10% 402 6.3V 1UF CERM X5R 20% 0.22UF 0201 6.3V 5% 56PF 01005 NP0-C0G 6.3V X5R 20% 6.3V 10UF 603 201 240 1% 1/20W MF 10% X5R 0.01UF 6.3V 01005 01005 MF 1/32W 1% 10K 10% X5R 0.01UF 6.3V 01005 X5R 20% 0.22UF 0201 6.3V01005 MF 1/32W 1% 10K 201 MF 1/20W 1% 240 10% X5R 0.01UF 6.3V 01005 01005 MF 1/32W 1% 10K 10% X5R 0.01UF 6.3V 0100501005 MF 1/32W 1% 10K 10% 6.3V 402 1UF CERM 10% X5R 0.01UF 6.3V 01005 10% X5R 0.01UF 6.3V 01005 01005 MF 1/32W 1% 4.7K 01005 MF 1/32W 1% 4.7K 01005 MF 1/32W 1% 4.7K 10% X5R 0.01UF 6.3V 01005 10% X5R 0.01UF 6.3V 0100501005 MF 1/32W 1% 4.7K X5R 20% 6.3V 0.22UF 0201 OMIT_TABLE BGA XXXMB H4G-DRAM OMIT_TABLE XXXMB H4G-DRAM BGA 10% 6.3V 1UF CERM 402 SYNC_MASTER=N/A DDR 0 AND 1 SYNC_DATE=N/A NET_SPACING_TYPE=PWR MIN_LINE_WIDTH=0.3MM VOLTAGE=0.6V PPVREF_DDR1_DQ MIN_NECK_WIDTH=0.2MM MAX_NECK_LENGTH=3 MM =PP1V2_VDDQ_DDR NET_SPACING_TYPE=PWR VOLTAGE=0.6V MIN_LINE_WIDTH=0.3MM MAX_NECK_LENGTH=3 MM MIN_NECK_WIDTH=0.2MM PPVREF_DDR0_DQ =PP1V2_VDDQ_DDR MIN_NECK_WIDTH=0.2MM NET_SPACING_TYPE=PWR MAX_NECK_LENGTH=3 MM MIN_LINE_WIDTH=0.3MM VOLTAGE=0.6V PPVREF_DDR1_CA =PP1V2_S2R_DDR VOLTAGE=0.6V NET_SPACING_TYPE=PWR MIN_LINE_WIDTH=0.3MM MIN_NECK_WIDTH=0.2MM MAX_NECK_LENGTH=3 MM PPVREF_DDR0_CA =PP1V2_S2R_DDR =PP1V2_S2R_DDR DDR1_DQ<8> DDR0_DQ<11> DDR1_DQ<12> DDR1_DQ<13> DDR1_DM<2> DDR1_CA<7> DDR1_CA<5> =PP1V8_S2R_DDR DDR1_DM<1> DDR0_DQ<14> DDR0_DQ<2> DDR0_DQ<13> =PP1V2_VDDQ_DDR =PP1V2_S2R_DDR DDR0_DQ<8> DDR0_DQ<9> DDR0_DQ<10> DDR1_CK_P DDR0_DQ<5> DDR0_DQ<6> DDR0_CK_N DDR0_CKE<0> DDR1_DQ<29> DDR1_DQ<4> DDR1_DQ<3> DDR1_DQ<2> DDR1_DQ<9> DDR1_DQ<10> DDR1_DQ<11> DDR1_CSN<0> DDR1_CKE<0> DDR1_CK_N DDR1_CA<9> DDR1_CA<8> DDR1_CA<6> DDR1_CA<4> DDR1_CA<3> DDR1_CA<2> DDR1_CA<1> DDR1_CA<0> DDR1_DQS_N<3> DDR1_DQS_P<3> DDR1_DQ<28> DDR1_DQ<27> DDR1_DQ<30> DDR1_DQ<31> DDR1_DQ<26> DDR1_DQ<24> DDR1_DQ<25> DDR1_DQ<7> DDR1_DQ<6> DDR1_DQ<5> DDR1_DQ<1> DDR1_DQ<15> DDR1_DQ<0> DDR1_DQ<14> DDR1_DQ<16> DDR1_DQ<23> DDR1_DQ<22> DDR0_DQ<23> DDR0_DQ<21> DDR0_DQ<22> DDR0_DQ<20> DDR0_DQ<18> DDR0_DQ<19> DDR0_DQ<17> DDR0_DQ<16> DDR0_DQ<31> DDR0_DQ<29> DDR0_DQ<30> DDR0_DQ<28> DDR0_DQ<27> DDR0_DQ<26> DDR0_DQ<25> DDR0_DQ<24> DDR0_DQ<7> DDR0_DQ<4> DDR0_DQ<3> DDR0_DQ<0> DDR0_DQ<1> DDR0_DQ<15> DDR0_DQ<12> DDR0_DQS_N<2> DDR0_DQS_P<2> DDR0_CA<7> DDR0_CA<8> DDR0_CA<9> DDR0_CK_P DDR0_DQS_P<0> PPVREF_DDR0_CA PPVREF_DDR0_DQ DDR0_DQS_N<3> DDR0_DQS_N<0>DDR1_DQS_N<0> DDR0_DQS_N<1>DDR1_DQS_N<1> DDR1_DQS_P<2> DDR0_DQS_P<3> DDR1_DQS_P<0> DDR0_DQS_P<1>DDR1_DQS_P<1> DDR1_DQ<21> DDR1_DQ<20> DDR1_DQ<19> DDR1_DQ<18> DDR1_DQ<17> DDR0_CA<6> DDR0_CA<5> DDR0_CA<4> DDR0_CA<3> DDR0_CA<2> DDR0_CA<1> DDR0_CA<0> DDR1_DM<0> DDR1_DM<3> DDR0_CSN<0> DDR0_DM<1> DDR0_DM<0> DDR0_DM<3> DDR0_DM<2> PPVREF_DDR1_DQ PPVREF_DDR1_CA DDR1_DQS_N<2> DDR1_ZQ DDR0_ZQ C1305 1 2 C1304 1 2 C1309 1 2 C13081 2 C1303 1 2 C13071 2 C1302 1 2 C1301 1 2 C1306 1 2 C1322 1 2 C13131 2 C1319 1 2 C1312 1 2 C1318 1 2 C1326 1 2 C1311 1 2 C13171 2 C1325 1 2 C13241 2 C1331 1 2 C1335 1 2 C1330 1 2 C13341 2 C1329 1 2 C13331 2 C1310 1 2 C1316 1 2 C1315 1 2 C1321 1 2 C1314 1 2 C1320 1 2 C13231 2 C1328 1 2 C1332 1 2 C1327 1 2 R13211 2 C13601 2 R13051 2 C13501 2 R13061 2 R13201 2 C13611 2 R13511 2 C13521 2 R13521 2 C13621 2 C13541 2 R13531 2 R13541 2 R13551 2 C13631 2 C13561 2 R13561 2 U1300 T15 G16 U15 G17 U14 H17 V14 H18 T13 J16 T9 N16 U9 N17 U8 P17 V8 P18 T7 R16 U12 K17 U11 L17 V13 J18 U13 J17 C12 K3 B10 M2 B16 G4 D7 T2 C15 G3 B8 P5 C8 P4 D8 P3 E8 P2 B7 R4 C7 R3 B18 B2 C18 C2 D18 D3 E18 D2 D15 G2 B17 E4 D17 E3 E17 E2 E16 F2 B6 T5 B5 U5 C5 U4 D5 U2 B4 V5 C4 V4 B14 H5 B3 V3 C3 V2 C14 H4 D14 H3 E14 H2 B13 J3 C13 J2 C9 N4 D9 N3 D13 J4 D10 M4 C16 F4 D6 T3 D12 K4 C10 M3 D16 F3 C6 T4 U10 M17 D11 L4 U7 R17 U1300 A2 B1 W17 U19 B11 F17 L2 M16 T10 U18 V17 V6 E11 W5 W16 W19 W18 V19 A3 T19 E19 L5 M18 U17 T18 V10 V16 V18 F18 T8 H16 K16 L16 P16 T11 T12 T14 V7 E1 U1 J5 K2 N2 R5 A8 A10 A14 A13 C17 C19 H1 E10 E15 B12 U3 W3 M1 P1 A17 D4 A16 A1 D19 E12 E13 F16 A4 G18 J1 K18 K5 L18 L3 M5 N18 N5 A6 R18 R2 T1 T17 U16 U6 B15 V11 V12 V15 T6 V9 W1 W4 A18 B19 C1 E7 G5 T16 V1 W2 A19 B9 C11 D1 051-9385 A.0.0 13 OF 154 11 OF 39 11 38 39 111234 11 38 39 111234 11 38 39 111234 11 38 39 111234 111234 838 8 38 838 838 838 838 838 1234 838 8 38 8 38 8 38 111234 111234 8 38 8 38 8 38 838 8 38 8 38 8 38 8 38 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 11 38 39 11 38 39 8 38 8 38838 8 38838 838 8 38 838 8 38838 838 838 838 838 838 8 38 8 38 8 38 8 38 8 38 8 38 8 38 838 838 8 38 8 38 8 38 8 38 8 38 113839 113839 838 38 38

- 14. CK_1 DQ13_2 DQ14_2 DQ2_2 DQ1_2 DQ0_2 CKB_2 CKE_2 DQ21_1 DQ12_1 DQ11_1 DQ10_1 DQ0_1 DQ1_1 DQ2_1 DQ3_1 DQ4_1 DQ5_1 CSB_1 CKE_1 CKB_1 CA9_1 CA8_1 CA7_1 CA6_1 CA5_1 CA4_1 CA3_1 CA2_1 CA1_1 CA0_1 DQSB2_1 DQS2_1 DQ20_1 DQ19_1 DQ22_1 DQ23_1 DQ18_1 DQ16_1 DQ17_1 DQ15_1 DQ14_1 DQ13_1 DQ9_1 DQ7_1 DQ8_1 DQ6_1 DQ24_1 DQ31_1 DQ30_1 DQ31_2 DQ29_2 DQ30_2 DQ28_2 DQ26_2 DQ27_2 DQ25_2 DQ24_2 DQ23_2 DQ21_2 DQ22_2 DQ20_2 DQ19_2 DQ18_2 DQ17_2 DQ16_2 DQ15_2 DQ12_2 DQ11_2 DQ10_2 DQ8_2 DQ9_2 DQ6_2 DQ7_2 DQ5_2 DQ4_2 DQ3_2 DQSB3_2 DQS3_2 CA7_2 CA8_2 CA9_2 CK_2 DQS1_2 VREFCA_1 VREFCA_2 VREFDQ_1 VREFDQ_2 2_QZ1_QZ DQSB3_1 DQSB2_2 DQSB1_2DQSB1_1 DQSB0_2DQSB0_1 DQS3_1 DQS2_2 DQS1_1 DQS0_2DQS0_1 DQ29_1 DQ28_1 DQ27_1 DQ26_1 DQ25_1 CA6_2 CA5_2 CA4_2 CA3_2 CA2_2 CA1_2 CA0_2 DM0_1 DM1_1 DM2_1 DM3_1 CSB_2 DM0_2 DM1_2 DM2_2 DM3_2 DDR_1 DDR_2 SYM 1 OF 2 VDD1_3 VDD1_1 VSS55 VSS51 VSS6 VSS49 VSS4 VSS3 VDDQ33 VDDCA1 VDDCA2 VSS46 VDD1_0 VDD1_8 VDD1_5 VDD1_6 VDD1_7 VSS52 VSS0 VSS2 VSS7 VSS9 VSS10 VSS13 VSS18 VSS20 VSS32 VSS33 VSS34 VSS42 VSS43 VSS44 VSS29 VSS28 VSS27 VSS26 VSS25 VSS23 VSS22 VSS47 VSS53 VSS48 VSS50 VSS1 VSS12 VDD1_11 VDD2_3 VDD2_2 VDD1_2 VDD2_6 VDD2_7 VDD2_13 VDD2_14 VDD2_16 VDDQ27 VDDQ32 VDDQ31 VDDQ VDDQ6 VDDQ23 VDDQ30 VDDQ22 VDDQ16 VDDQ34 VDDQ17 VDDQ21 VDDQ19 VDDQ24 VDDQ20 VDDQ28 VDDCA3 VDDCA4 VDDCA5 VDDCA6 VDDCA7 VDDCA8 VDD2_1 VDDQ26 VDDQ25 VSS24 VDD2_9 VDD2_8 VDDQ1 VDD1_9 VDD1_10 VDDCA9 VDDCA10 VDDQ29 VDDQ3 VDD1_4 VDD2_5 VDD2_4 VDD2_15 VSS41 VSS40 VSS39 VSS54 VSS36 VSS35 VDD2_10 VDD2_11 VDD2_12 VSS45 VDD2VDDQVDDCAVDD1 VSS SYM 2 OF 2 Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT 6.3V 402 CERM 1UF 10% 6.3V 1UF CERM 402 10% 20% 0.22UF 0201 6.3V X5R 20% 0.22UF 0201 6.3V X5R 20% 0201 6.3V 0.22UF X5R 20% 6.3V 603 10UF X5R 6.3V NP0-C0G 56PF 5% 01005 6.3V 01005 0.01UF X5R 10% 6.3V 01005 0.01UF X5R 10% 20% 0.22UF 0201 6.3V X5R X5R-CERM 0201 0.01UF 10V 10% 6.3V 01005 0.01UF X5R 10% 6.3V CERM 1UF 402 10% 20% 0.22UF 0201 6.3V X5R 6.3V 1UF CERM 402 10% 20% 0.22UF 0201 6.3V X5R 20% X5R-CERM 4.3UF 4V 0610 6.3V 01005 0.01UF X5R 10% 6.3V 1UF 402 CERM 10% 6.3V 01005 5% 56PF NP0-C0G 6.3V 1UF CERM 402 10% 6.3V 01005 5% NP0-C0G 56PF 20% 0.22UF 0201 6.3V X5R 20% 0.22UF 0201 6.3V X5R 20% 0.22UF 0201 6.3V X5R 20% 0610 4V 4.3UF X5R-CERM 20% 6.3V 10UF 603 X5R 20% 0.22UF 0201 6.3V X5R 20% 6.3V 10UF 603 X5R 6.3V 5% 56PF 01005 NP0-C0G 20% 6.3V 10UF 603 X5R MF 1/20W 1% 240 201 01005 6.3V 0.01UF X5R 10% 01005 6.3V 0.01UF X5R 10% 01005 MF 1/32W 1% 10K 6.3V 01005 0.01UF X5R 10% 01005 MF 1/32W 1% 10K 240 1% 1/20W MF 201 01005 6.3V 0.01UF X5R 10% 01005 6.3V 0.01UF X5R 10% 01005 MF 1/32W 1% 10K 01005 MF 1/32W 1% 10K 20% 0.22UF 0201 6.3V X5R 01005 6.3V 0.01UF X5R 10% 01005 6.3V 0.01UF X5R 10% 01005 6.3V 0.01UF X5R 10% 01005 MF 1/32W 1% 4.7K 01005 MF 1/32W 1% 4.7K 01005 MF 1/32W 1% 4.7K 01005 6.3V 0.01UF X5R 10% 0.22UF 20% 0201 6.3V X5R 01005 MF 1/32W 1% 4.7K BGA XXXMB H4G-DRAM OMIT_TABLE BGA H4G-DRAM XXXMB OMIT_TABLE 20% 0.22UF 0201 6.3V X5R SYNC_MASTER=N/A SYNC_DATE=N/A DDR 2 AND 3 DDR2_CK_P DDR2_CK_N PPVREF_DDR3_DQ VOLTAGE=0.6V MAX_NECK_LENGTH=3 MM MIN_NECK_WIDTH=0.2MM MIN_LINE_WIDTH=0.3MM NET_SPACING_TYPE=PWR =PP1V2_VDDQ_DDR PPVREF_DDR2_DQ MAX_NECK_LENGTH=3 MM VOLTAGE=0.6V MIN_NECK_WIDTH=0.2MM MIN_LINE_WIDTH=0.3MM NET_SPACING_TYPE=PWR =PP1V2_VDDQ_DDR PPVREF_DDR3_CA MIN_NECK_WIDTH=0.2MM VOLTAGE=0.6V MIN_LINE_WIDTH=0.3MM NET_SPACING_TYPE=PWR MAX_NECK_LENGTH=3 MM =PP1V2_S2R_DDR NET_SPACING_TYPE=PWR PPVREF_DDR2_CA MIN_NECK_WIDTH=0.2MM MAX_NECK_LENGTH=3 MM MIN_LINE_WIDTH=0.3MM VOLTAGE=0.6V =PP1V2_S2R_DDR DDR3_ZQ DDR2_ZQ =PP1V2_S2R_DDR DDR3_DQ<11> DDR3_CKE<0> DDR3_CK_P DDR3_CA<7> DDR3_CA<1> DDR3_CA<0> =PP1V2_S2R_DDR =PP1V2_VDDQ_DDR =PP1V8_S2R_DDR DDR2_DM<2> DDR2_DM<3> DDR2_DM<0> DDR2_DM<1> DDR2_CSN<0> DDR3_DM<2> DDR3_DM<3> DDR3_DM<0> DDR3_DM<1> DDR2_CA<0> DDR2_CA<1> DDR2_CA<2> DDR2_CA<3> DDR2_CA<4> DDR2_CA<5> DDR2_CA<6> DDR3_DQ<17> DDR3_DQ<18> DDR3_DQ<19> DDR3_DQ<20> DDR3_DQ<21> DDR3_DQS_P<1> DDR2_DQS_P<1> DDR3_DQS_P<0> DDR2_DQS_P<3> DDR3_DQS_P<2> DDR3_DQS_N<1> DDR2_DQS_N<1> DDR3_DQS_N<0> DDR2_DQS_N<0> DDR2_DQS_N<3> DDR3_DQS_N<2> PPVREF_DDR2_DQPPVREF_DDR3_DQ PPVREF_DDR2_CAPPVREF_DDR3_CA DDR2_DQS_P<0> DDR2_CA<9> DDR2_CA<8> DDR2_CA<7> DDR2_DQS_P<2> DDR2_DQS_N<2> DDR2_DQ<11> DDR2_DQ<12> DDR2_DQ<13> DDR2_DQ<15> DDR2_DQ<14> DDR2_DQ<1> DDR2_DQ<0> DDR2_DQ<2> DDR2_DQ<3> DDR2_DQ<4> DDR2_DQ<7> DDR2_DQ<24> DDR2_DQ<25> DDR2_DQ<26> DDR2_DQ<27> DDR2_DQ<28> DDR2_DQ<30> DDR2_DQ<29> DDR2_DQ<31> DDR2_DQ<16> DDR2_DQ<17> DDR2_DQ<19> DDR2_DQ<18> DDR2_DQ<20> DDR2_DQ<22> DDR2_DQ<21> DDR2_DQ<23> DDR3_DQ<22> DDR3_DQ<23> DDR3_DQ<16> DDR3_DQ<14> DDR3_DQ<0> DDR3_DQ<15> DDR3_DQ<1> DDR3_DQ<5> DDR3_DQ<6> DDR3_DQ<7> DDR3_DQ<25> DDR3_DQ<24> DDR3_DQ<26> DDR3_DQ<31> DDR3_DQ<30> DDR3_DQ<27> DDR3_DQ<28> DDR3_DQS_P<3> DDR3_DQS_N<3> DDR3_CA<2> DDR3_CA<4> DDR3_CA<5> DDR3_CA<9> DDR3_CK_N DDR3_CSN<0> DDR3_DQ<13> DDR3_DQ<12> DDR3_DQ<10> DDR3_DQ<9> DDR3_DQ<8> DDR3_DQ<2> DDR3_DQ<3> DDR3_DQ<4> DDR3_DQ<29> DDR2_CKE<0> DDR2_DQ<8> DDR2_DQ<9> DDR2_DQ<10> DDR2_DQ<6> DDR2_DQ<5> DDR3_CA<8> DDR3_CA<6> DDR3_CA<3> C1405 1 2 C1409 1 2 C14131 2 C1404 1 2 C14081 2 C1412 1 2 C1411 1 2 C1403 1 2 C1402 1 2 C1406 1 2 C14071 2 C1410 1 2 C1401 1 2 C1419 1 2 C1422 1 2 C1431 1 2 C1426 1 2 C1418 1 2 C14171 2 C1425 1 2 C1416 1 2 C14241 2 C1421 1 2 C1430 1 2 C1429 1 2 C1428 1 2 C1435 1 2 C14341 2 C14331 2 C1432 1 2 C1415 1 2 C1414 1 2 C1420 1 2 C14231 2 C1427 1 2 R14211 2 C14601 2 C14501 2 R14051 2 R14061 2 R14201 2 C14611 2 C14521 2 R14511 2 R14521 2 C14621 2 C14541 2 C14631 2 R14531 2 R14541 2 R14551 2 C14561 2 R14561 2 U1400 T15 G16 U15 G17 U14 H17 V14 H18 T13 J16 T9 N16 U9 N17 U8 P17 V8 P18 T7 R16 U12 K17 U11 L17 V13 J18 U13 J17 C12 K3 B10 M2 B16 G4 D7 T2 C15 G3 B8 P5 C8 P4 D8 P3 E8 P2 B7 R4 C7 R3 B18 B2 C18 C2 D18 D3 E18 D2 D15 G2 B17 E4 D17 E3 E17 E2 E16 F2 B6 T5 B5 U5 C5 U4 D5 U2 B4 V5 C4 V4 B14 H5 B3 V3 C3 V2 C14 H4 D14 H3 E14 H2 B13 J3 C13 J2 C9 N4 D9 N3 D13 J4 D10 M4 C16 F4 D6 T3 D12 K4 C10 M3 D16 F3 C6 T4 U10 M17 D11 L4 U7 R17 U1400 A2 B1 W17 U19 B11 F17 L2 M16 T10 U18 V17 V6 E11 W5 W16 W19 W18 V19 A3 T19 E19 L5 M18 U17 T18 V10 V16 V18 F18 T8 H16 K16 L16 P16 T11 T12 T14 V7 E1 U1 J5 K2 N2 R5 A8 A10 A14 A13 C17 C19 H1 E10 E15 B12 U3 W3 M1 P1 A17 D4 A16 A1 D19 E12 E13 F16 A4 G18 J1 K18 K5 L18 L3 M5 N18 N5 A6 R18 R2 T1 T17 U16 U6 B15 V11 V12 V15 T6 V9 W1 W4 A18 B19 C1 E7 G5 T16 V1 W2 A19 B9 C11 D1 051-9385 A.0.0 14 OF 154 12 OF 39 8 38 8 38 12 38 39 111234 12 38 39 111234 12 38 39 111234 12 38 39 111234 38 38 111234 838 838 838 838 838 838 111234 111234 1134 8 38 8 38 8 38 8 38 8 38 838 838 838 838 8 38 8 38 8 38 8 38 8 38 8 38 8 38 838 838 838 838 838 838 8 38 838 8 38 838 838 8 38 838 8 38 8 38 838 12 38 39123839 12 38 39123839 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 8 38 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 838 8 38 8 38 8 38 8 38 8 38 8 38 838 838 838

- 15. TP TP TP TP TP TP TP IN IN IN IN IN IN IN IO0-1 IO7-1 IO6-1 IO3-1 IO4-1 IO5-1 IO1-1 IO2-1 IO7-0 IO5-0 IO6-0 IO4-0 IO2-0 IO3-0 IO1-0 IO0-0 VCC CLE1 CE1* CLE0 CE0* WE0* ALE0 RE0 RE0* DQS0* R/B0* DQS0 ALE1 WE1* RE1 RE1* DQS1 DQS1* R/B1* ZQ VREF VSSQVSS VCCQ VDDI TMSC TCKC IN IN IN IN IN BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI BI TP TP TP TP NC NC NC NC TP Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT DO NOT PLACE IN NAND SINGLE PCS SHIELD CAN AREA TEST POINTS NP0-C0G 25V 0201 27PF 5% 27PF 25V NP0-C0G 0201 5% 25V NP0-C0G 0201 27PF 5% 6.3V 20% 0402-1 CERM-X5R 10UF 20% 0.22UF 6.3V 0201 X5R 20% 6.3V 0402-1 CERM-X5R 10UF 0201 6.3V 20% X5R 0.22UF 5% 27PF 0201 NP0-C0G 25V 5% 27PF 0201 NP0-C0G 25V 6.3V 20% 0402-1 CERM-X5R 10UF 6.3V X5R 0201 0.22UF 20% 27PF NP0-C0G 25V 0201 5% 0.22UF X5R 20% 6.3V 0201 5% 27PF 0201 NP0-C0G 25V 100K MF 01005 5% 1/32W 6 38 6 13 38 6 13 38 6 13 38 6 13 38 6 13 38 6 38 OMIT_TABLE LGA-12X17 XXNM-XGBX8-MLC-PPN1.5-ODP 6 13 38 6 13 38 6 13 38 6 13 38 6 13 38 1/20W 1% 201 MF 243 10UF CERM-X5R 0402-1 20% 6.3V 6.3V 20% 0201 X5R 1UF 10UF CERM-X5R 0402-1 6.3V 20% 10UF CERM-X5R 0402-1 20% 6.3V 6.3V 20% 0201 X5R 1UF X5R 0201 6.3V 0.22UF 20% 0201 6.3V 20% X5R 0.22UF 61338 638 638 638 638 638 638 638 61338 638 638 638 638 638 638 638 4V 20% 01005 X5R 0.1UF 4V 20% 01005 X5R 0.1UF 1/32W 1% 01005 MF 51.1K 1/32W 1% 01005 MF 51.1K 25V NP0-C0G 0201 27PF 5% NP0-C0G 5% 0201 25V 27PF 5% 27PF 0201 NP0-C0G 25V 10UF CERM-X5R 0402-1 20% 6.3V X5R 0201 6.3V 0.22UF 20% 10UF CERM-X5R 0402-1 6.3V 20% CERM-X5R 20% 0402-1 6.3V 10UF 0201 6.3V 20% X5R 0.22UF0.22UF X5R 6.3V 0201 20% SYNC_DATE=N/A NAND SYNC_MASTER=N/A =PP1V8_NAND =PP3V3_NAND FMI1_AD<7> FMI0_RE_L FMI1_AD<6> FMI1_AD<5> FMI1_AD<4> FMI1_AD<3> FMI1_AD<2> FMI1_AD<1> FMI1_AD<0> FMI0_AD<7> FMI0_AD<6> FMI0_AD<5> FMI0_AD<4> FMI0_AD<3> FMI0_AD<2> FMI0_AD<1> FMI0_AD<0> FMI1_DQS FMI1_RE_L FMI1_WE_L FMI1_ALE FMI1_CLE FMI1_CE0_L FMI0_DQS FMI0_WE_L FMI0_ALE FMI0_CLE FMI0_CE0_L TP_FMI_TCKC_U1600 TP_FMI_TMSC_U1600 FMI_ZQ_U1600 NAND_SLOT0_RDYBSY_L FMI_DQVREF_NAND =PP1V8_NAND =PP1V8_NAND FMI1_DQS FMI0_RE_L FMI0_ALE FMI0_AD<0> FMI0_CLE FMI1_WE_L FMI0_DQS FMI1_RE_L FMI1_CLE FMI1_ALE FMI0_WE_L FMI1_AD<0> PPVDDI_NAND_U1600 VOLTAGE=1.2V MIN_LINE_WIDTH=0.2MM MIN_NECK_WIDTH=0.1MM NET_SPACING_TYPE=PWR MAX_NECK_LENGTH=3MM TP16001 TP16011 TP16021 TP16031 TP16051 TP16061 TP16071 TP16081 TP16091 TP16111 R1655 1 2 U1600 C1 D2 A5 C5 A3 C3 H4 F4 M4 K4 G3 G1 H2 J1 J3 L1 K2 N3 L5 N5 K6 L7 J5 J7 H6 G7 E5 E7 B4 C7 D4 D6 OA0 OB0 B6 F2 M6 N1 N7 OC8 OD8 OE0 OF8 G0 OA8 OB8 G5 B2 F6 L3 A7 M2 OC0 OD0 OE8 OF0 G8 E3 E1 A1 R16541 2 C16021 2 C16501 2 C16011 2 C16001 2 C16511 2 C16061 2 C16051 2 C16901 2 C16911 2 R16901 2 R16911 2 TP16131 TP16151 C16071 2 C16081 2 C16091 2 C16121 2 C16221 2 C16111 2 C16101 2 C16211 2 C16201 2 C16321 2 C16311 2 C16301 2 C16151 2 C16251 2 C16141 2 C16241 2 C16341 2 C16351 2 C16131 2 C16231 2 C16331 2 C16041 2 C16521 2 051-9385 A.0.0 16 OF 154 13 OF 39 13 34 34 13 34 13 34 61338 61338 61338 61338 61338 61338 61338 61338 61338 61338 61338 61338

- 16. Apple Inc. THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. 124578 B D 8 7 6 5 4 3 C B A NOTICE OF PROPRIETARY PROPERTY: PAGE 12 D A C PAGE TITLE SHEET IV ALL RIGHTS RESERVED R D SIZEDRAWING NUMBER REVISION BRANCH 6 3 THE POSESSOR AGREES TO THE FOLLOWING: I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART II NOT TO REPRODUCE OR COPY IT WIFI ALIASES SYNC_MASTER=N/A SYNC_DATE=N/A ALIASES GPIO_WLAN_HSIC_DEV_RDY MAKE_BASE=TRUE GPIO_BT_WAKE MAKE_BASE=TRUE MAKE_BASE=TRUEVDDIO_WLAN_BT_1V8 UART3_BT_RTS_L MAKE_BASE=TRUE PMU_GPIO_CLK_32K_WLAN MAKE_BASE=TRUE I2S2_BT_BCLK MAKE_BASE=TRUE I2S2_BT_LRCK MAKE_BASE=TRUE UART4_WLAN_RXD MAKE_BASE=TRUE I2S2_BT_DIN MAKE_BASE=TRUE BT_PCM_IN BT_PCM_OUT UART3_BT_RXD MAKE_BASE=TRUE PP_WL_BT_VDDIO_AP HSIC1_WLAN_STB MAKE_BASE=TRUE GPIO_WLAN_HSIC_HOST_RDY MAKE_BASE=TRUE PMU_GPIO_WLAN_REG_ON MAKE_BASE=TRUE DEV_HSIC3_RDY 50_HSIC_WLAN_STROBE PMU_GPIO_BT_HOST_WAKE MAKE_BASE=TRUE BT_UART_CTS_L BT_PCM_SYNC BT_PCM_CLK BT_UART_RXD BT_REG_ON I2S2_BT_DOUT MAKE_BASE=TRUE PMU_GPIO_BT_REG_ON MAKE_BASE=TRUE PMU_GPIO_WLAN_HOST_WAKE MAKE_BASE=TRUE UART3_BT_TXD MAKE_BASE=TRUE BT_WAKE WLAN_REG_ON HOST_WAKE_WLAN HOST_WAKE_BT UART3_BT_CTS_L MAKE_BASE=TRUE 50_HSIC_WLAN_DATAHSIC1_WLAN_DATA MAKE_BASE=TRUE UART4_WLAN_TXD MAKE_BASE=TRUE WLAN_UART_RXD GPIO_WL_HSIC_RESUME MAKE_BASE=TRUE WLAN_HSIC3_RESUME WLAN_UART_TXD CLK32K_AP BT_UART_RTS_L BT_UART_TXD AP_HSIC3_RDY 051-9385 A.0.0 21 OF 154 14 OF 39 536 5 34 536 3036 536 536 536 536 27 27 536 27 436 536 30 27 27 30 27 27 27 27 27 536 30 30 536 27 27 27 27 536 27436 536 27 5 27 27 27 27 27 27