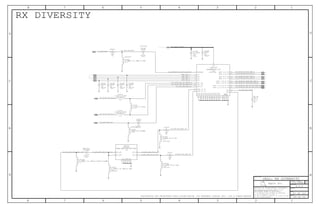

The document contains detailed specifications and part numbers for electronic components and printed circuit boards (PCBs) related to Apple Inc. It includes various codes and identifiers relevant to production and design, emphasizing the proprietary nature of the information. Additionally, the document specifies confidentiality instructions for its possession and handling.

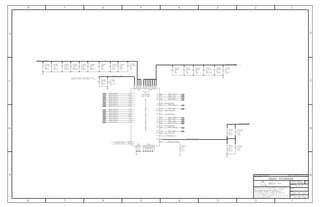

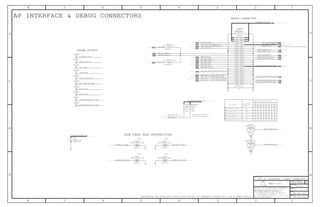

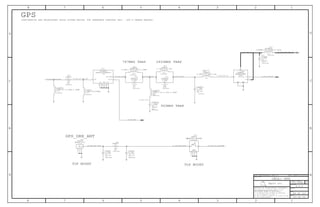

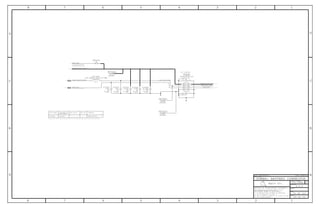

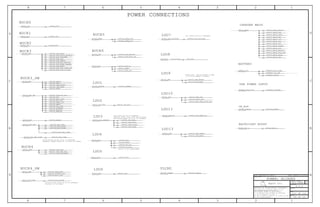

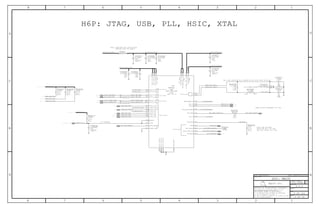

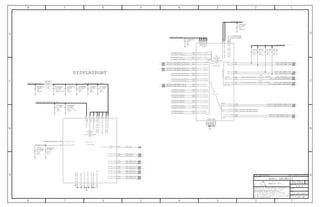

![OUT

CLK

RESET

DETGND

GND

GND

GND

GND

GND

I/O

DETECT

VCC VPP

OUT

BIIN

IN

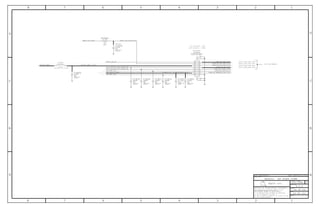

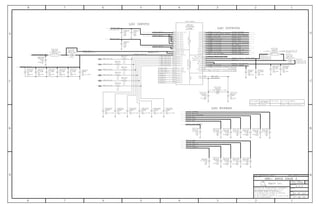

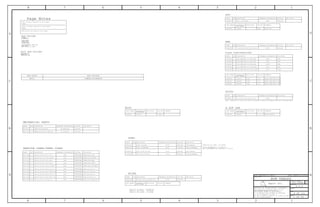

SCHEMATIC DEFINED CONSTRAINTS (YES/NO)

CKPLUS RULE EXCEPTIONS

TABLE_DASHBOARD_INFO

REQUIRED

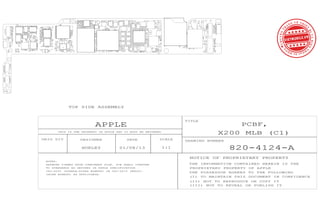

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZEDRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

EVT101

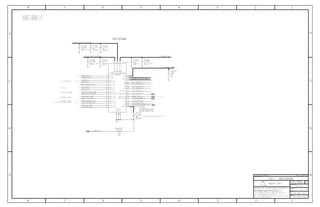

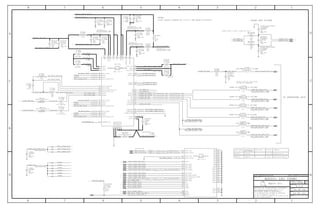

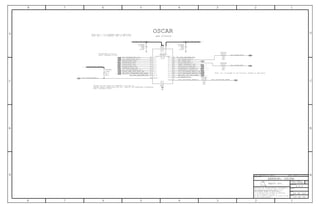

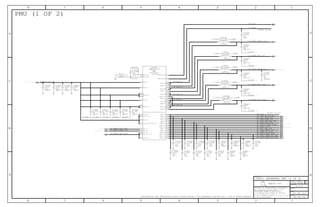

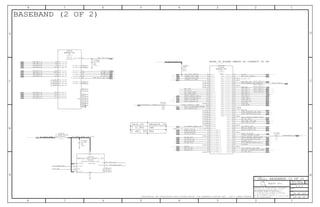

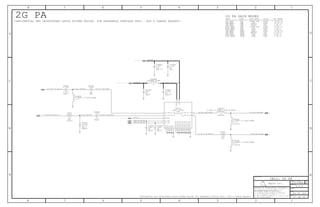

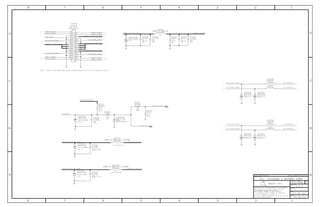

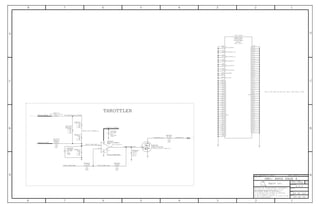

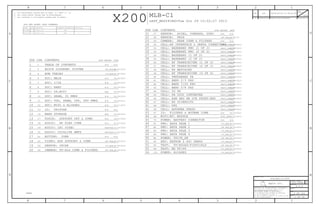

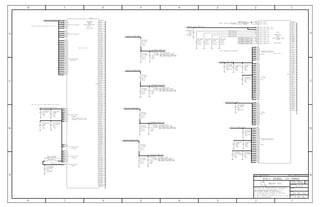

BOARD_ID[1]

MLB_C

SIM CARD

SPI0 TEST MODE

MLB

BOARD REVISION

S/W READ FLOW

2. DISABLE PU AND ENABLE PD

1. SET GPIO AS INPUT

BOARD_ID[0]

ID[3-0] SYSTEM

1. SET GPIO AS INPUT

BOOT_CONFIG[3-0]

2. DISABLE PU AND ENABLE PD

BOOT_CONFIG[3] (GPIO29)

S/W READ FLOW

BOOT_CONFIG[0] (GPIO18)

BOOT_CONFIG[2] (GPIO28)

BOARD ID

3. READ

BOARD_ID[3]

BOARD_ID[2]

BRD_REV[2-0]

3. READ

1. SET GPIO AS INPUT

S/W READ FLOW

3. READ

BOOT_CONFIG[1] (GPIO25)

BOOT CONFIG ID

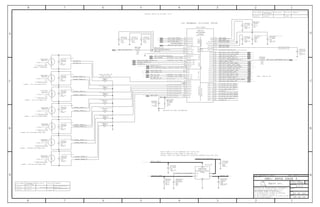

1010 J85 AP

1011 J85 DEV

1100 J86 AP

1101 J86 DEV

1110 J87 AP

1111 J87 DEV

MLB_B

0000

0010

JTAG

SPI0

0011

0001

2. ENABLE PU AND DISABLE PD

NAND <-- SELECTED

NAND TEST MODE

ID_J85_J87

2.2K

5%

01005

1/32W

MF

R1205

01005

5%

MF

1/32W

2.2K

R1201

NOSTUFFNOSTUFF

2.2K

1/32W

5%

R1200

MF

01005 01005

5%

2.2K

1/32W

MF

R1203

NOSTUFF

MF

1/32W

2.2K

5%

R1206

ID_DEV

01005

ID_J86_J87

5%

2.2K

01005

1/32W

MF

R1204

R1260

5%

100

MF

1/32W

01005

01005

1/32W

2.2K

5%

MF

R1213

4 52

100

5%

1/32W

MF

01005

R1210

01005

R1250

0%

0.00

1/32W

MF

NOSTUFF

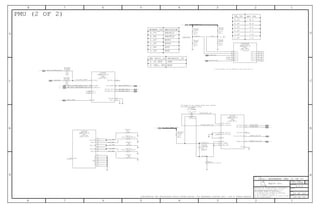

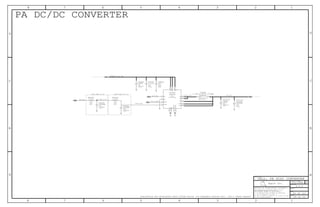

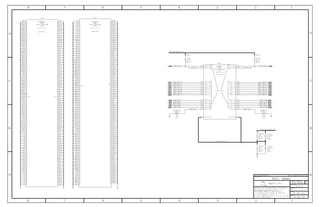

SIM-CARD-X113-X223

F-ST-SM

CELL

J3000

24 28 52

24 28 52242852

242852

C3002

CELL

CERM

6.3V

5%

100PF

01005

01005

MF

1/32W

1%

CELL

15.00K

R3000

C3001

0402

X5R

10%

16V

1.0UF

CELL

01005

MF

1/32W

5%

2.2K

R1202

1/32W

5%

100

R1211

01005

MF

NOSTUFF

2.2K

01005

5%

MF

R1207

1/32W

2.2K

MF

5%

R1208

01005

1/32W

NOSTUFF

5%

2.2K

01005

1/32W

MF

R1209

NO

SYNC_DATE=04/11/2011SYNC_MASTER=N/A

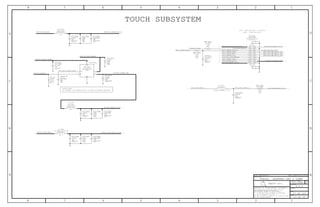

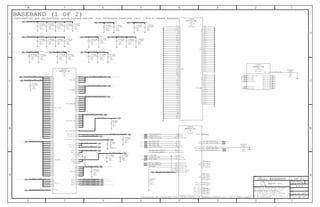

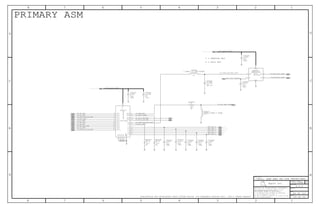

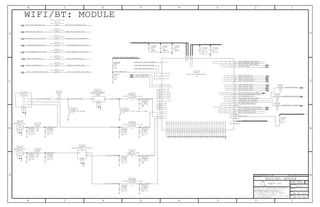

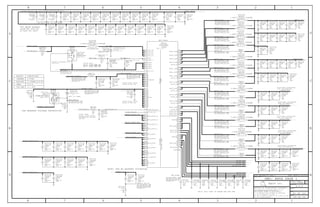

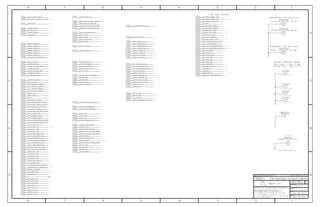

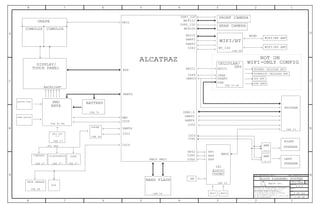

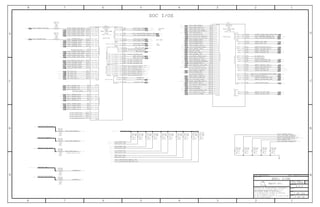

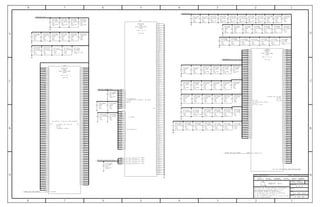

SOC: MISC & ALIASES

GPIO_BOOT_CONFIG2

SIMCRD_CLK_CONN

SIMCRD_RST_CONN

PP_LDO6_RUIM_1V8

NC_J3000_5

SIMCRD_IO_CONN

SIM_TRAY_DETECT

MAKE_BASE=TRUE

WDOG_SOC WDOG_SOC2PMU_RESET_IN

MAKE_BASE=TRUE

I2S3_BT2SOC_DATA I2S4_BT2SOC_DATA

I2S3_SOC2BT_DATA

MAKE_BASE=TRUE

I2S4_SOC2BT_DATA

I2S3_SOC2BT_BCLK

MAKE_BASE=TRUE

I2S4_SOC2BT_BCLK

I2S3_SOC2BT_LRCK

MAKE_BASE=TRUE

I2S4_SOC2BT_LRCK

RESET_SOC_LJTAG_SOC_TRST_L

JTAG_SOC_SEL

GPIO_BOARD_ID1

GPIO_BOARD_REV1

SOC_FAST_SCAN_CLK

GPIO_BOARD_ID2

GPIO_BOARD_REV2

GPIO_BOOT_CONFIG3

GPIO_BOARD_REV0

GPIO_BOARD_ID3

SOC_HOLD_RESET

SOC_TESTMODE

=PP1V8_SOC

=PP1V8_SOC

GPIO_BOARD_ID0

GPIO_BOOT_CONFIG0

GPIO_BOOT_CONFIG1

051-0886

A.0.0

12 OF 121

10 OF 54

1

2

1

2

1

2

1

2

1

2

1

2

1 2

1

2

1

2

1 2

3

2

8

11

10

12

4

9

6

7

1

5

2

1

1

2

2

1

1

2 1

2

1

2

1

2

1

2

5

24252752

4 48

5 44

5 44

5 44

5 44

4 8 11 24 48 52452

5

5

4

5

5

5

5

5

4

4 52

457101854

457101854

5

5

5](https://image.slidesharecdn.com/ipadmini2fullschematicdiagram-180315105329/85/iPad-mini-2-full-schematic-diagram-11-320.jpg)