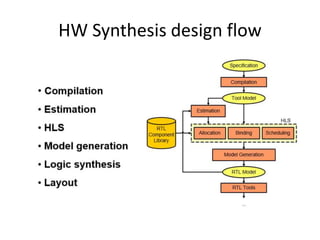

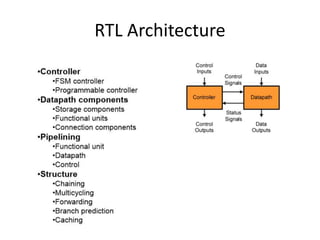

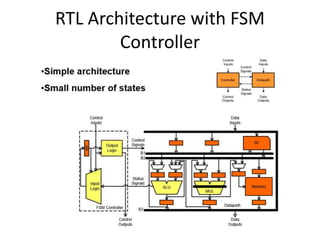

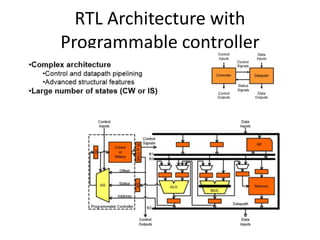

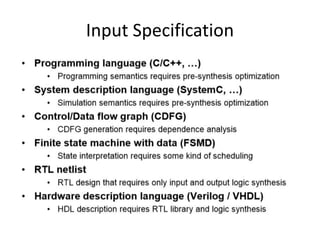

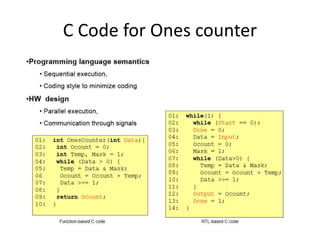

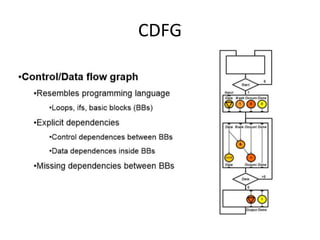

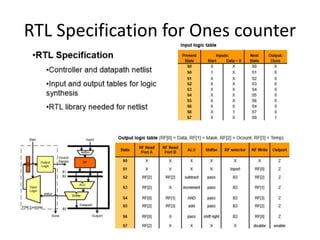

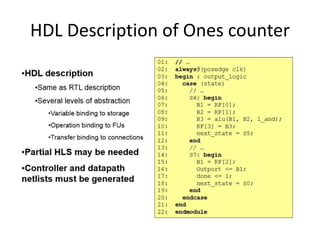

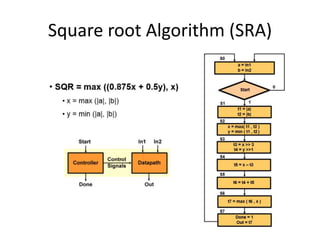

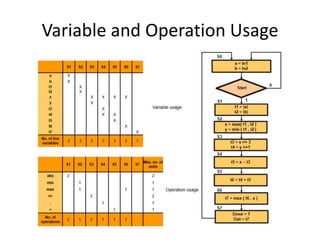

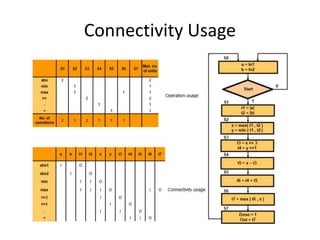

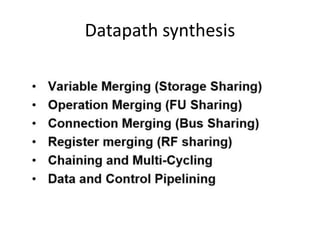

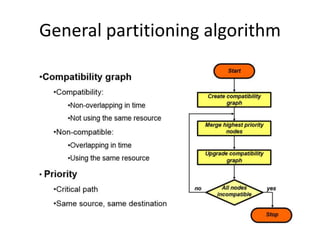

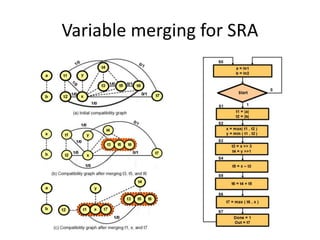

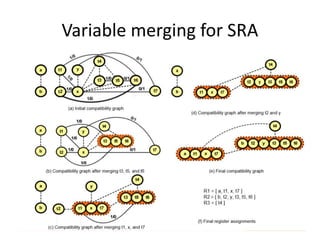

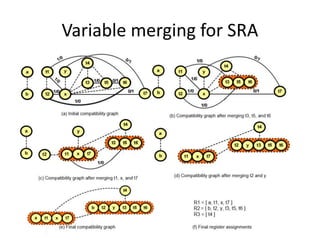

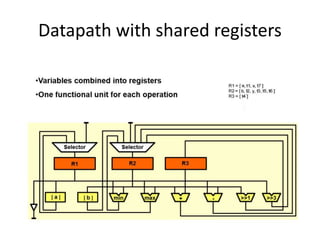

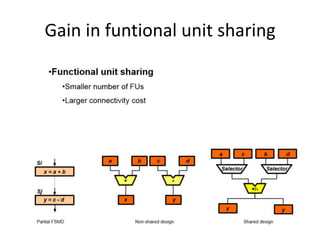

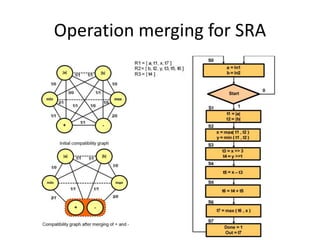

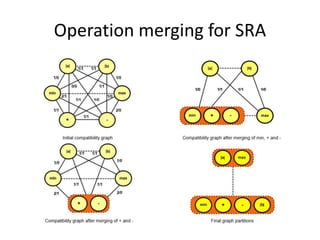

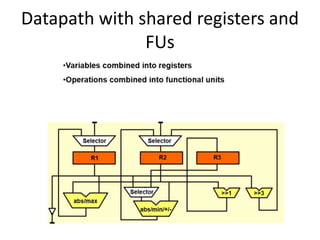

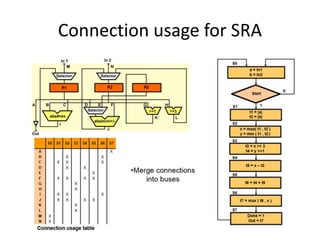

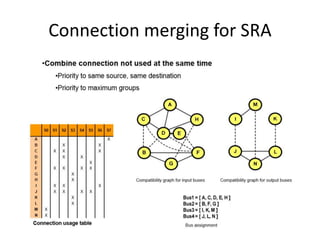

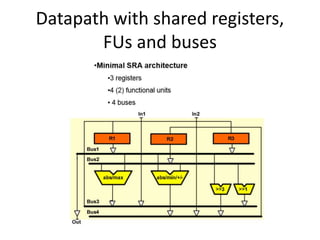

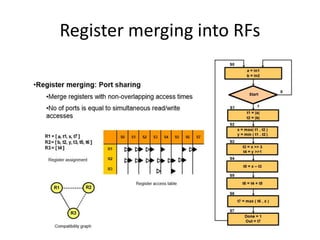

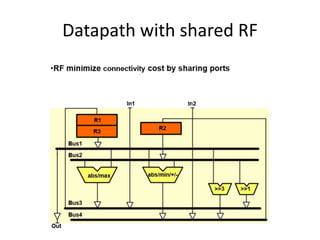

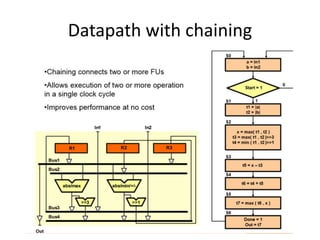

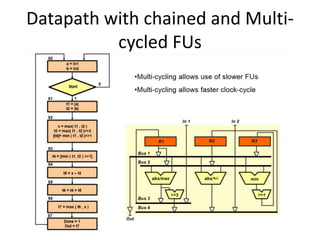

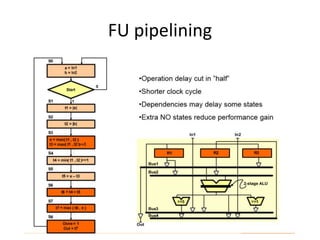

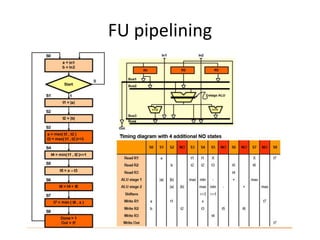

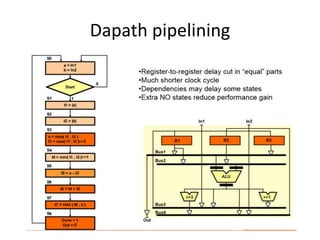

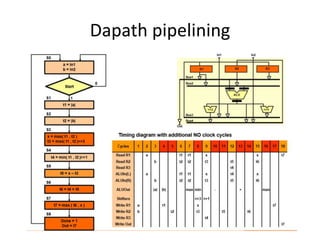

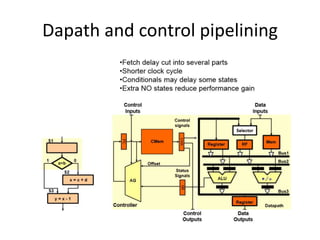

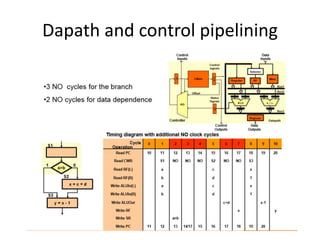

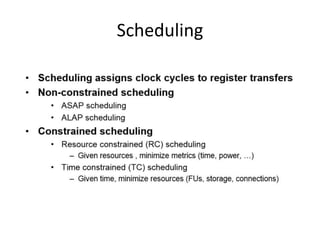

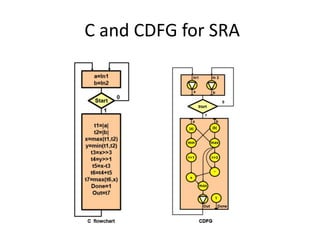

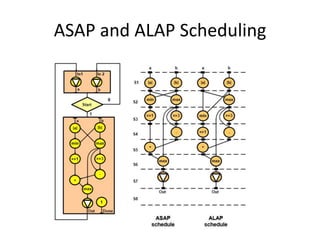

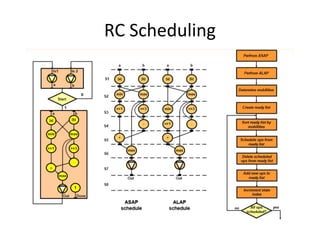

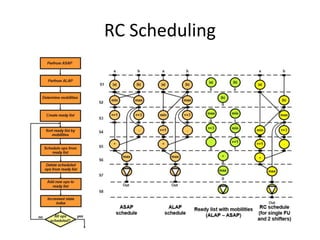

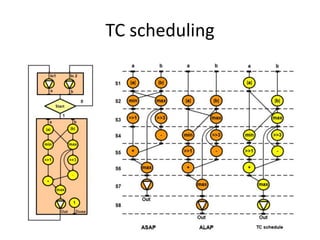

The document outlines hardware synthesis design processes, focusing on RTL architecture with optimizations like variable and operation merging, register sharing, and pipelining techniques. It discusses scheduling algorithms and emphasizes the need for system-level design to manage growing complexities in technology. Future work includes exploring timed transaction-level modeling (TLM), incorporating RTOS models, and synthesizing designs for FPGA prototyping.