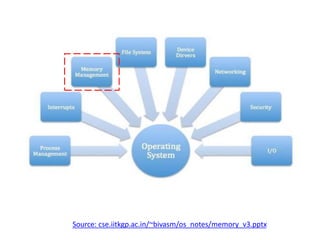

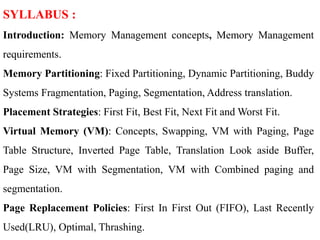

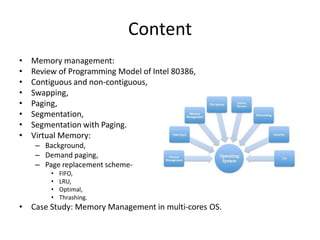

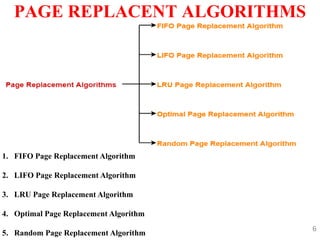

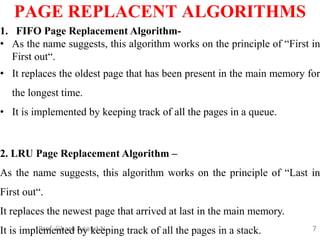

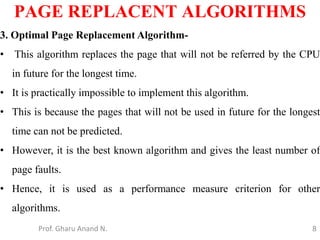

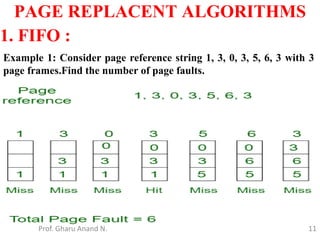

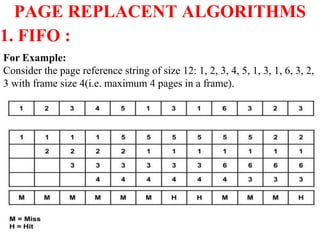

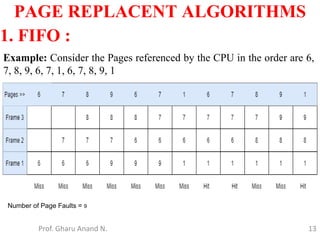

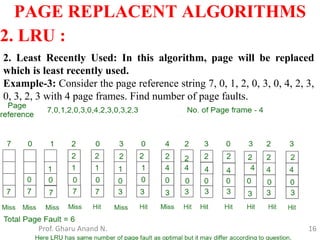

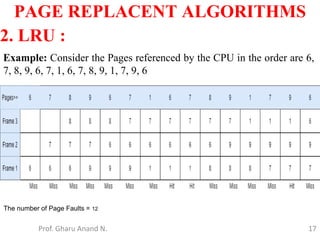

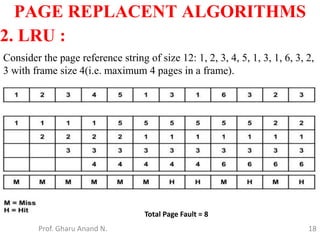

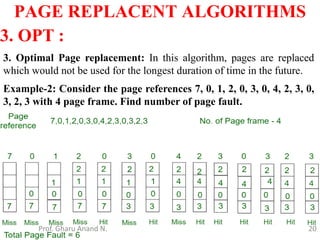

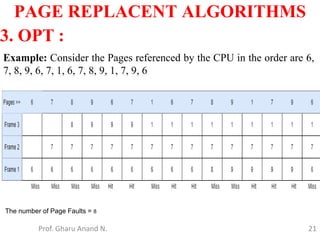

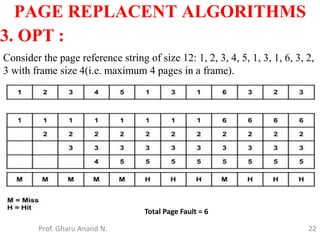

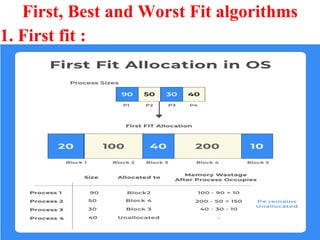

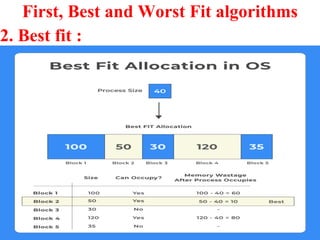

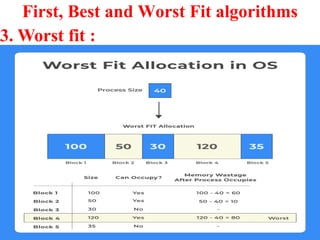

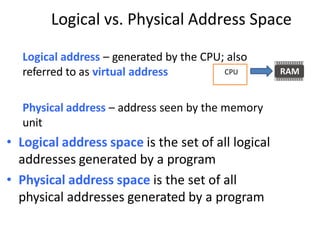

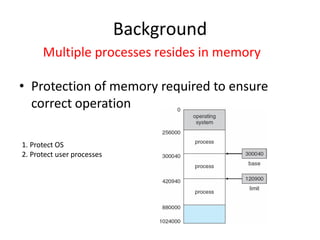

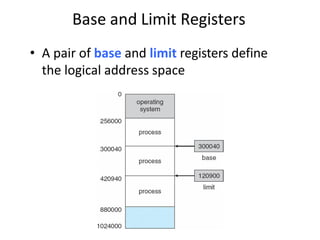

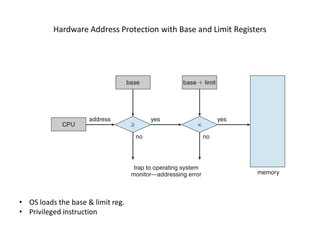

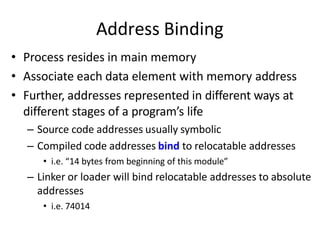

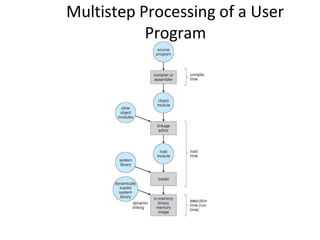

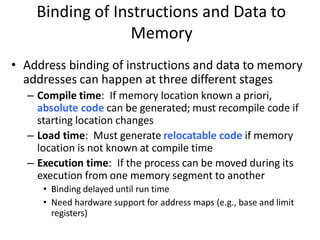

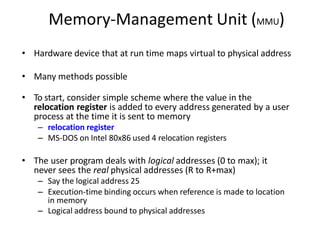

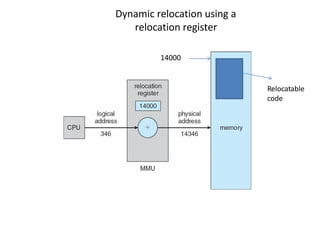

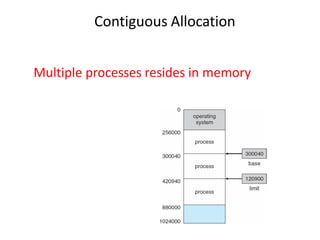

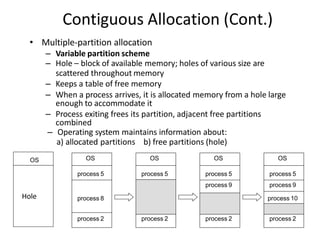

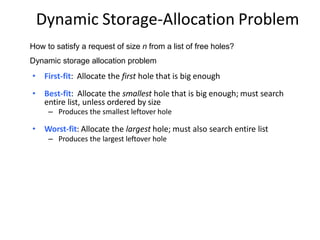

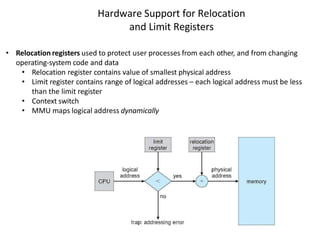

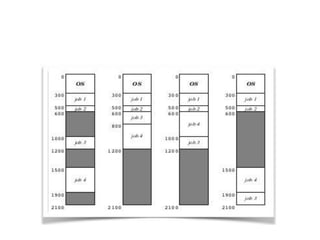

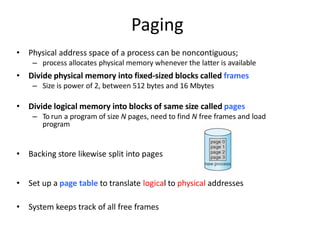

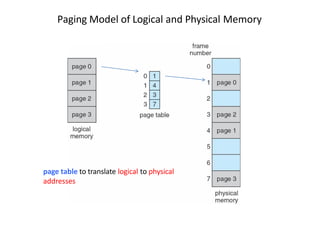

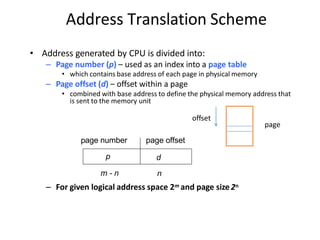

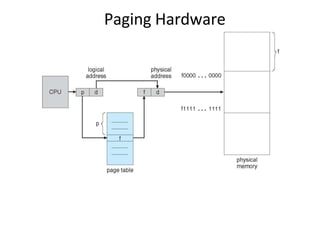

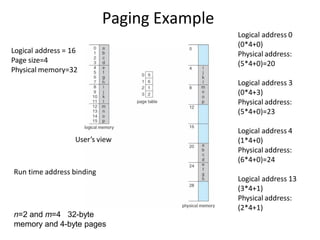

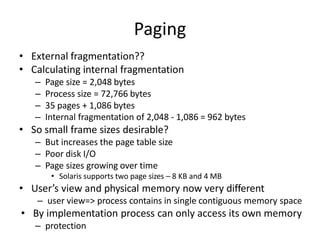

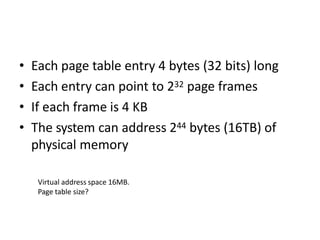

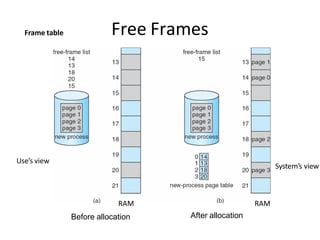

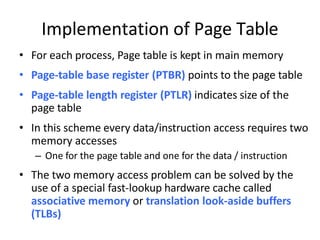

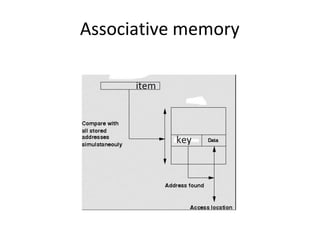

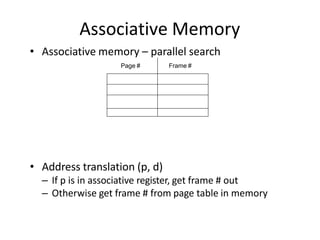

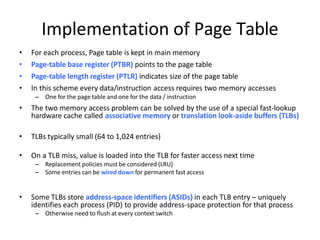

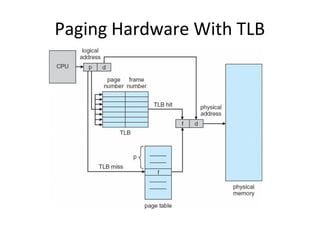

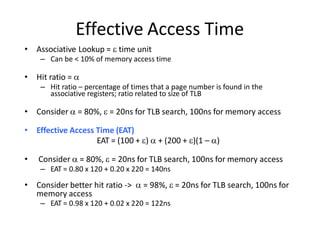

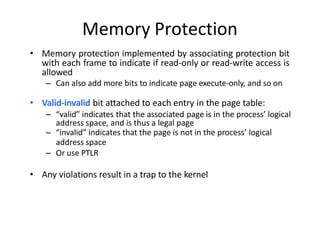

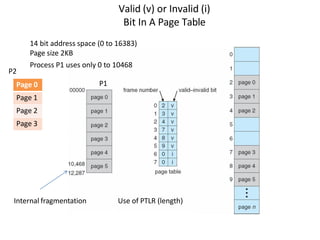

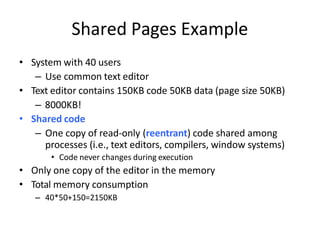

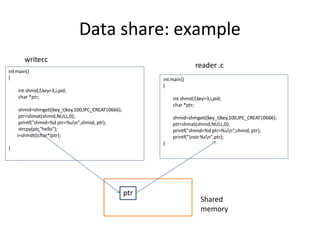

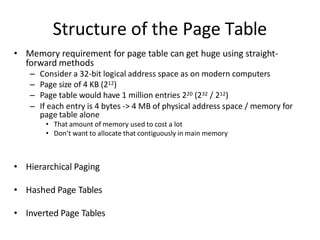

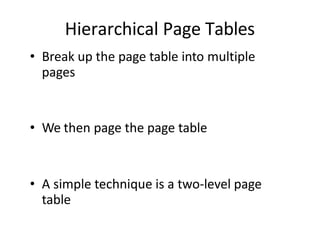

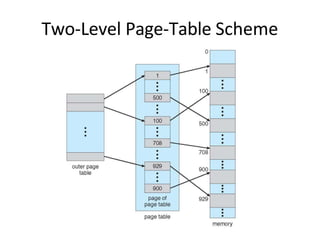

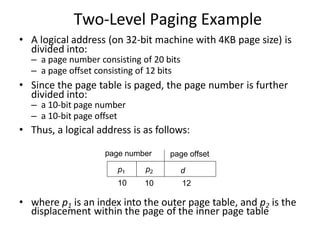

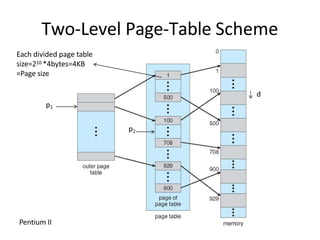

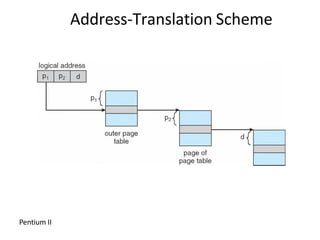

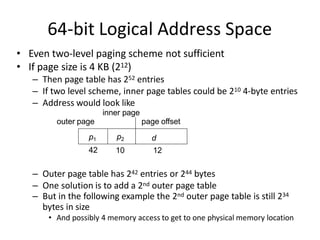

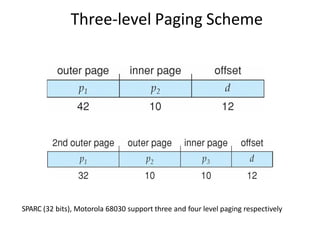

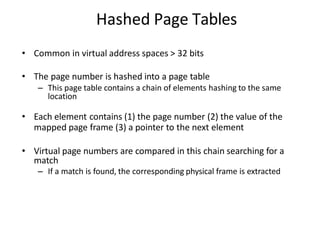

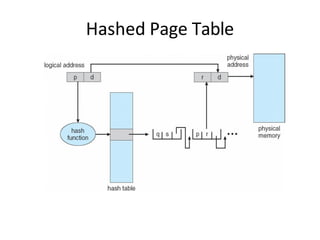

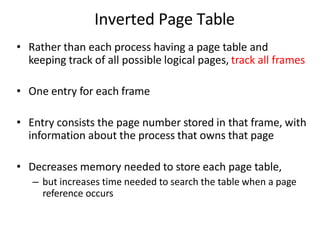

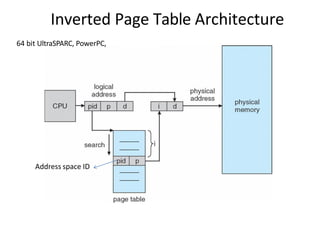

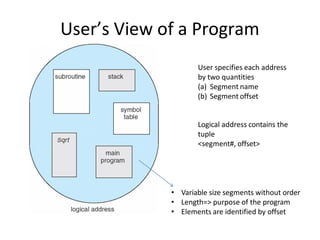

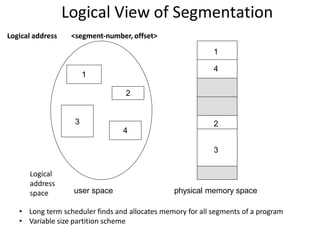

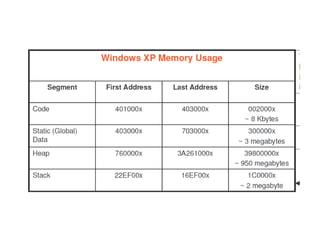

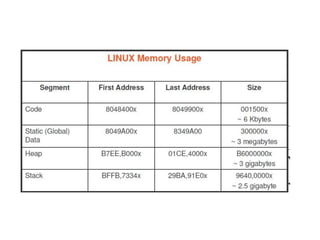

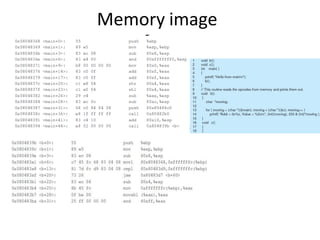

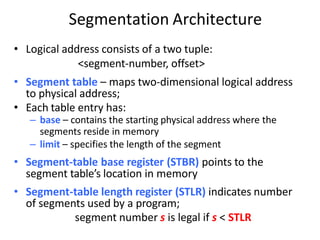

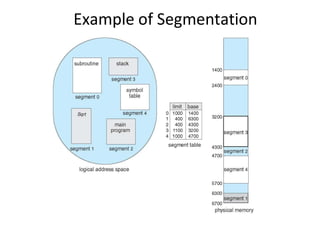

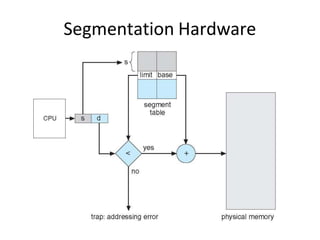

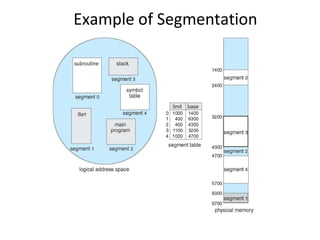

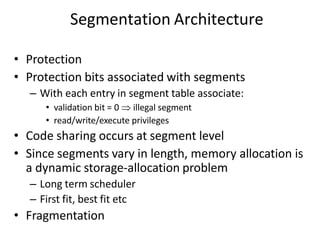

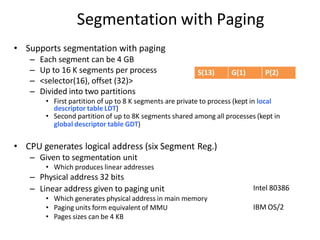

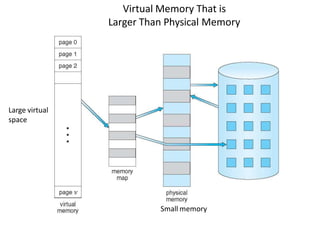

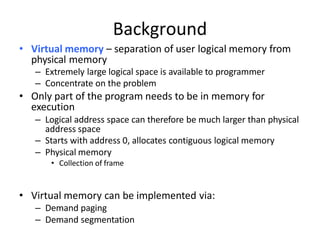

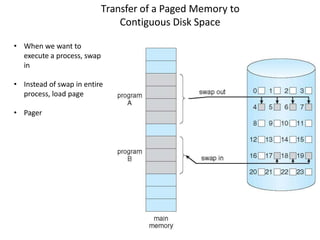

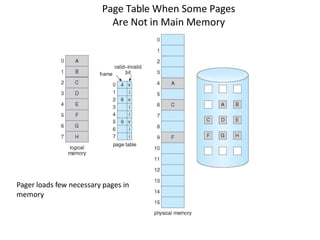

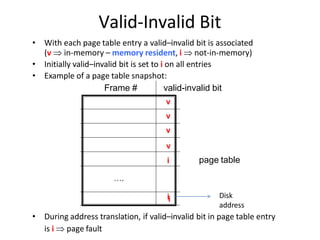

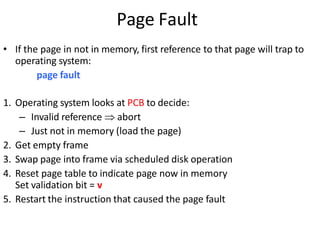

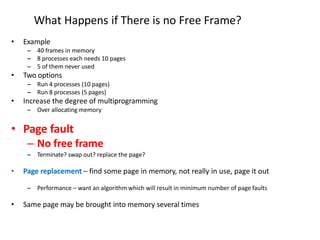

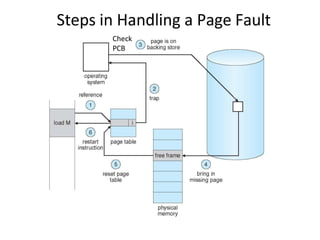

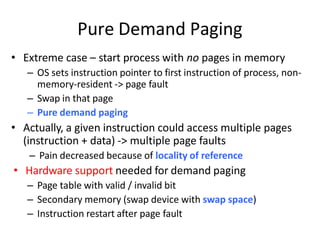

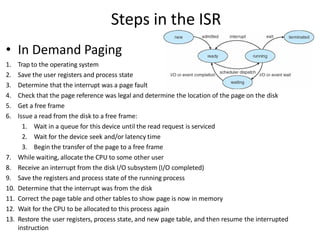

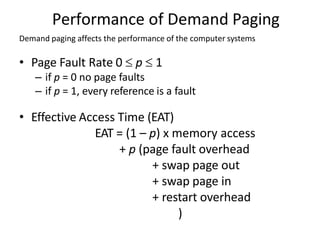

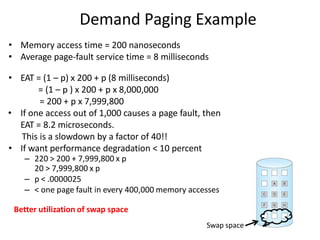

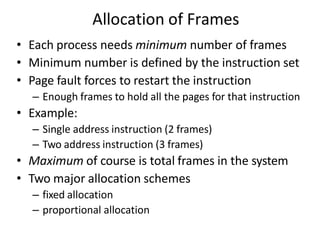

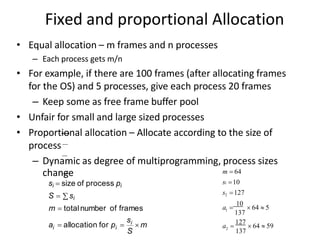

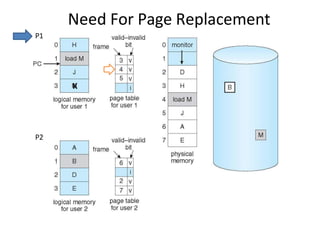

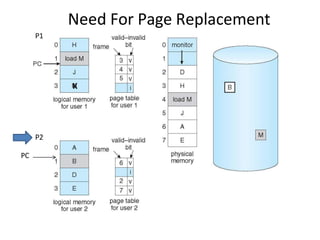

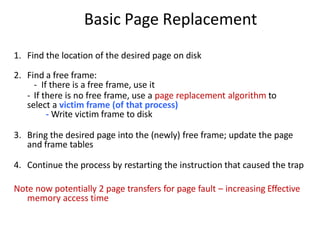

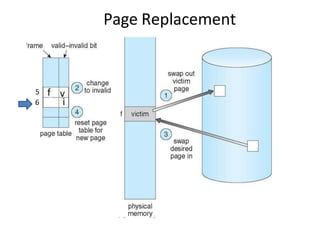

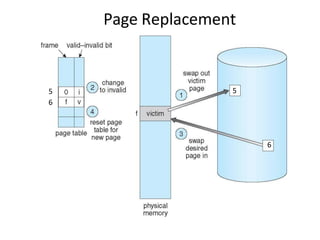

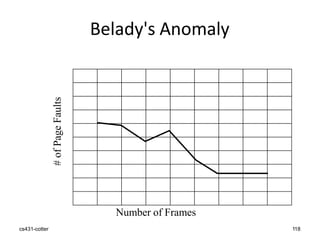

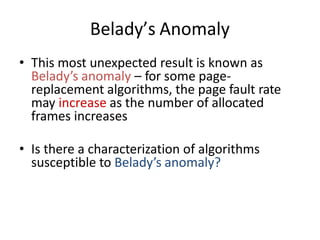

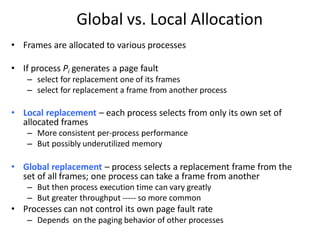

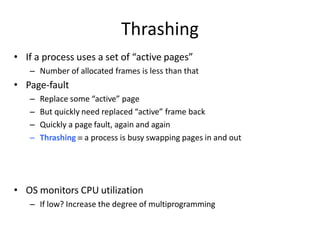

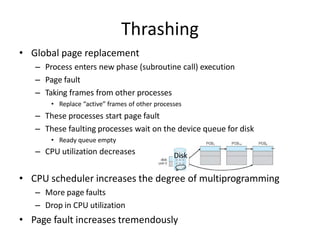

The document focuses on memory management in operating systems, covering concepts such as memory partitioning, virtual memory, and various page replacement algorithms like FIFO, LRU, and optimal. It discusses techniques for process memory allocation including first fit, best fit, and worst fit strategies. The material also includes practical examples and addresses fragmentation issues, both external and internal, in the context of memory management.