1) The document outlines the steps for setting up the Cadence design environment and using Cadence tools for VLSI simulation and layout, including creating a library and cells, schematic capture, simulation, and layout.

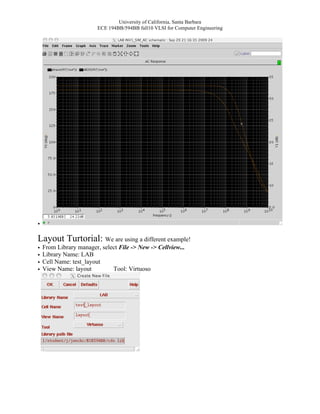

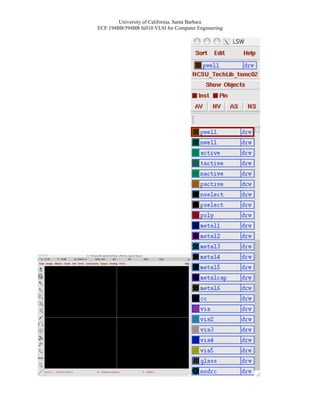

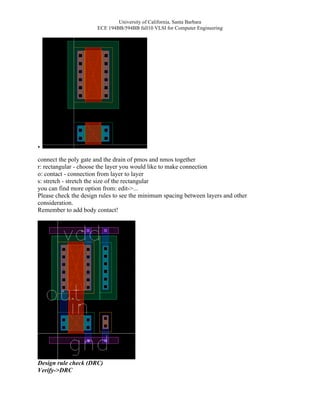

2) Key steps covered include making a new library and cells, inserting symbols and setting properties, adding I/O ports, saving schematics, hierarchical editing, simulation setup and running DC and AC analyses, and layout steps like inserting layout components and design rule checking.

3) The document provides a tutorial on using Cadence for both analog circuit simulation and layout design for a VLSI computer engineering course.