This document describes a cache memory simulation project. It includes a system overview with specifications, descriptions of main components like memory cells, muxes, and comparators. It also covers the final system layout, testing procedures, and conclusions. The cache uses a direct mapped replacement policy and stores 8-bit data with 4-bit tags at each memory address. System implementation and testing were successful with some minor geometric errors found during design rule checking.

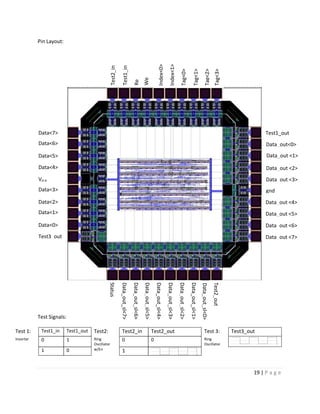

![System Diagram:

Tag_In Line_In Data_In

4bits 2bit 8bit We

Tag Line Data F2

Tag Data

Re

Demux

4 bits

Tag Data

4 bits

Tag Data

Tag Data

Comparator

Demux

4 bits

F1

32 bits

4 bits

Mux

2 bits

8 bits

Status Data_Out

Specification:

Data width: 8-bit

Tag: 4-bit

Address: 4-bit

Index 2-bit

Replacement Policy: Direct Mapped Cache Fill

Perform the following functions:

Operation Read_en Write_en Status Data Out

Read-Hit 1 X 1 Mem[index]

Read-Miss 1 X 0 Previous Data

Write-Hit 0 1 X X

Write-Miss 0 1 X X

2|P a ge](https://image.slidesharecdn.com/cache-120302001940-phpapp01/85/Cache-3-320.jpg)

![Inputs:

From CPU:

New Data: 8-bit

Address: 6-bit

Address<5:2> Tag: 4-bit

Address<1:0> Index: 2-bit

Read enable: 1-bit

Write enable: 1-bit

Outputs:

To CPU:

Dataout: 8-bit

Status: 1-bit [Signifies when data is ready]

Total pins required: 25pins + 1 Vdd + 1 gnd.

Extra outputs:

Ring Oscillator Test Signal: 1-bit

Ring Oscillator Test Signal w/En: 2-bits

Inverter: 2-bits

Replacement Algorithm: Direct Mapped Cache Fill

This is the fastest algorithm for cache replacement where the cache takes 2 least significant bits of the

address as index. It essentially takes the main memory address and indexes the address by using

modulus.

3|P a ge](https://image.slidesharecdn.com/cache-120302001940-phpapp01/85/Cache-4-320.jpg)