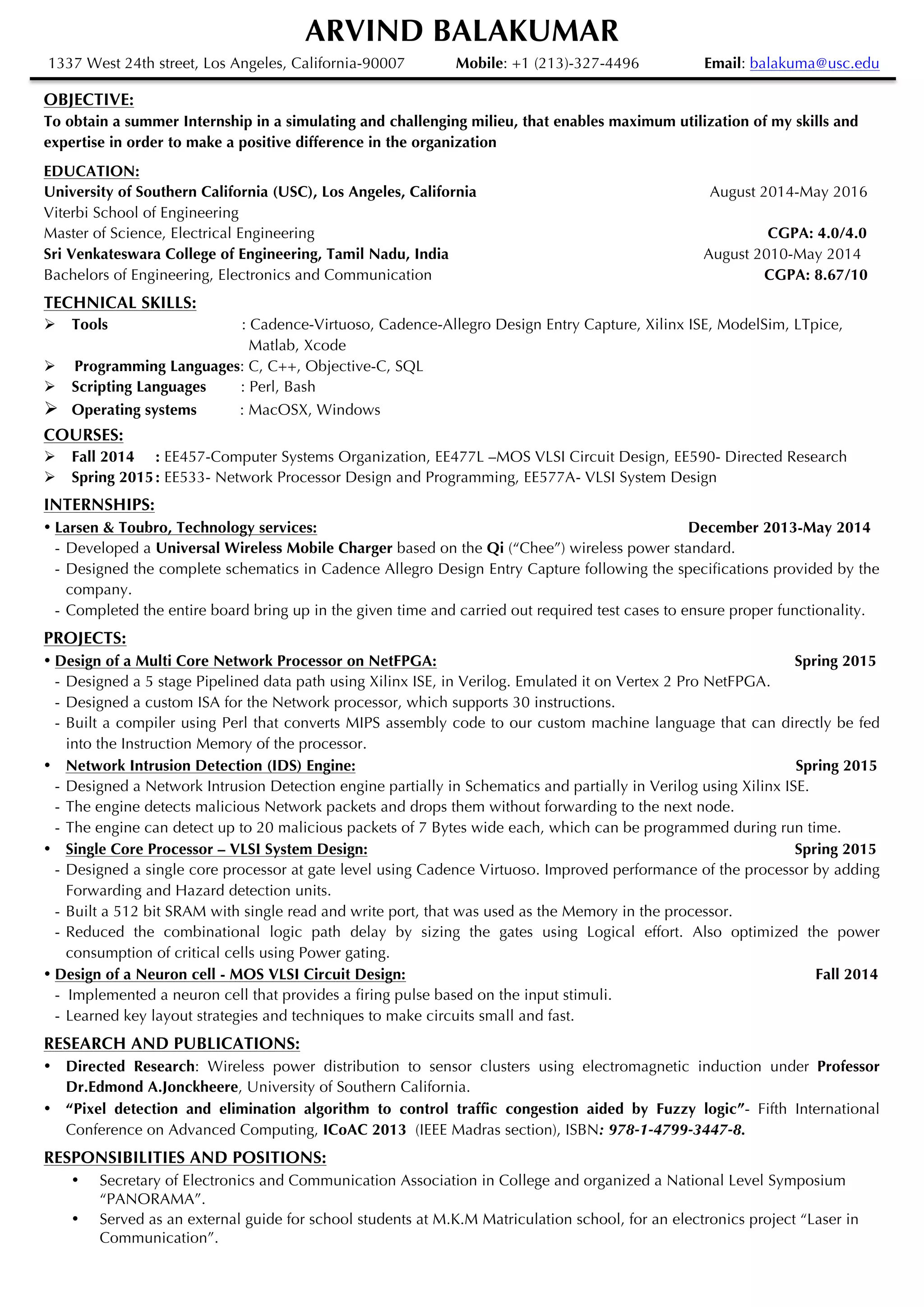

Arvind Balakumar is seeking a summer internship and has relevant experience and skills. He has a Master's degree in Electrical Engineering from USC and a Bachelor's degree from Sri Venkateswara College of Engineering. His technical skills include tools like Cadence and programming languages like C/C++. He has taken courses in computer systems organization, VLSI circuit design, and network processor design. His past internship and projects involved designing circuits and processors. He has research experience in wireless power distribution and published a paper on traffic congestion control using fuzzy logic.