1. Introduction

The exponential growth of semiconductor technology has led to highly complex integrated circuits (ICs) with billions of transistors. While the ability to fabricate such advanced chips is a testament to modern technology, ensuring their correct operation after manufacturing is an equally critical challenge. Manufacturing test principles are applied to detect faults that may occur during the fabrication process, ensuring that only properly functioning chips are delivered to customers. These tests are essential for quality assurance, yield improvement, and customer satisfaction.

The primary goal of manufacturing testing is to identify defective chips before they are shipped, ideally with minimal cost and testing time. This paper presents a comprehensive overview of the principles and practices involved in manufacturing testing, including fault models, test strategies, design for testability (DFT), test pattern generation, and emerging trends.

2. Importance of Manufacturing Testing

Manufacturing testing plays a vital role in the semiconductor industry due to the following reasons:

High Cost of Failure: A single faulty chip can cause failure in critical systems such as medical devices, avionics, or automotive control systems.

Complexity of ICs: As device complexity increases, the probability of defects in each chip also rises.

High Production Volumes: Millions of chips are fabricated in a single batch, making automated and reliable testing essential.

Yield Improvement: Manufacturing testing helps identify recurring fault patterns that can be traced back to process issues.

3. Types of Manufacturing Tests

Manufacturing tests are typically classified into various categories depending on the phase of testing and the type of fault targeted.

3.1 Wafer-Level Testing

Performed while chips are still on the wafer.

Probes are used to make contact with bonding pads.

Only basic functional or parametric tests are done.

3.2 Package-Level Testing

Conducted after the wafer is diced and chips are packaged.

Allows more comprehensive testing due to full electrical access.

3.3 System-Level Testing

Performed after the chip is integrated into a board or system.

Verifies system-level functionality and performance.

4. Fault Models in Manufacturing Testing

Fault models provide a simplified representation of physical defects that may occur in a circuit. They help in generating test patterns and analyzing fault coverage.

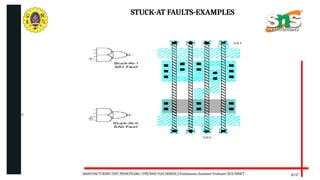

4.1 Stuck-at Fault Model

Assumes a line is permanently stuck at logic ‘0’ or ‘1’.

Simple and widely used for combinational and sequential circuits.

4.2 Bridging Fault Model

Assumes that two signal lines are unintentionally connected.

Can result in logic conflicts depending on the states of the signals.

4.3 Open Circuit Fault Model

A connection is broken, resulting in a floating signal.

Difficult to detect, as behavior depends on circuit loading and capacitance.

4.4 Delay Fault Model

Faults that affect the timing rather than