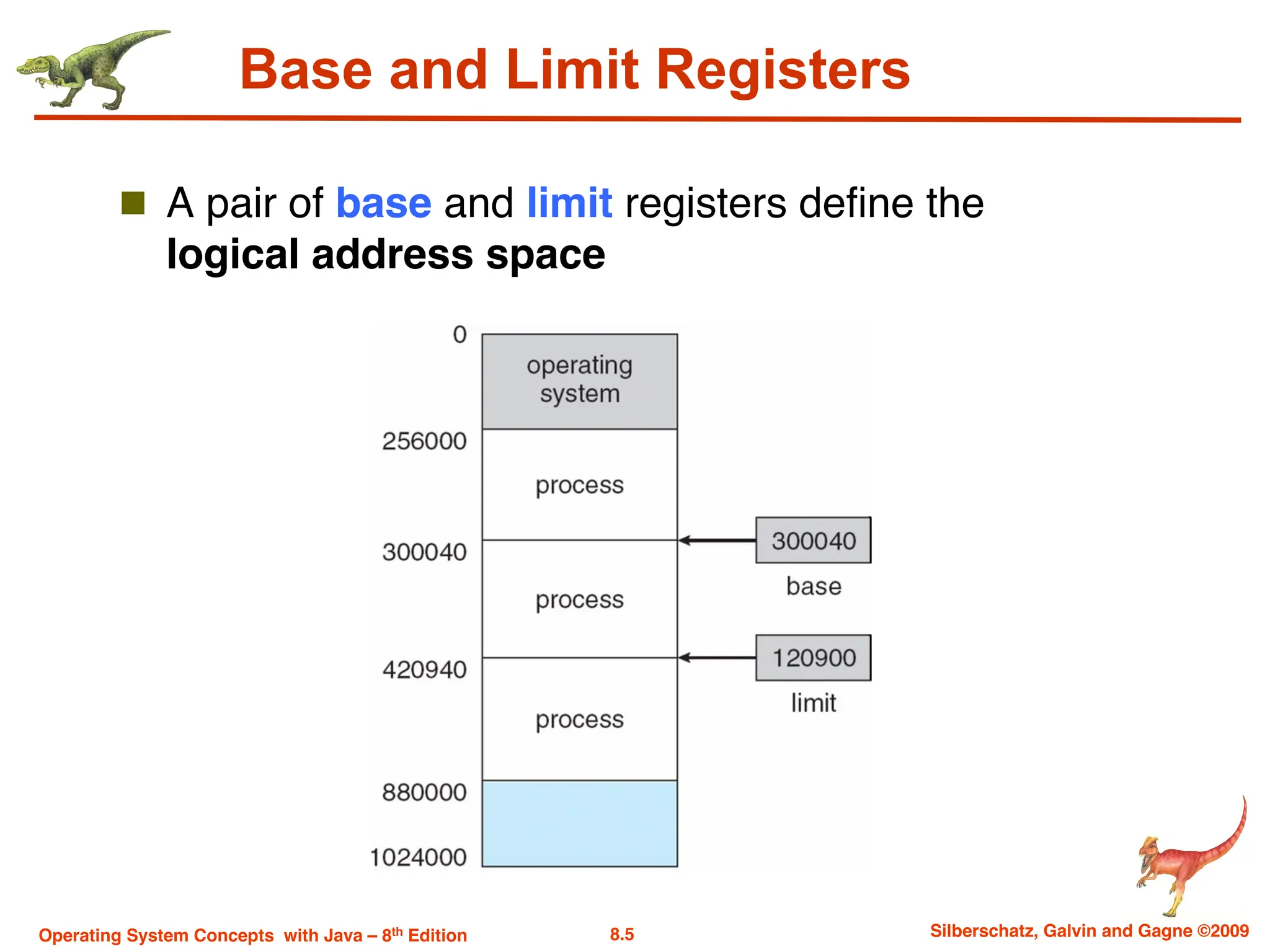

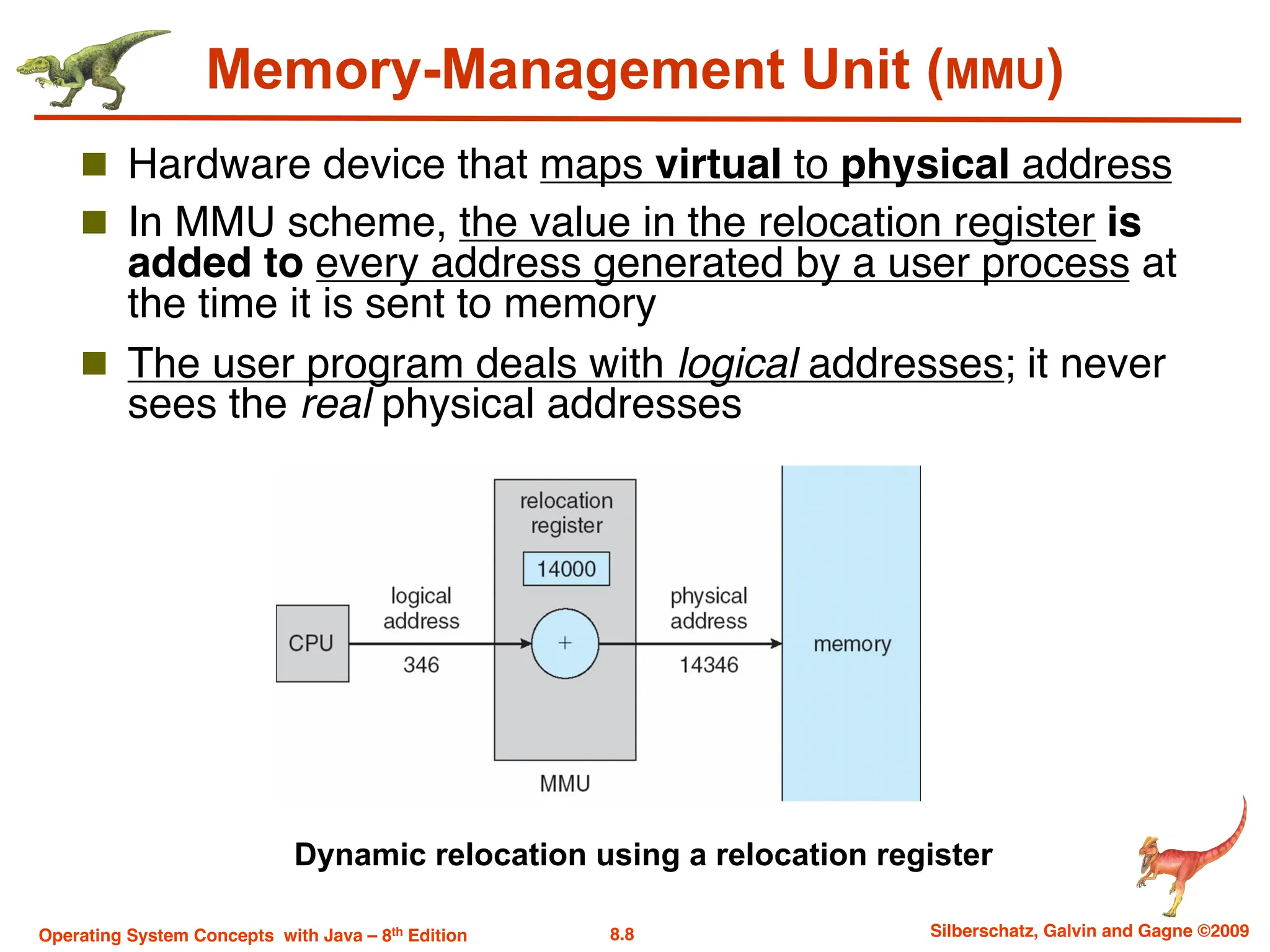

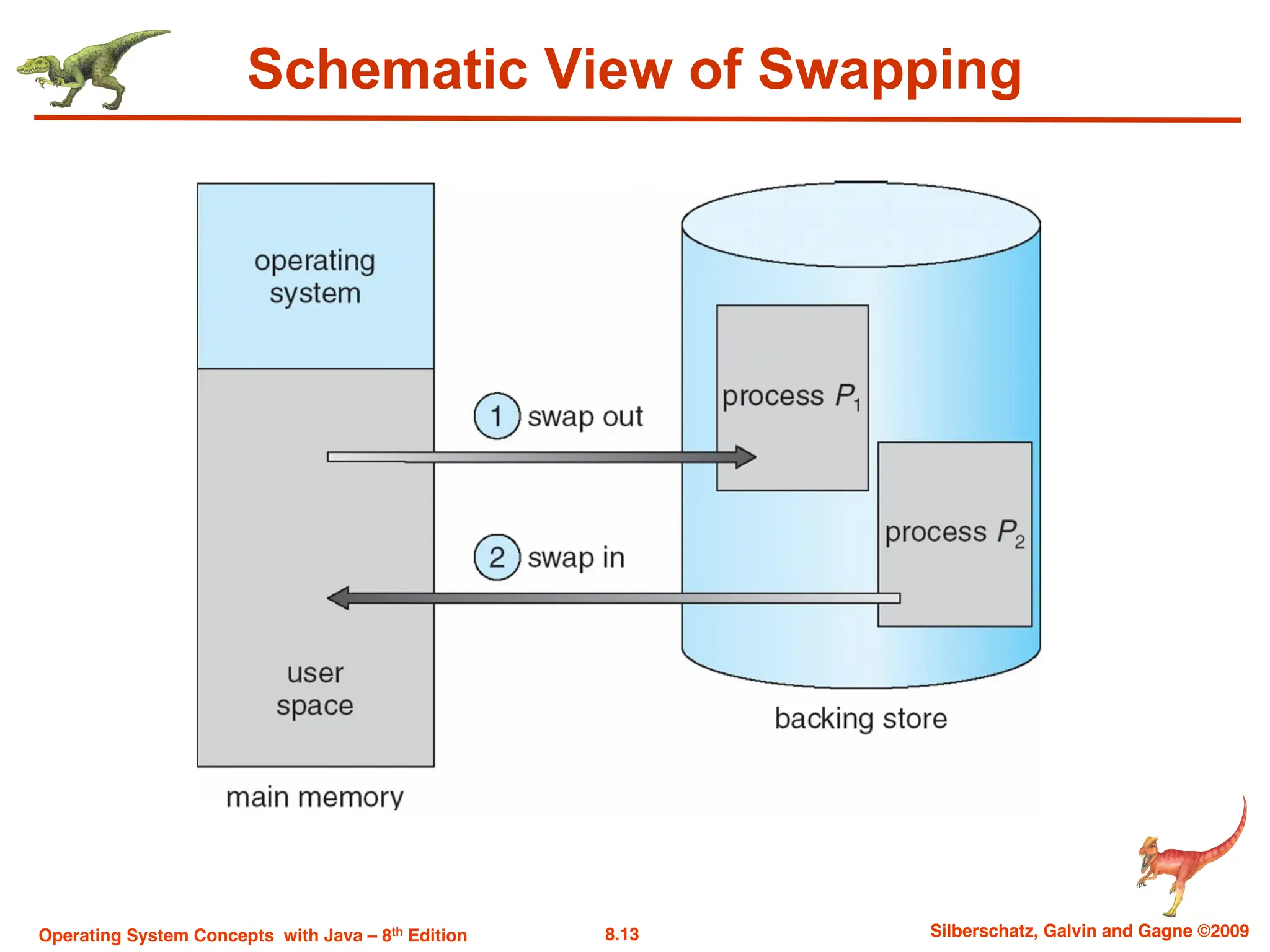

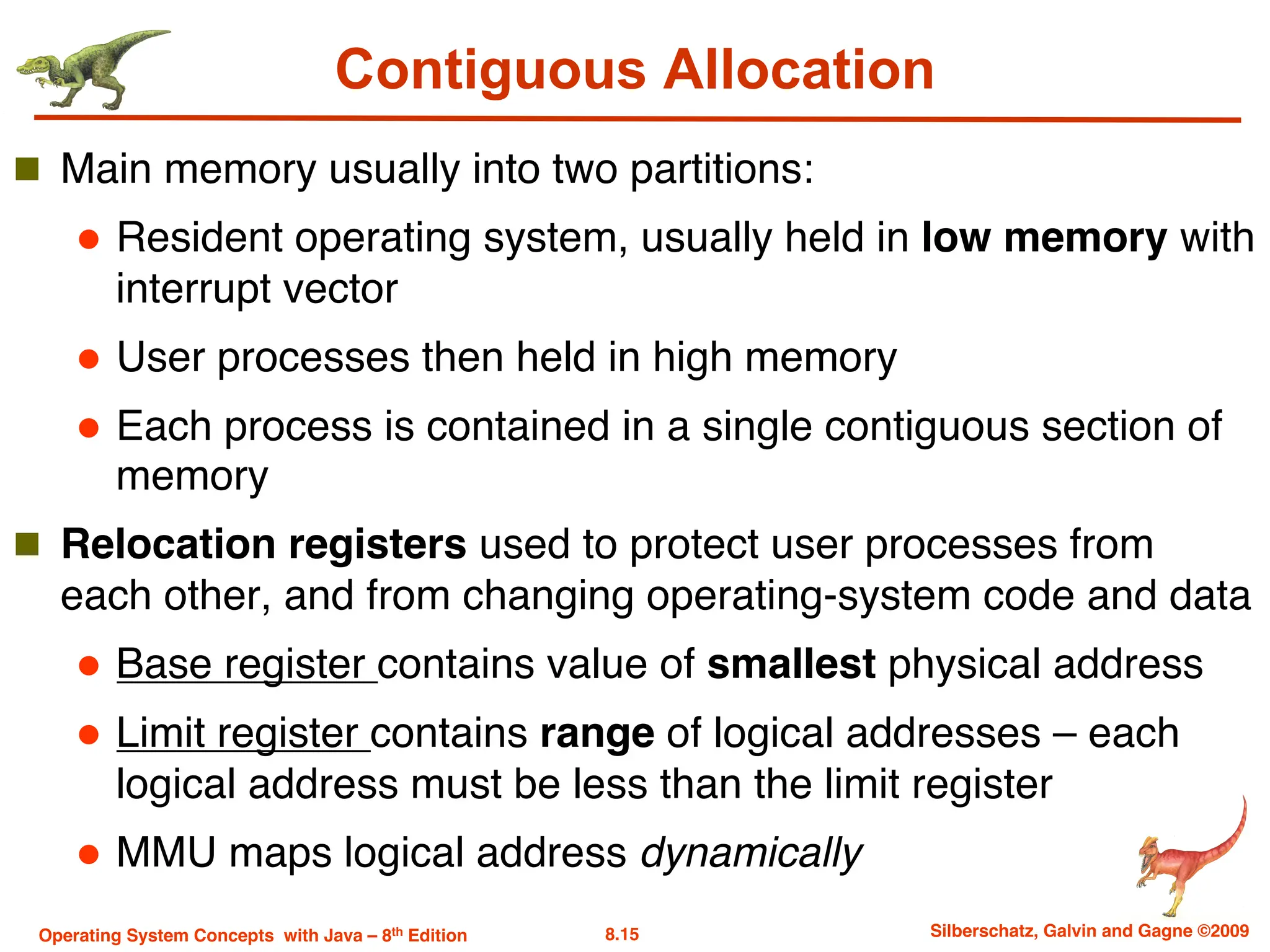

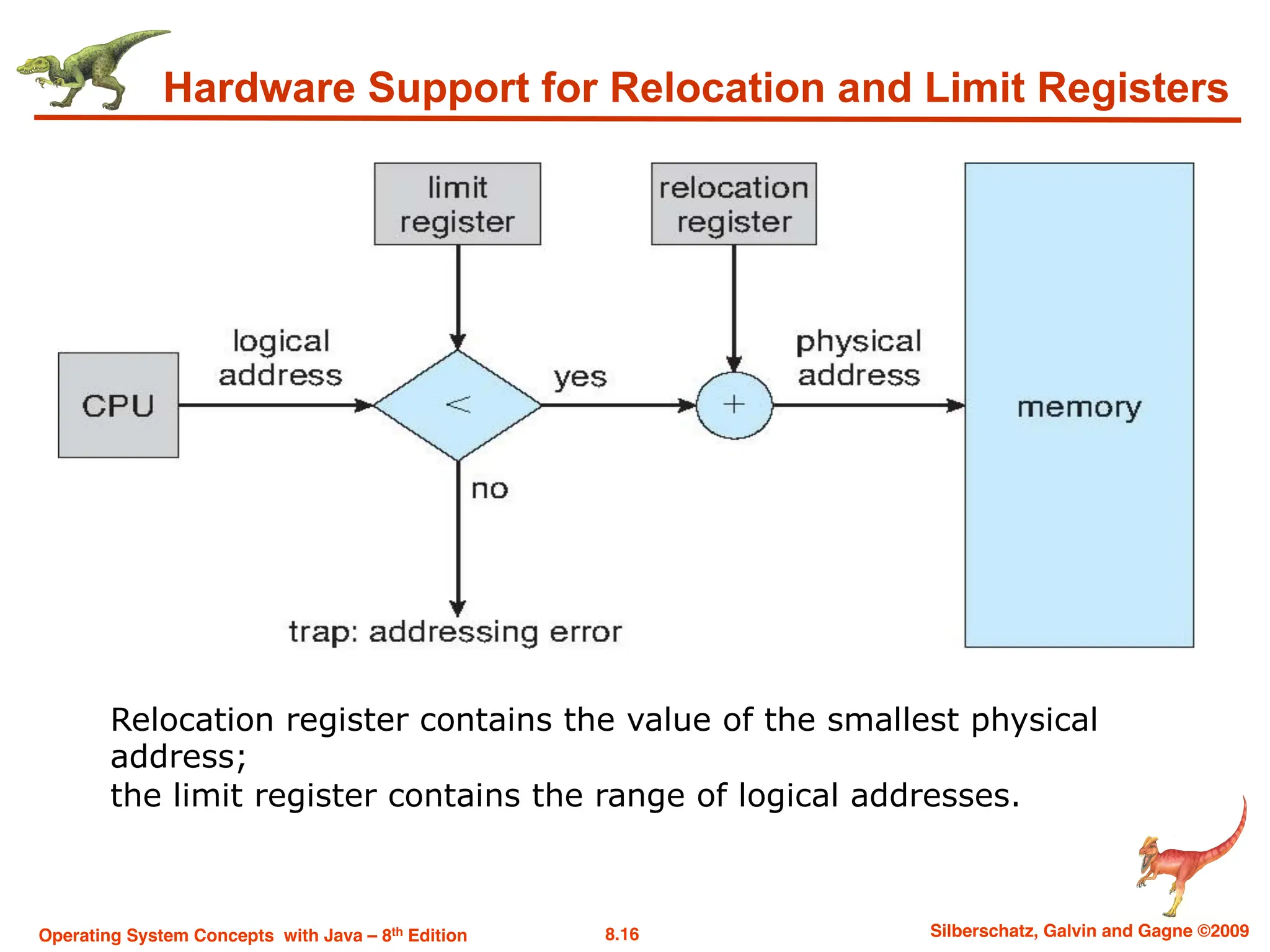

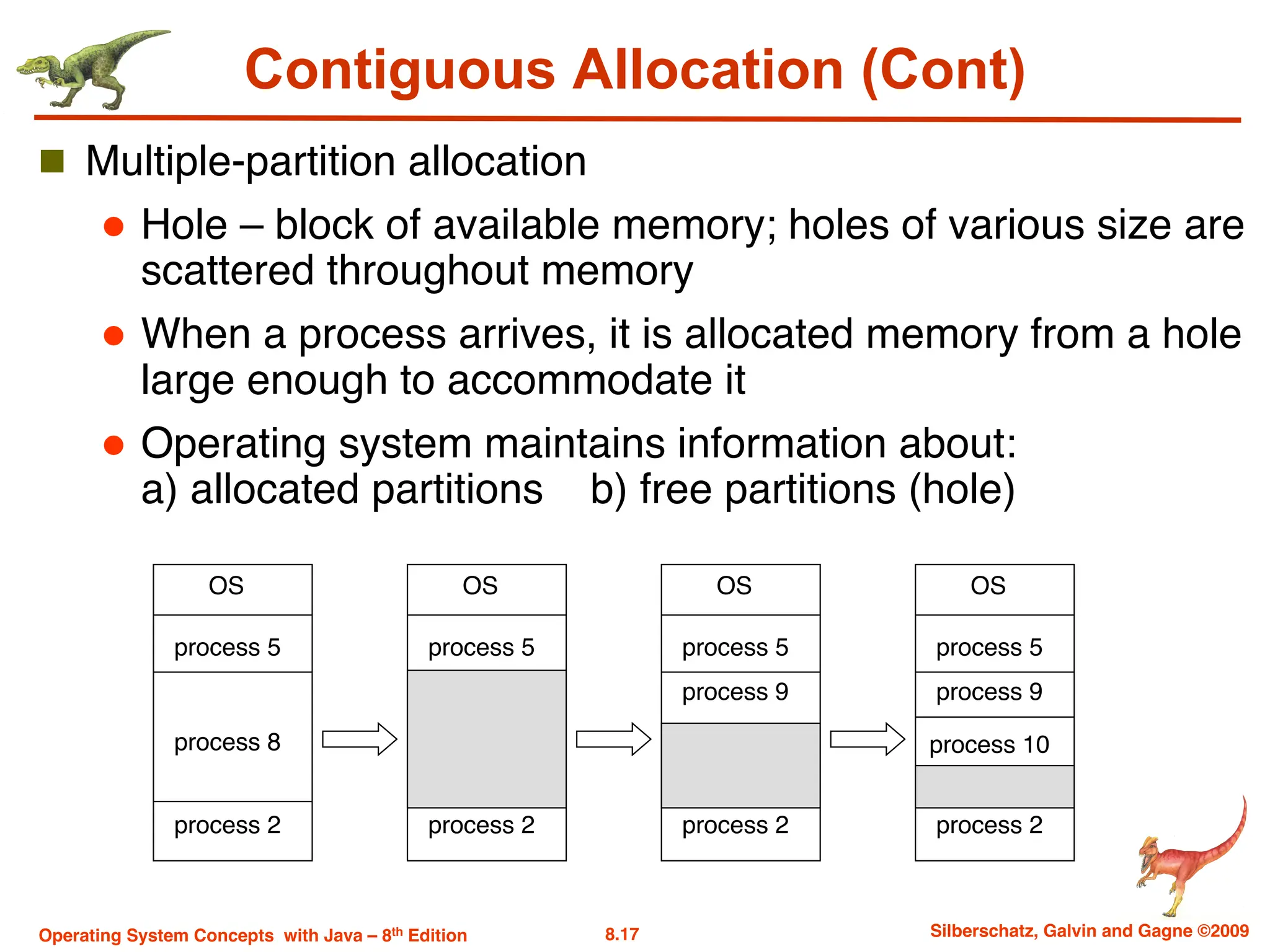

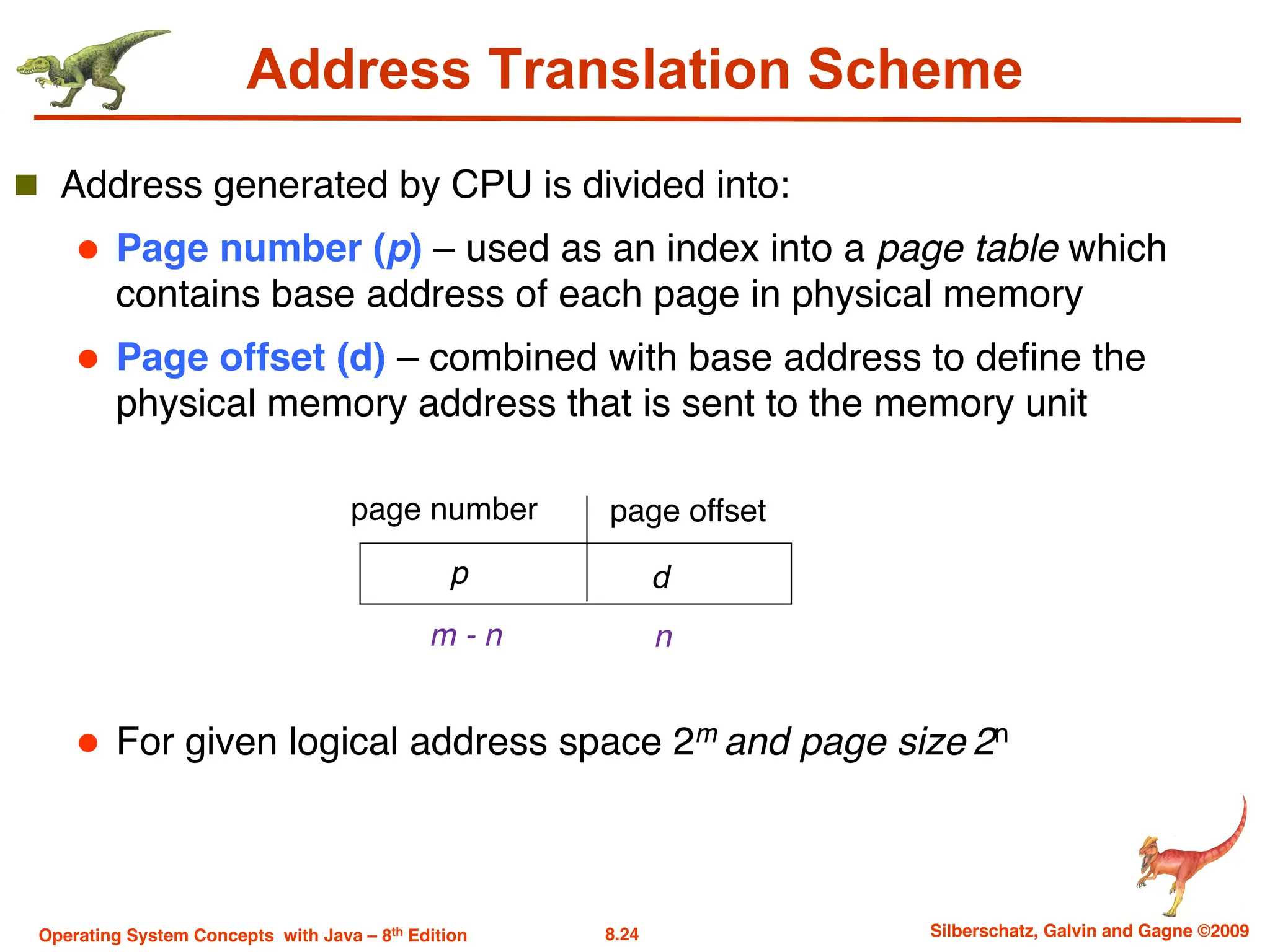

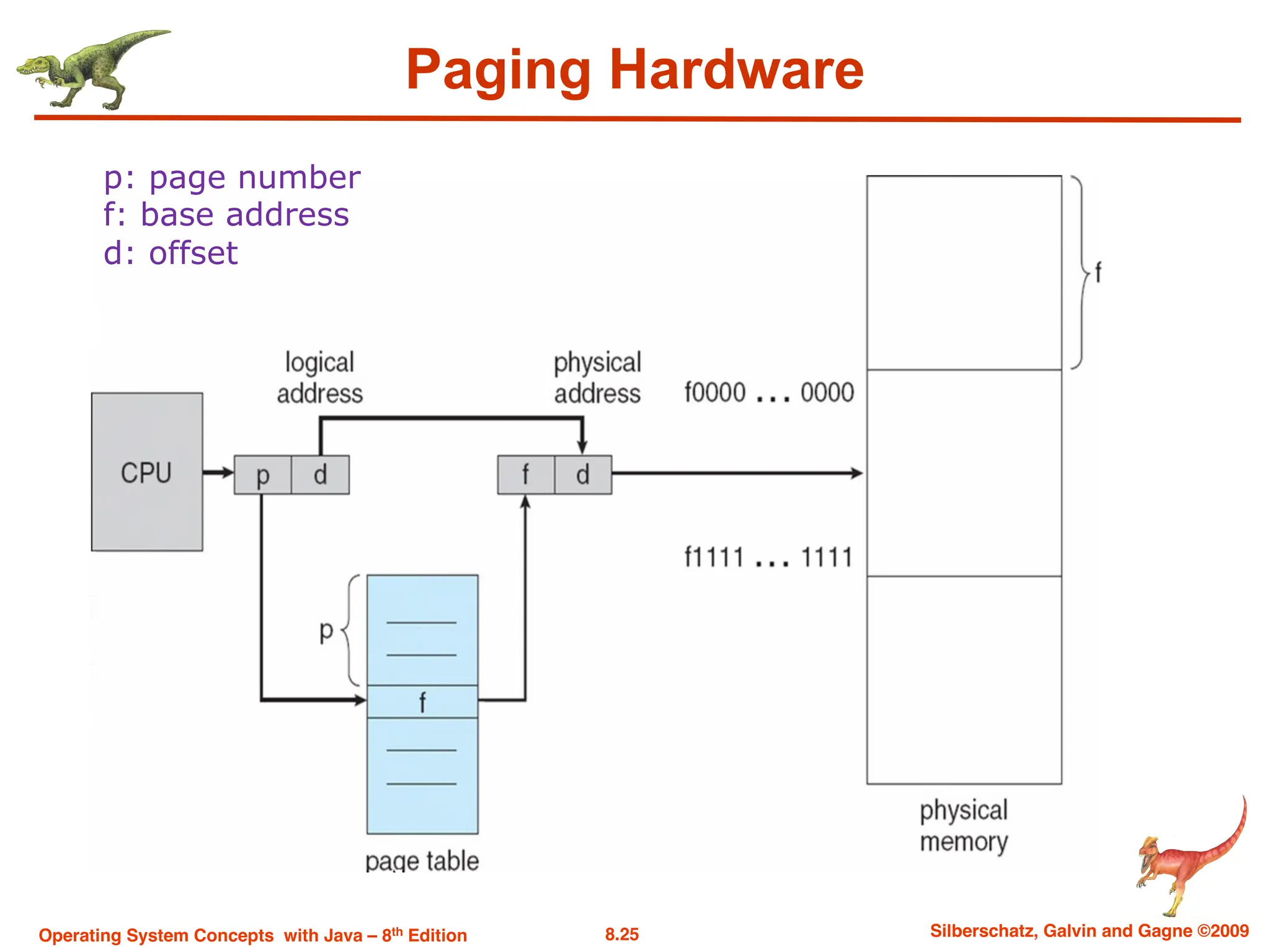

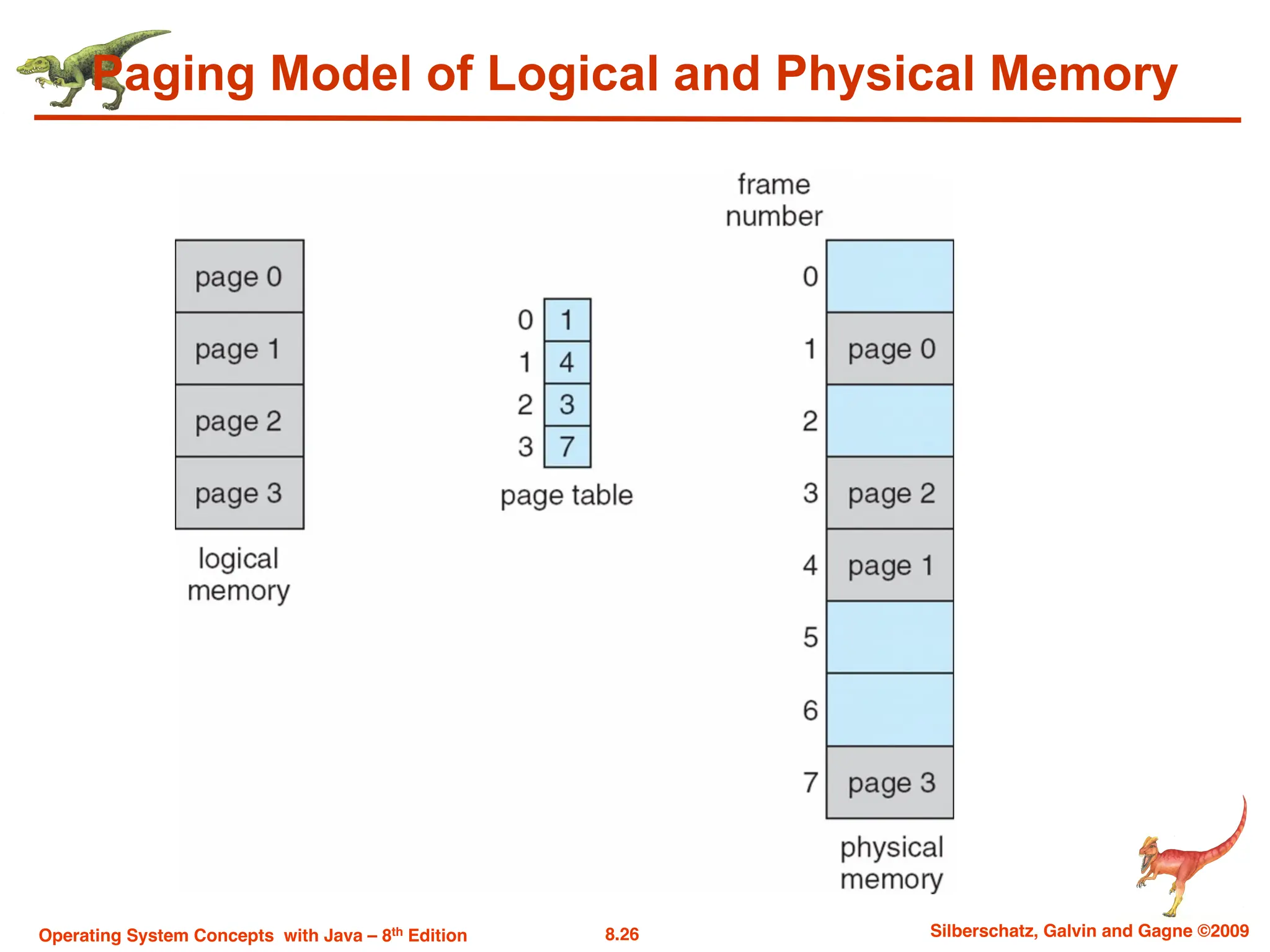

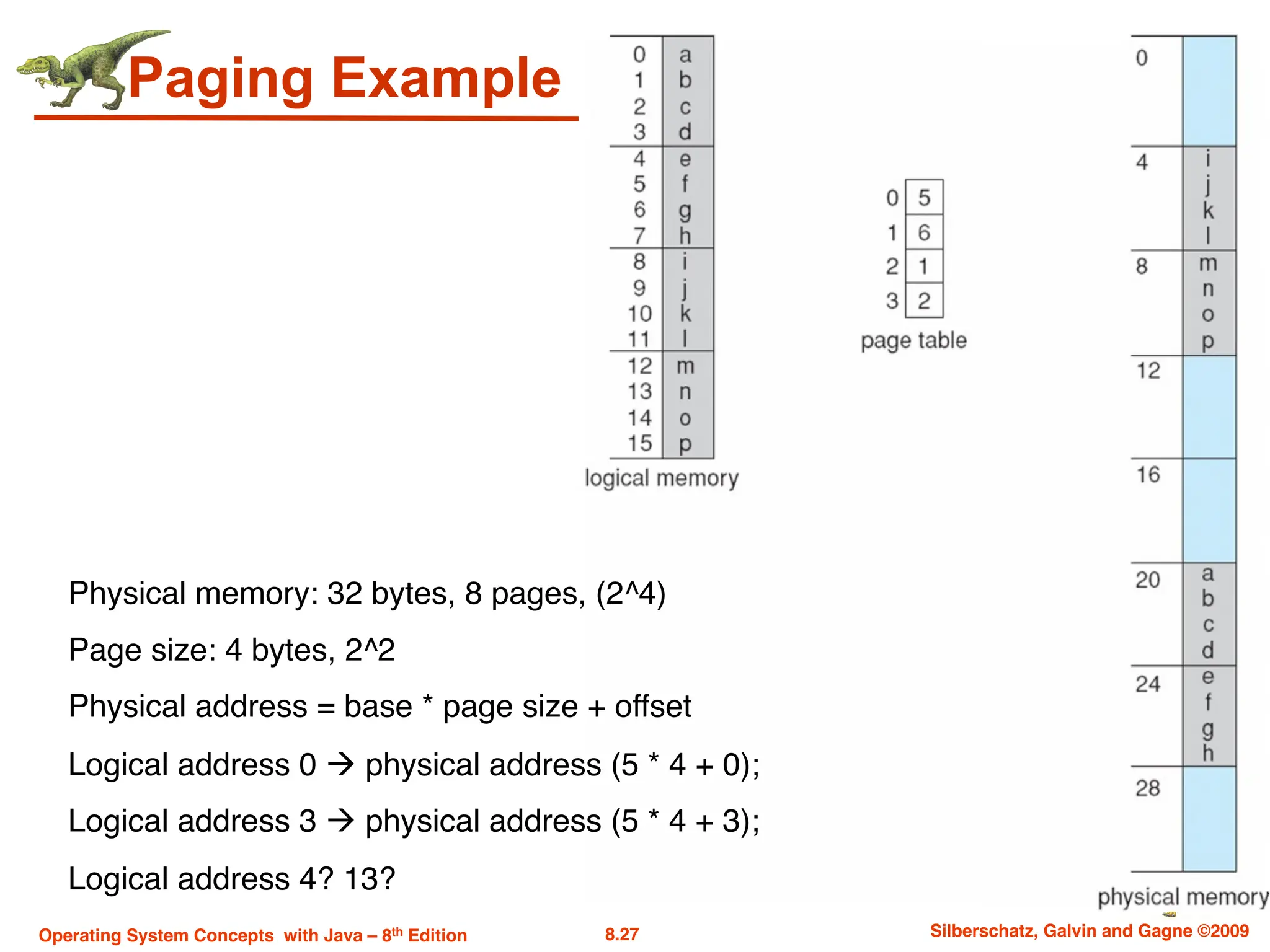

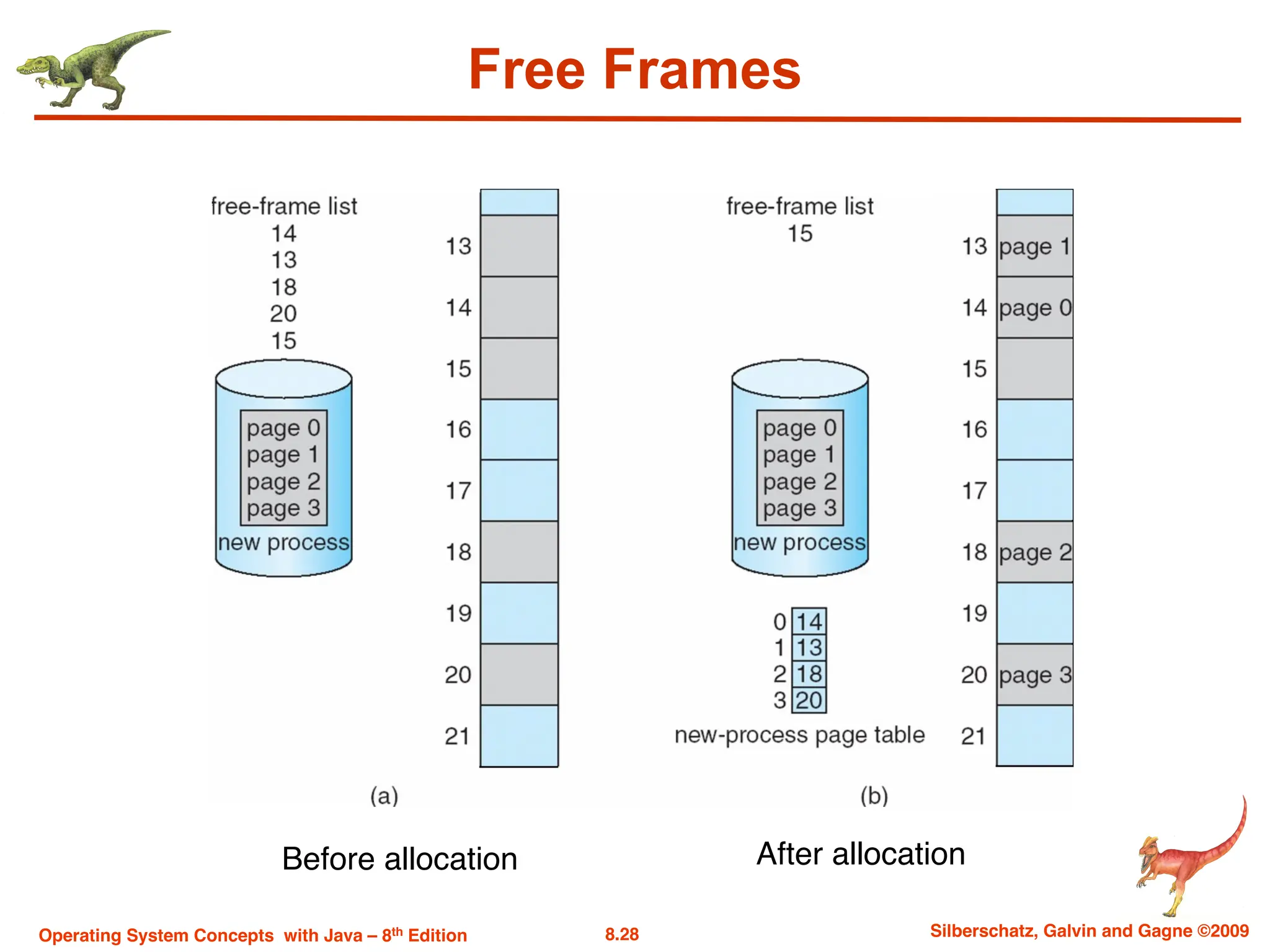

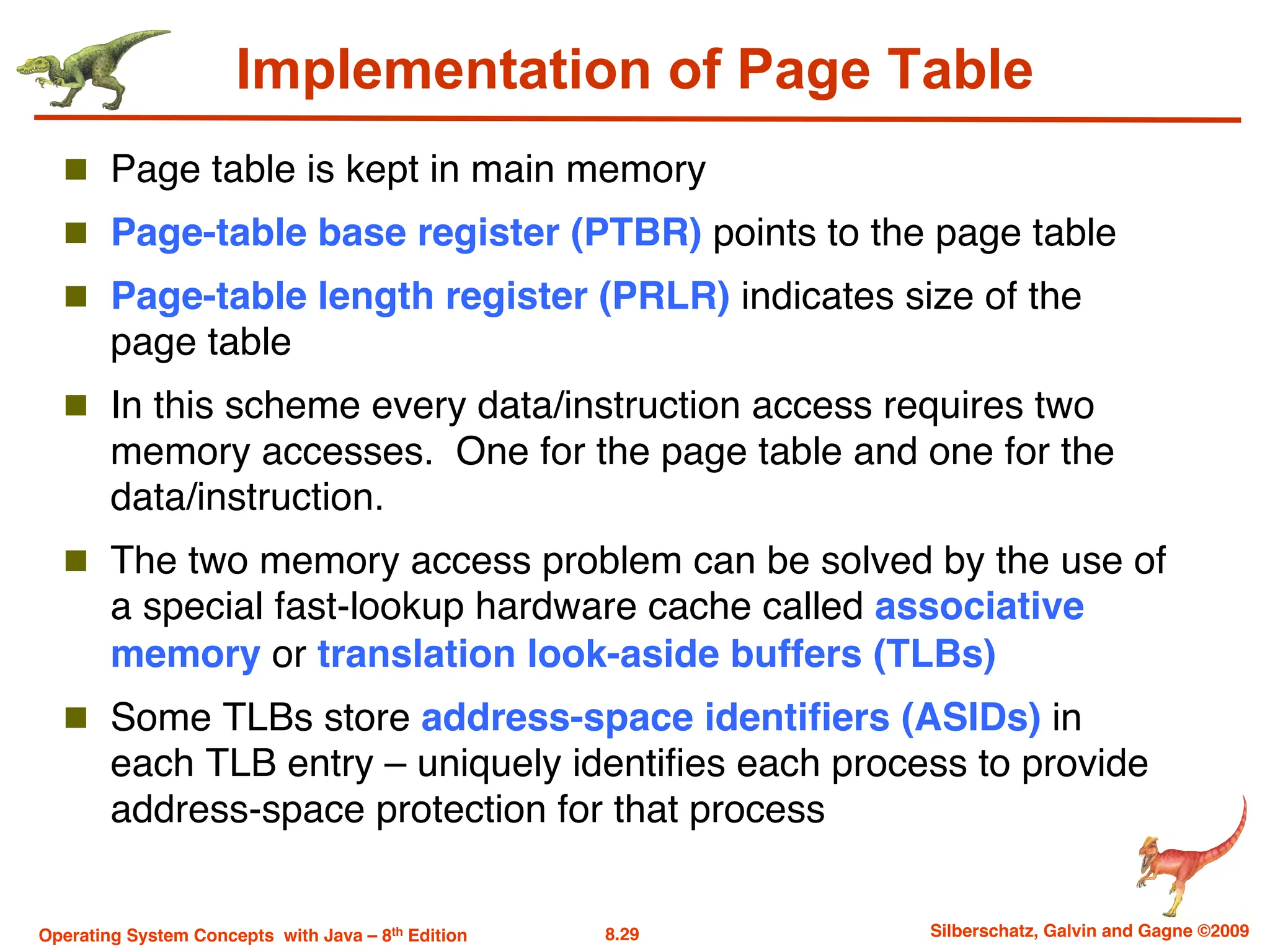

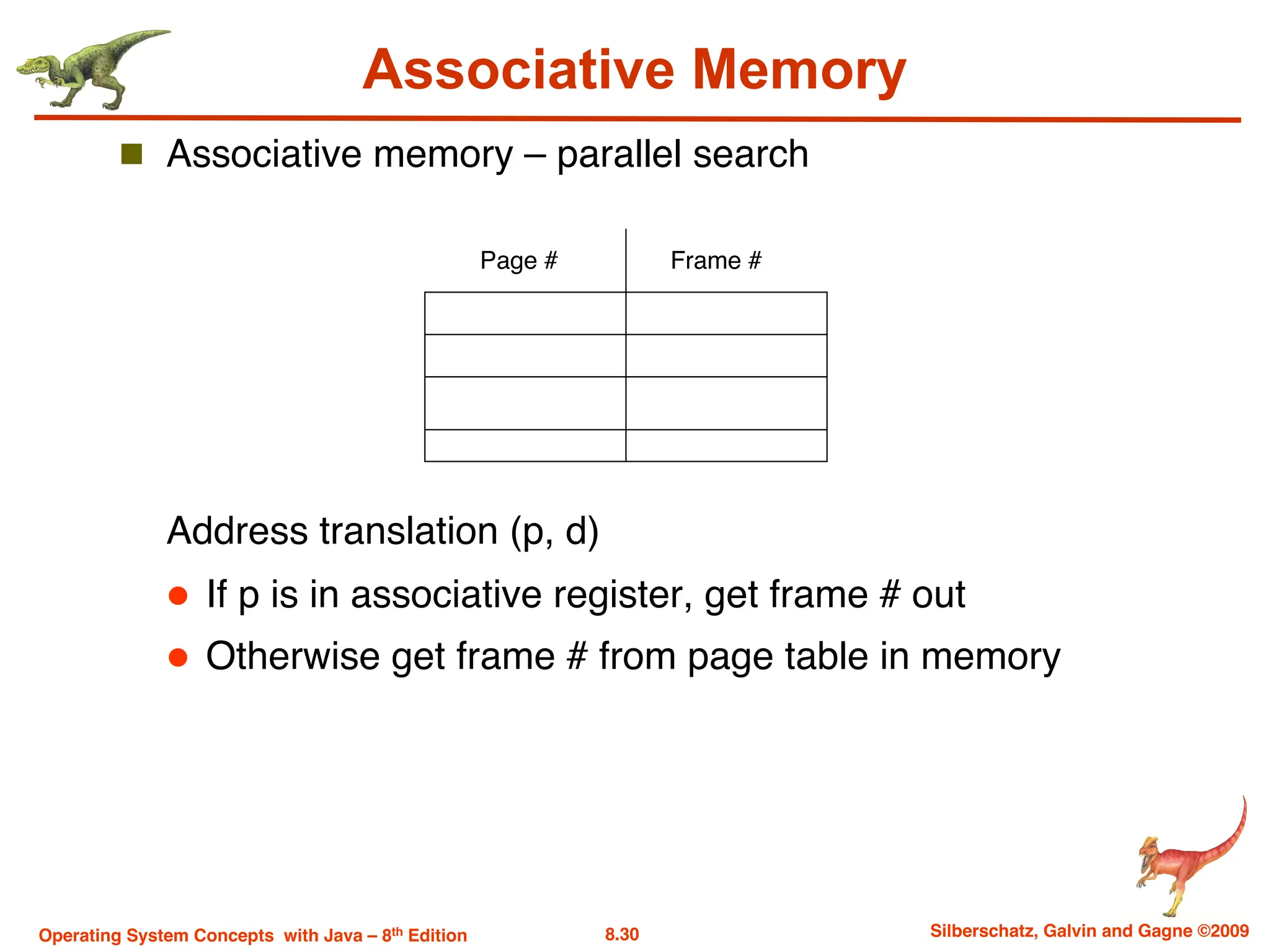

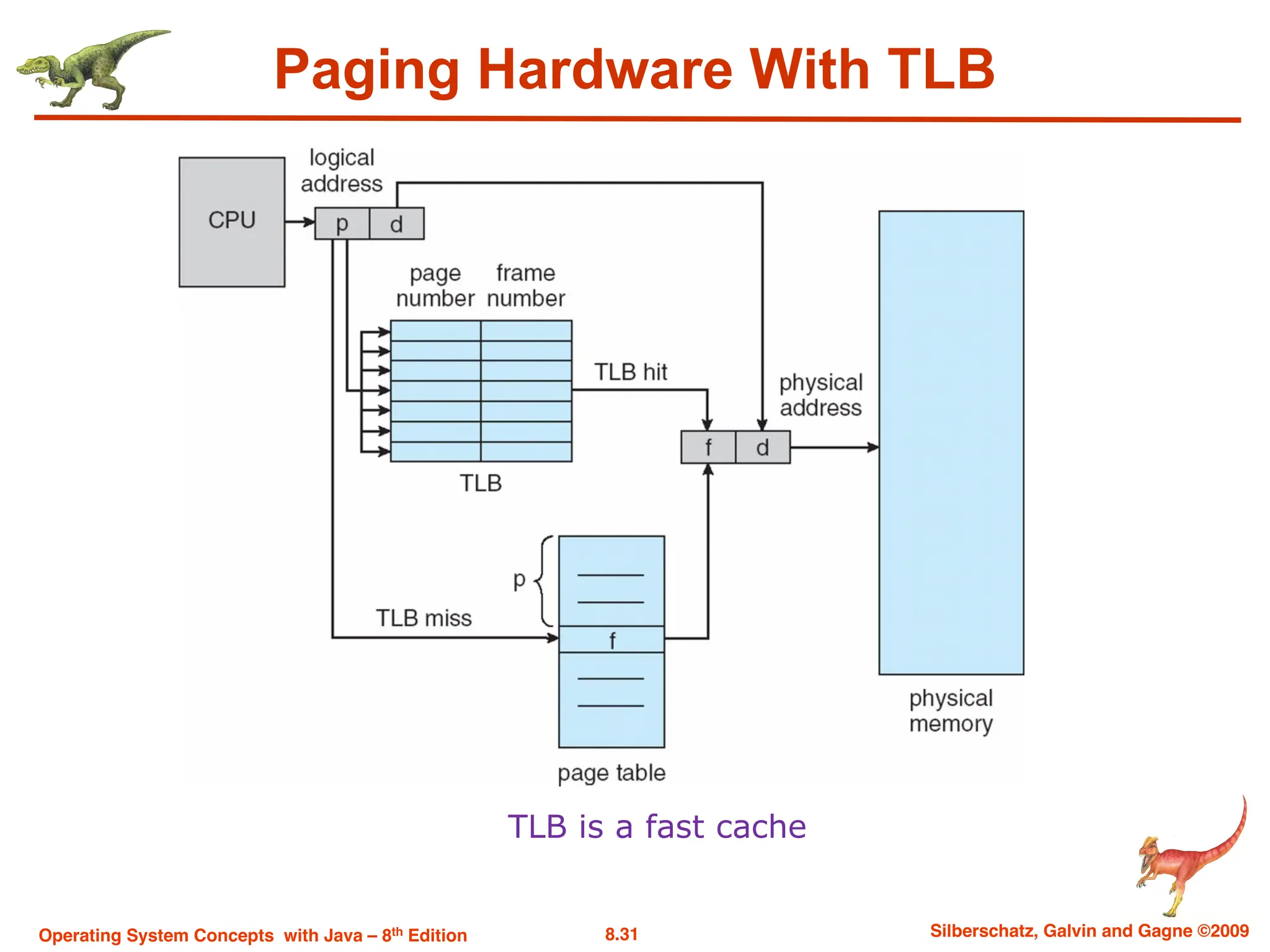

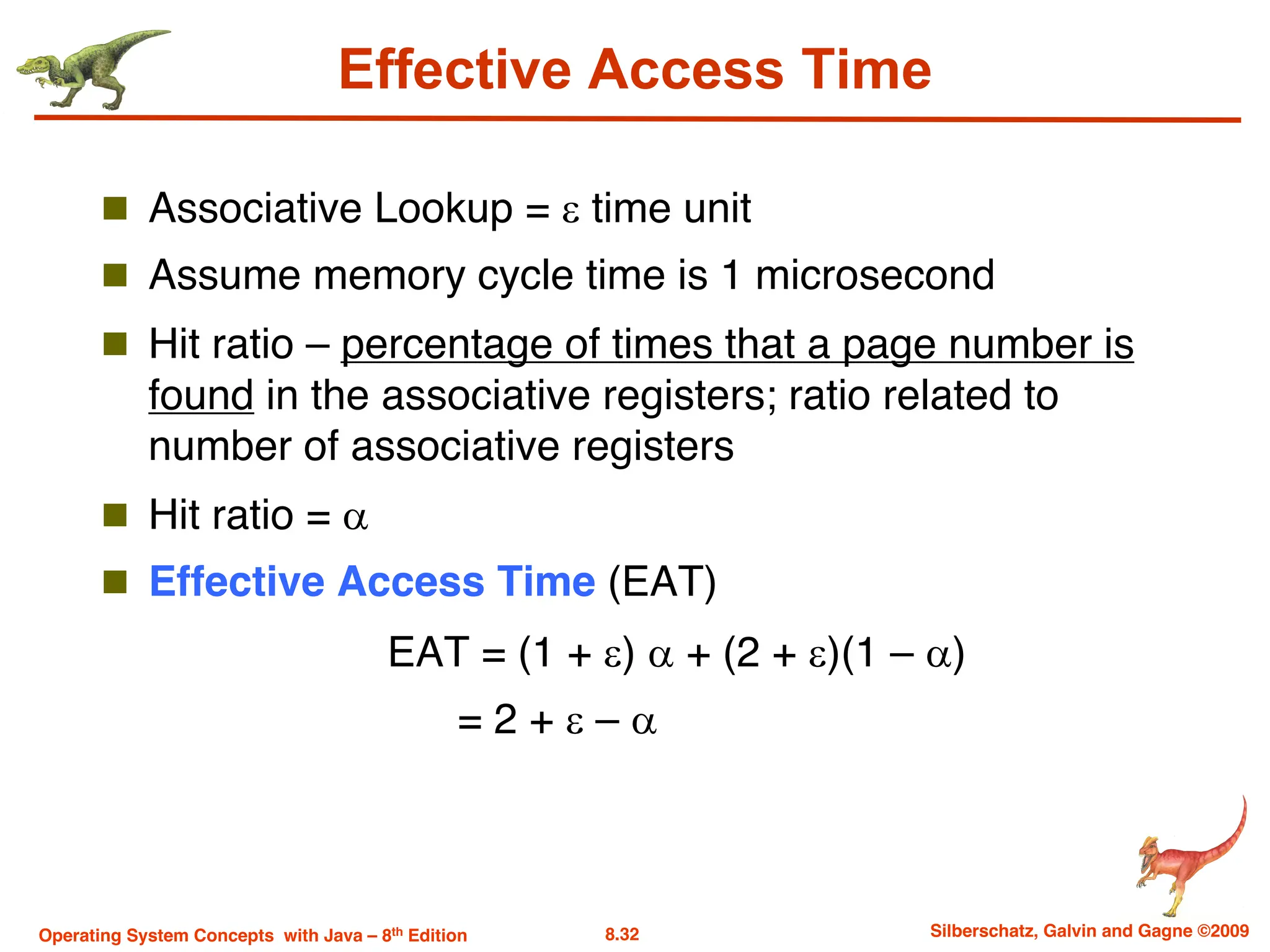

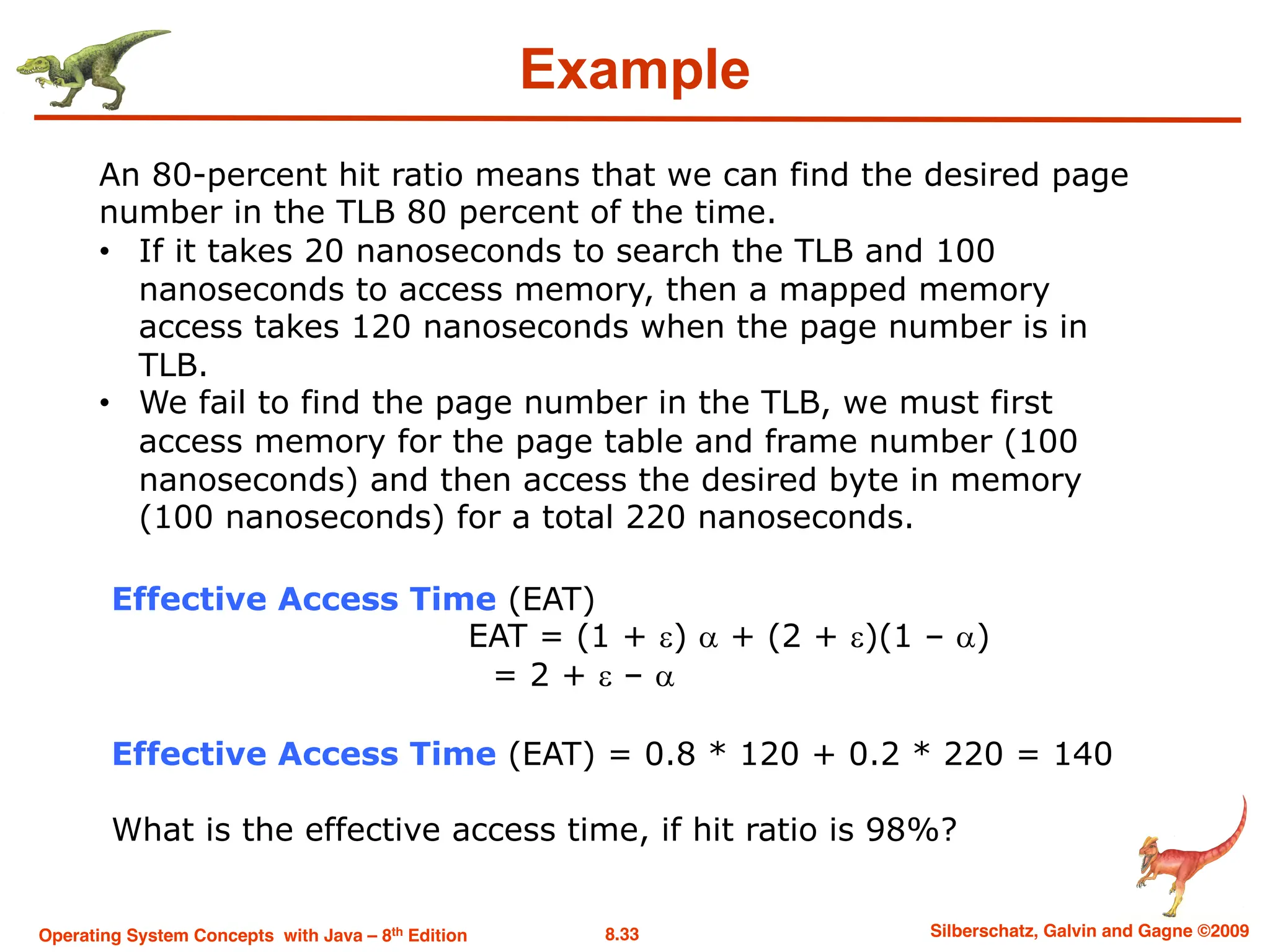

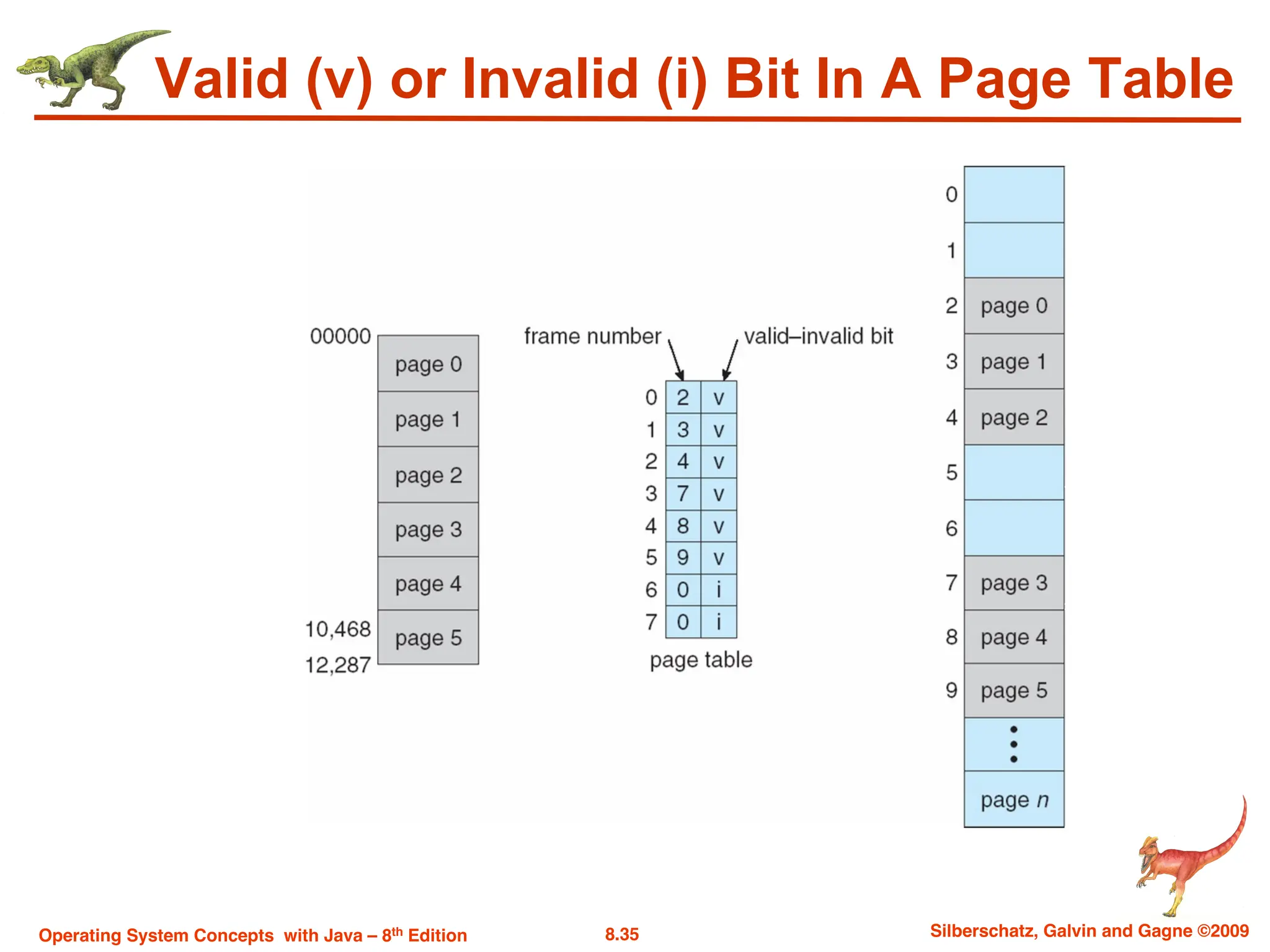

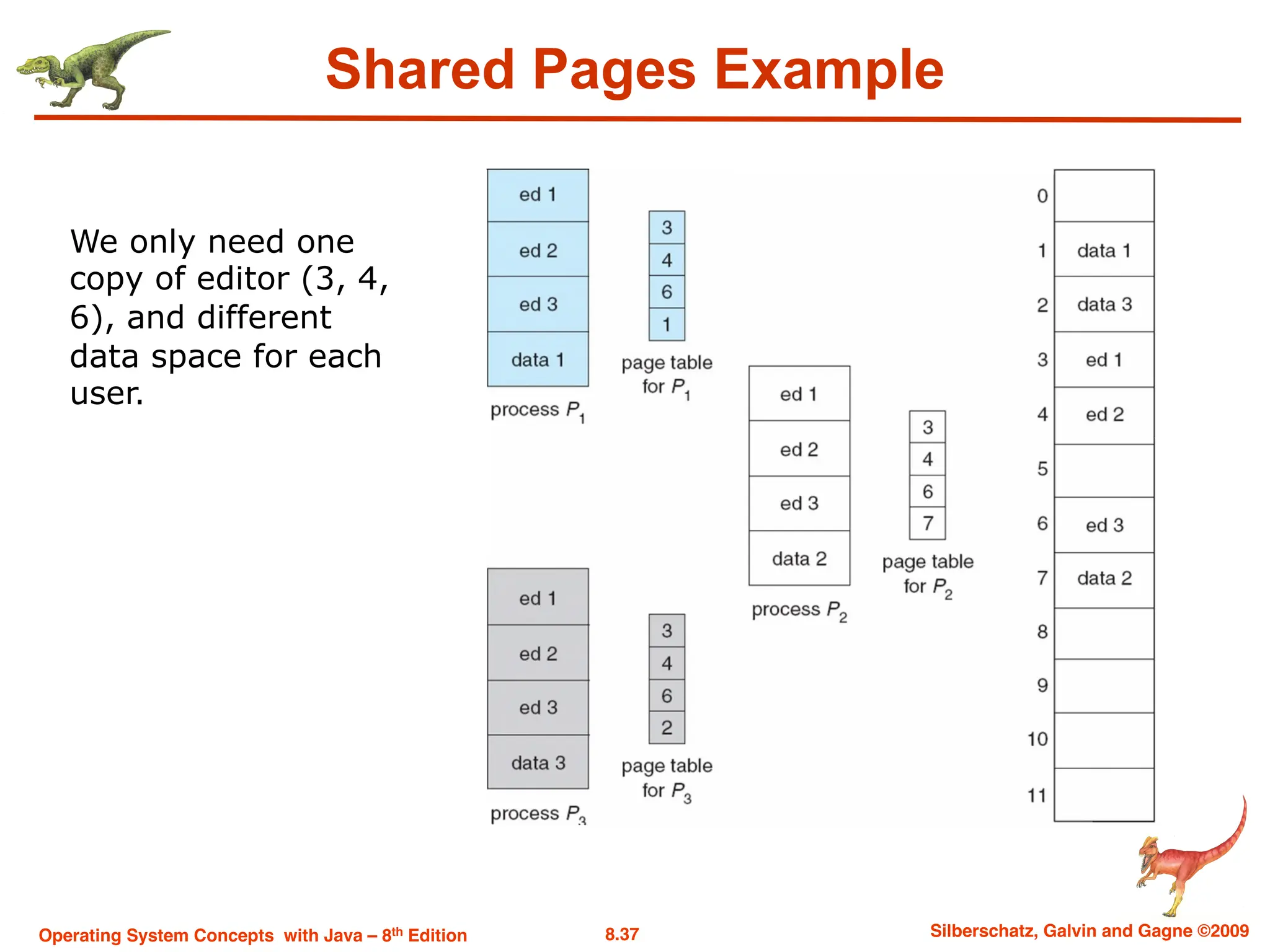

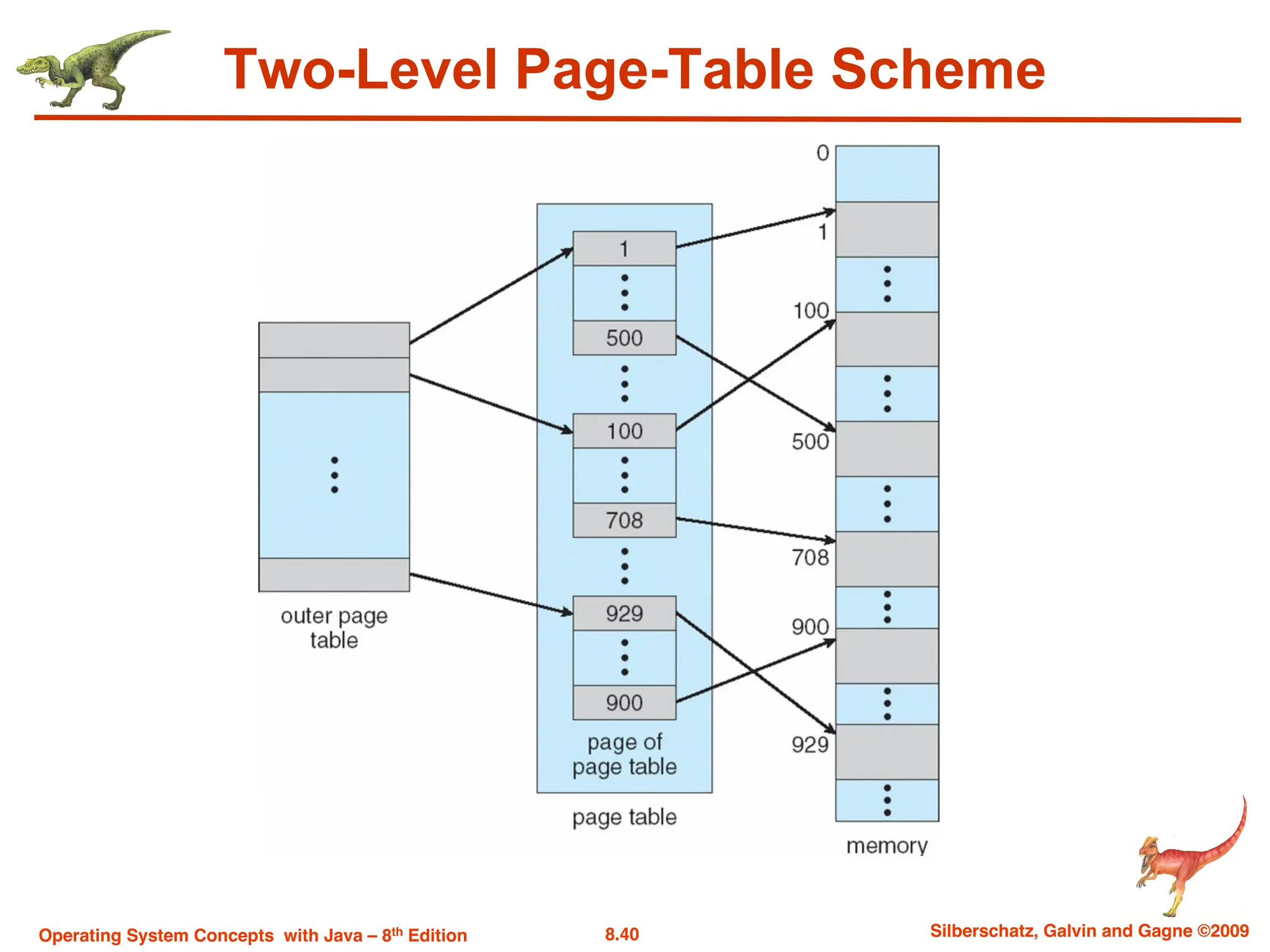

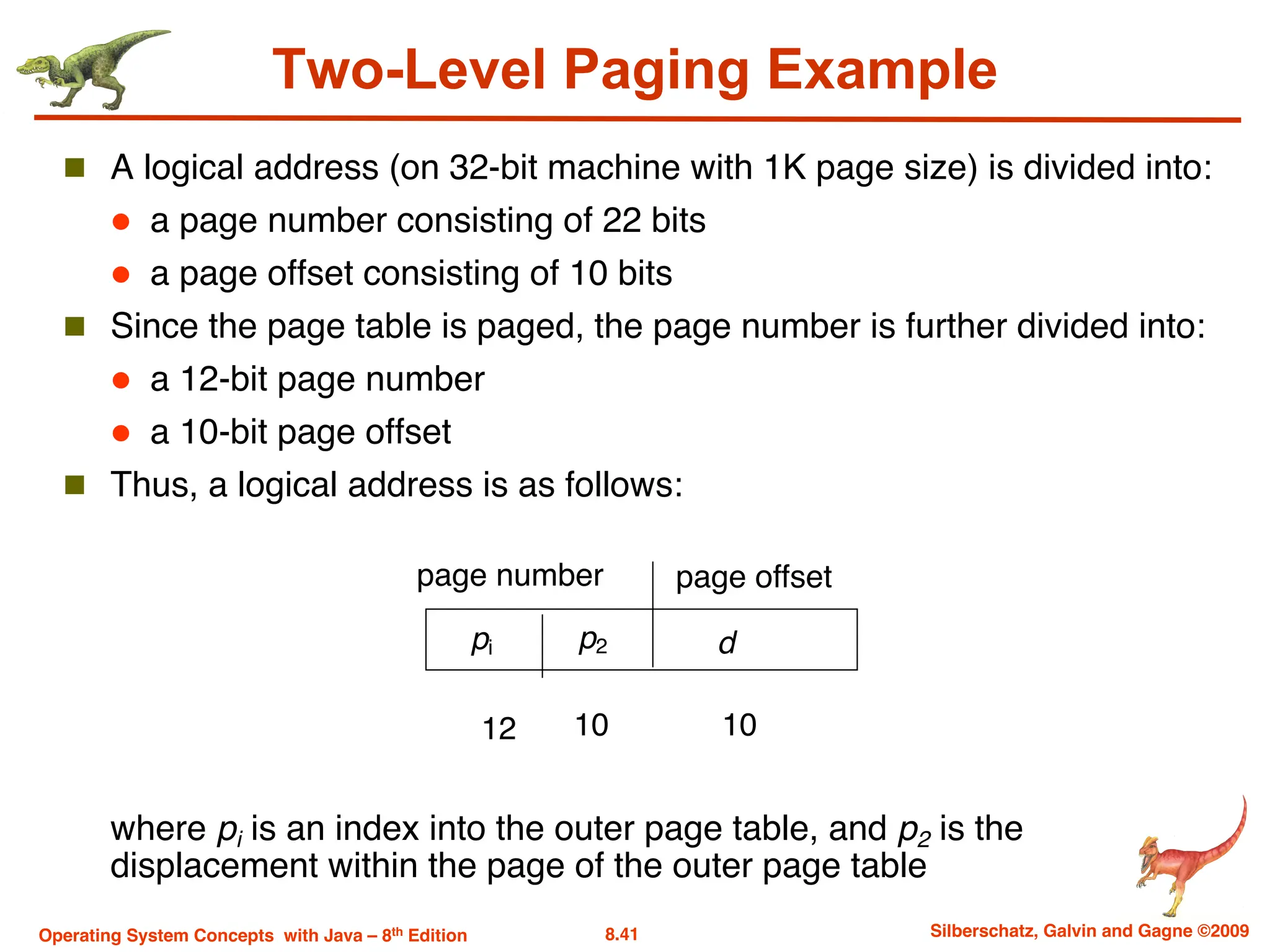

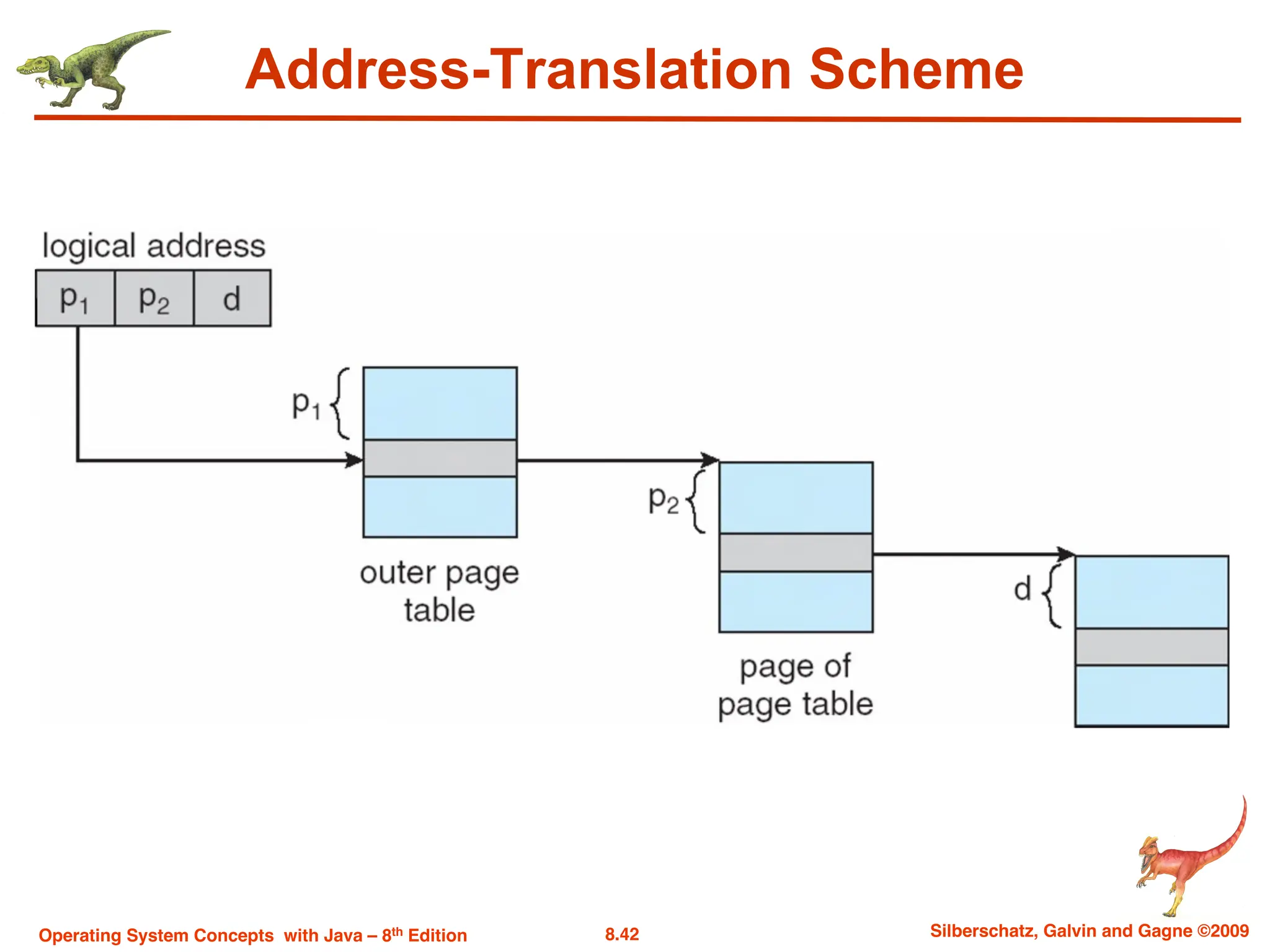

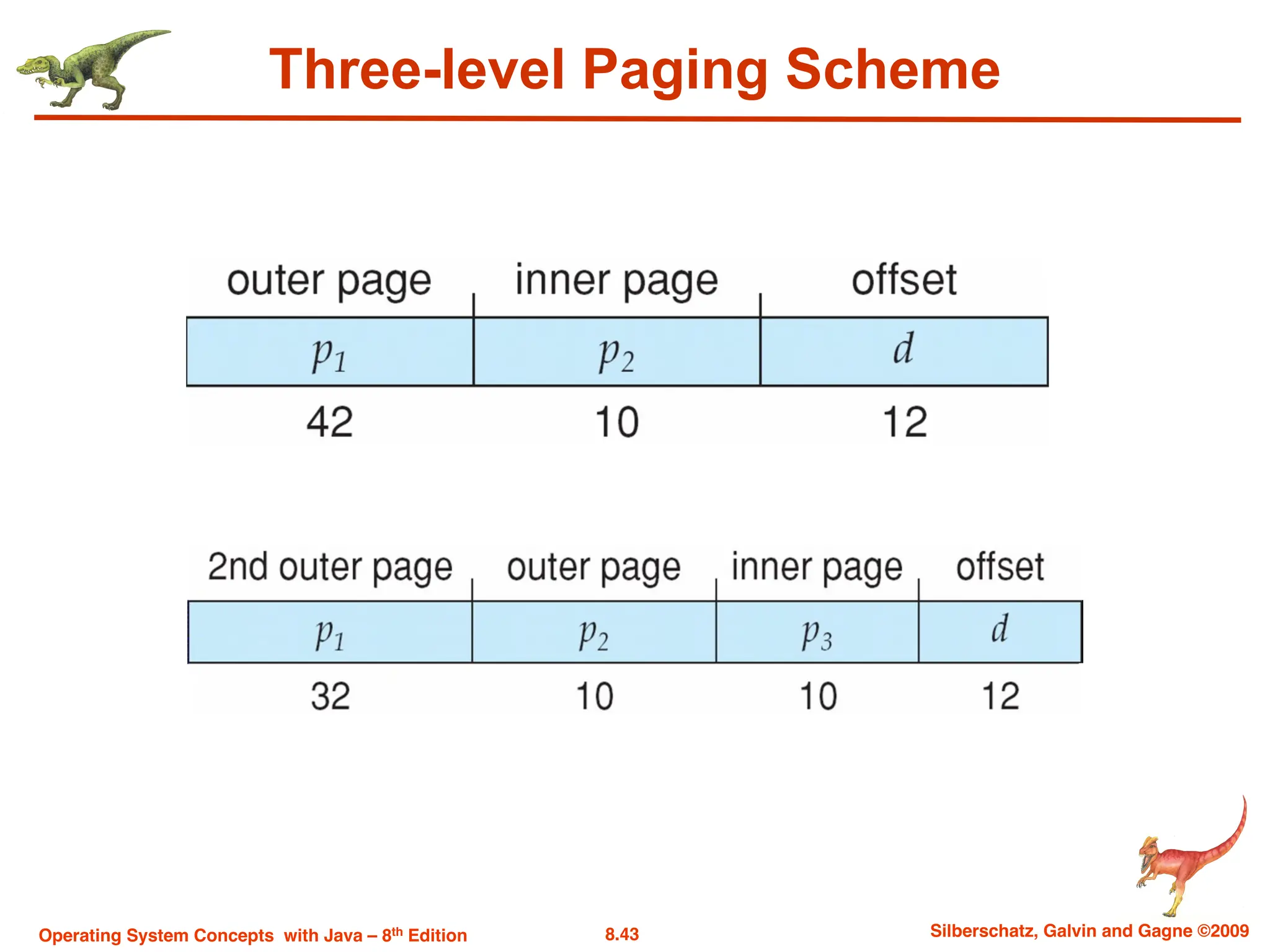

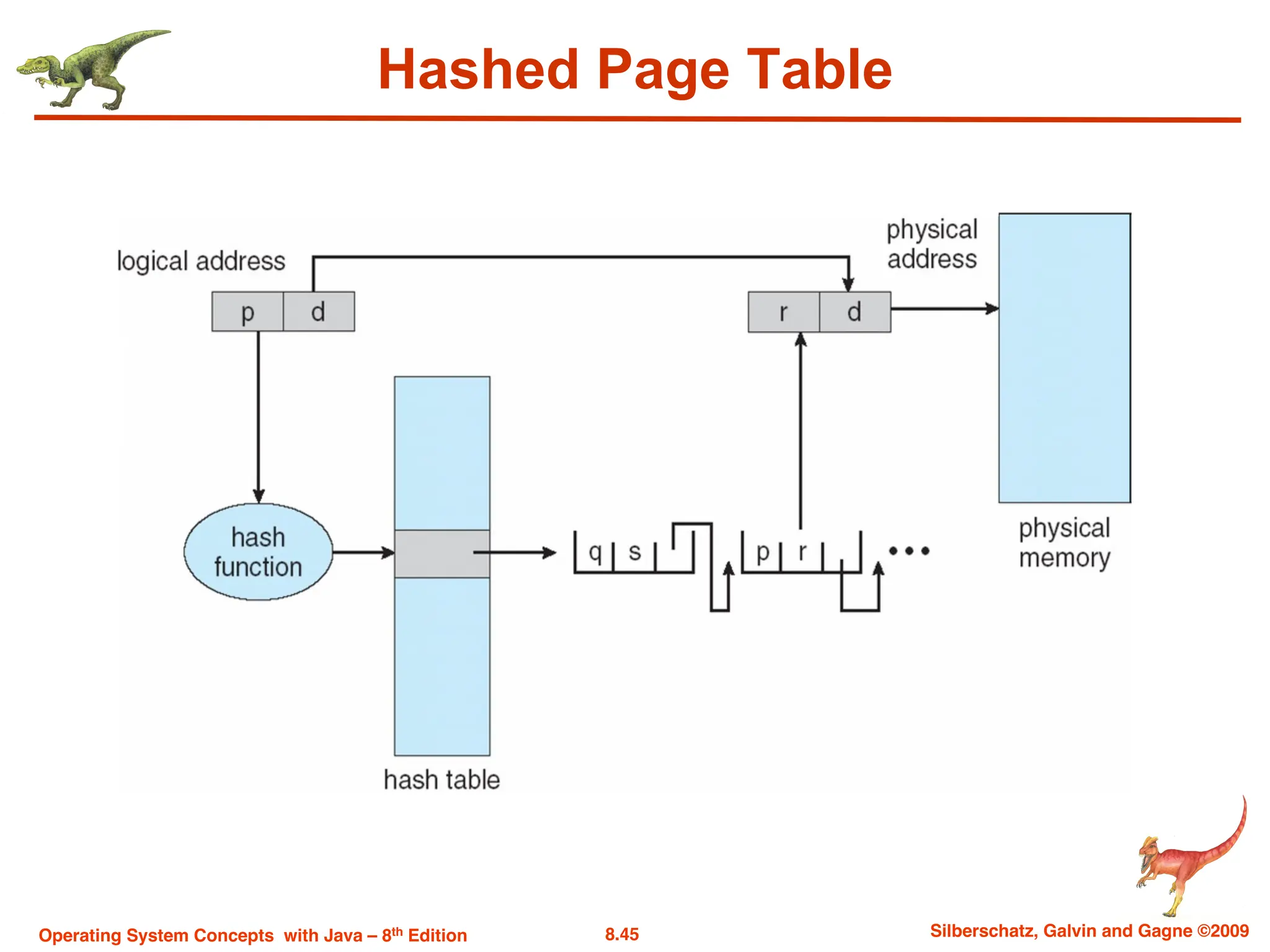

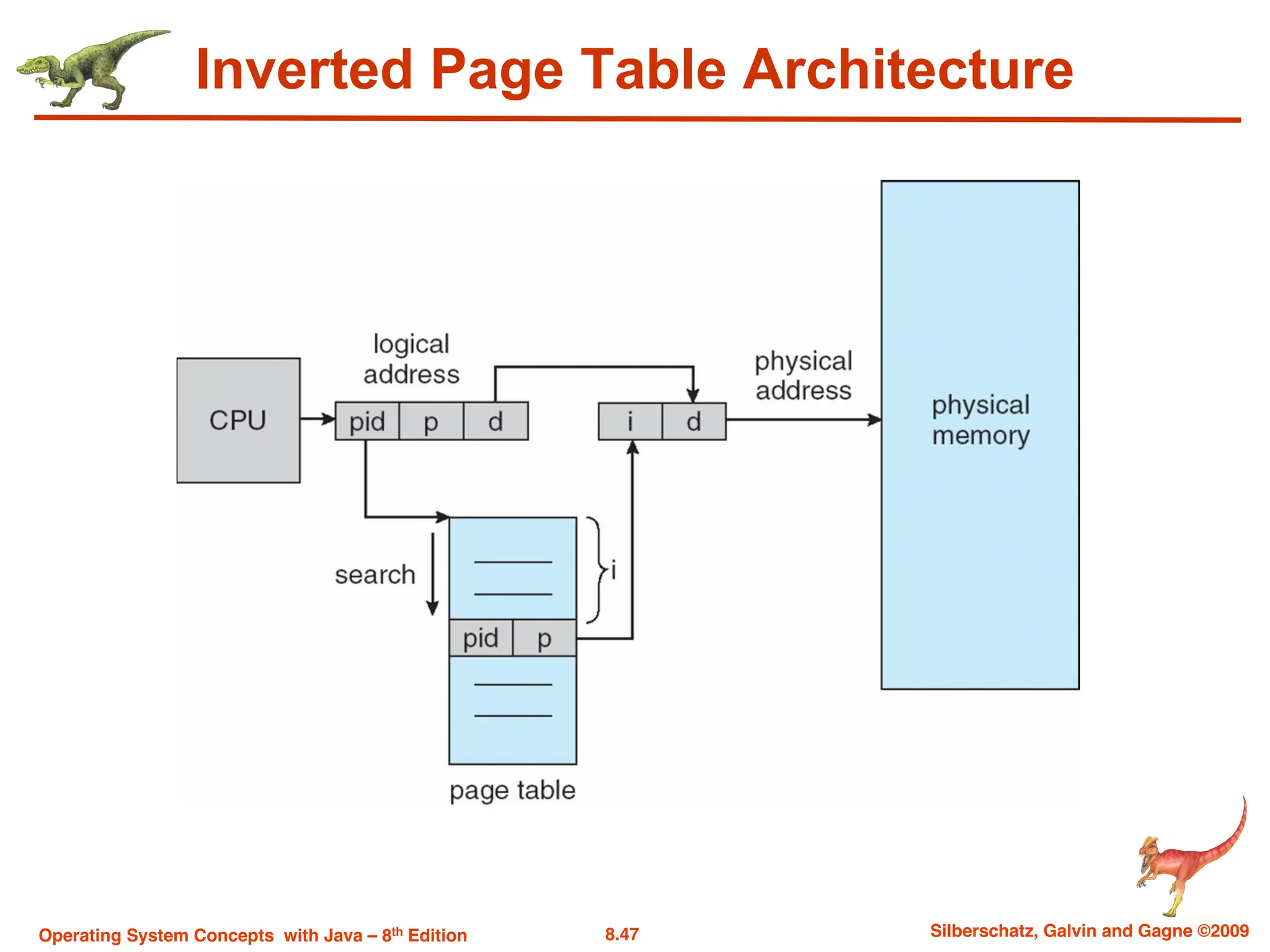

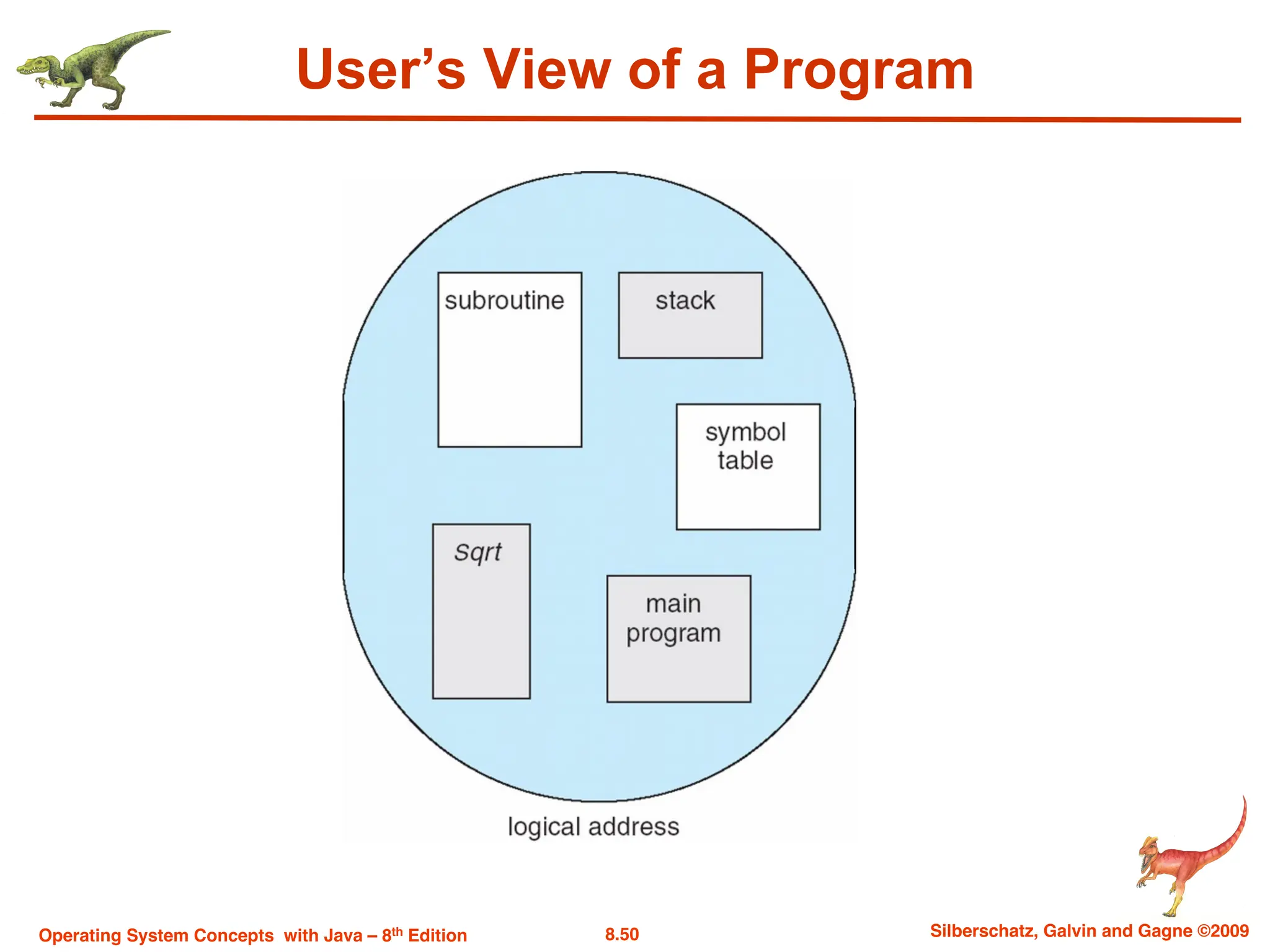

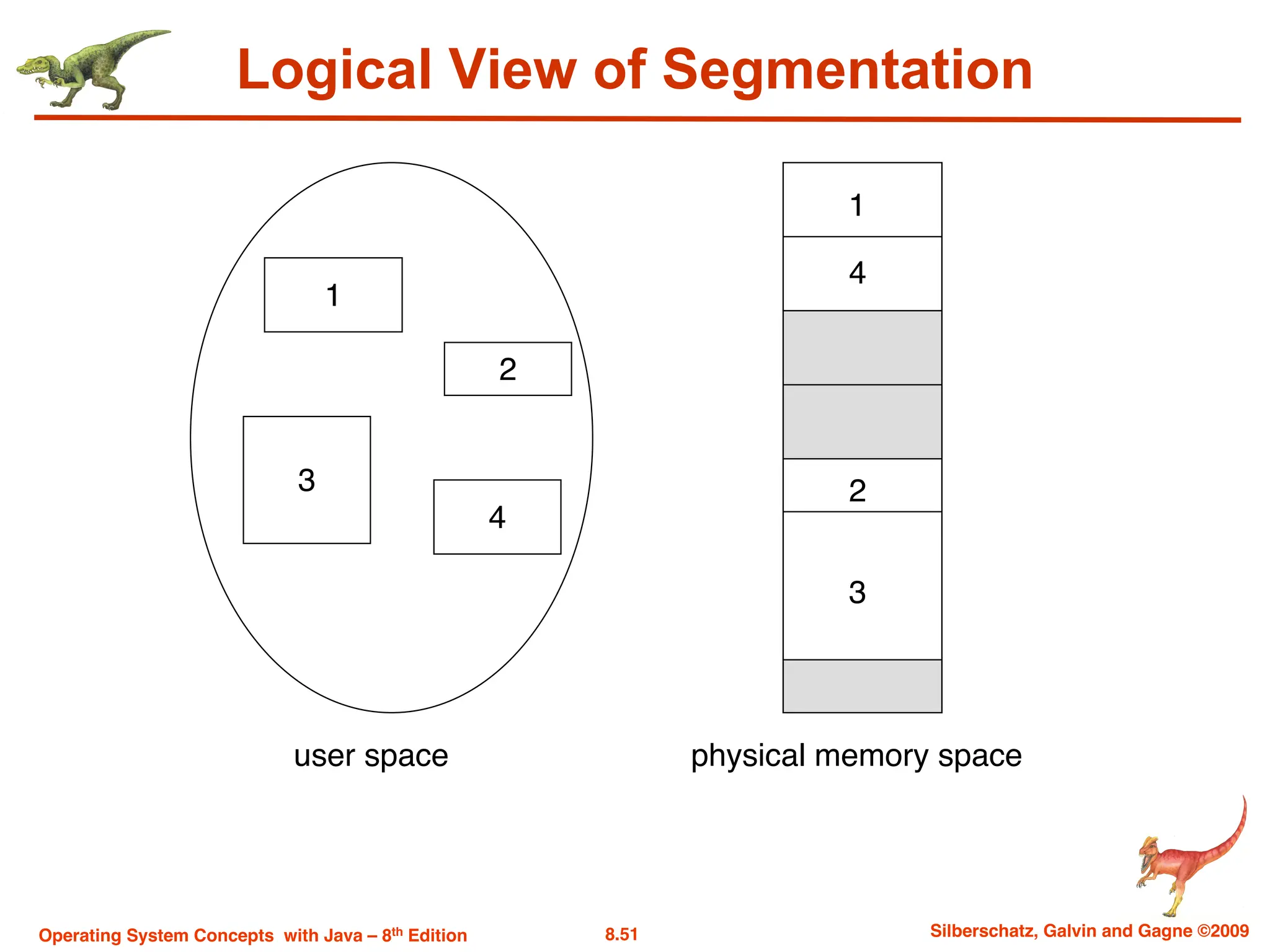

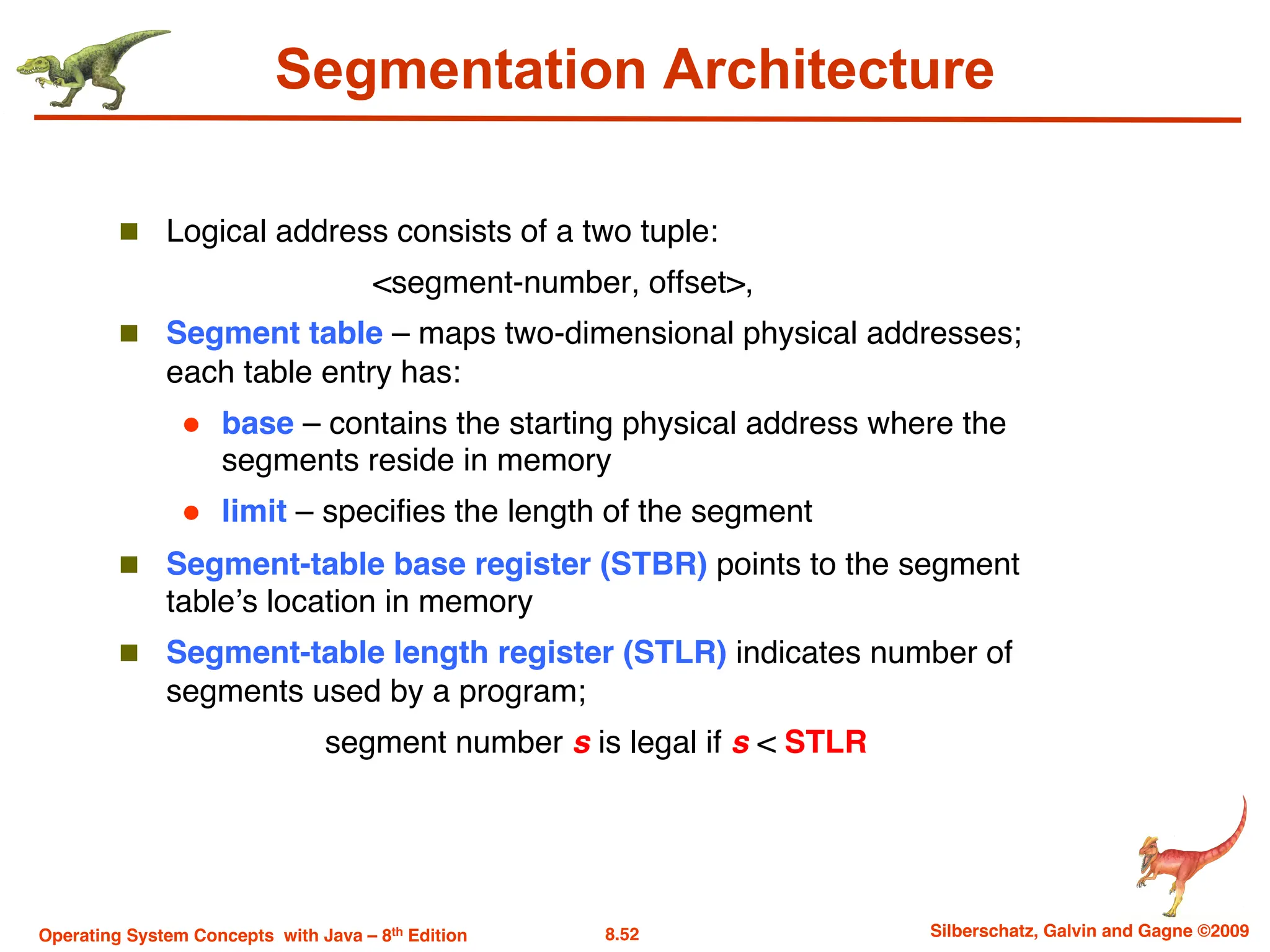

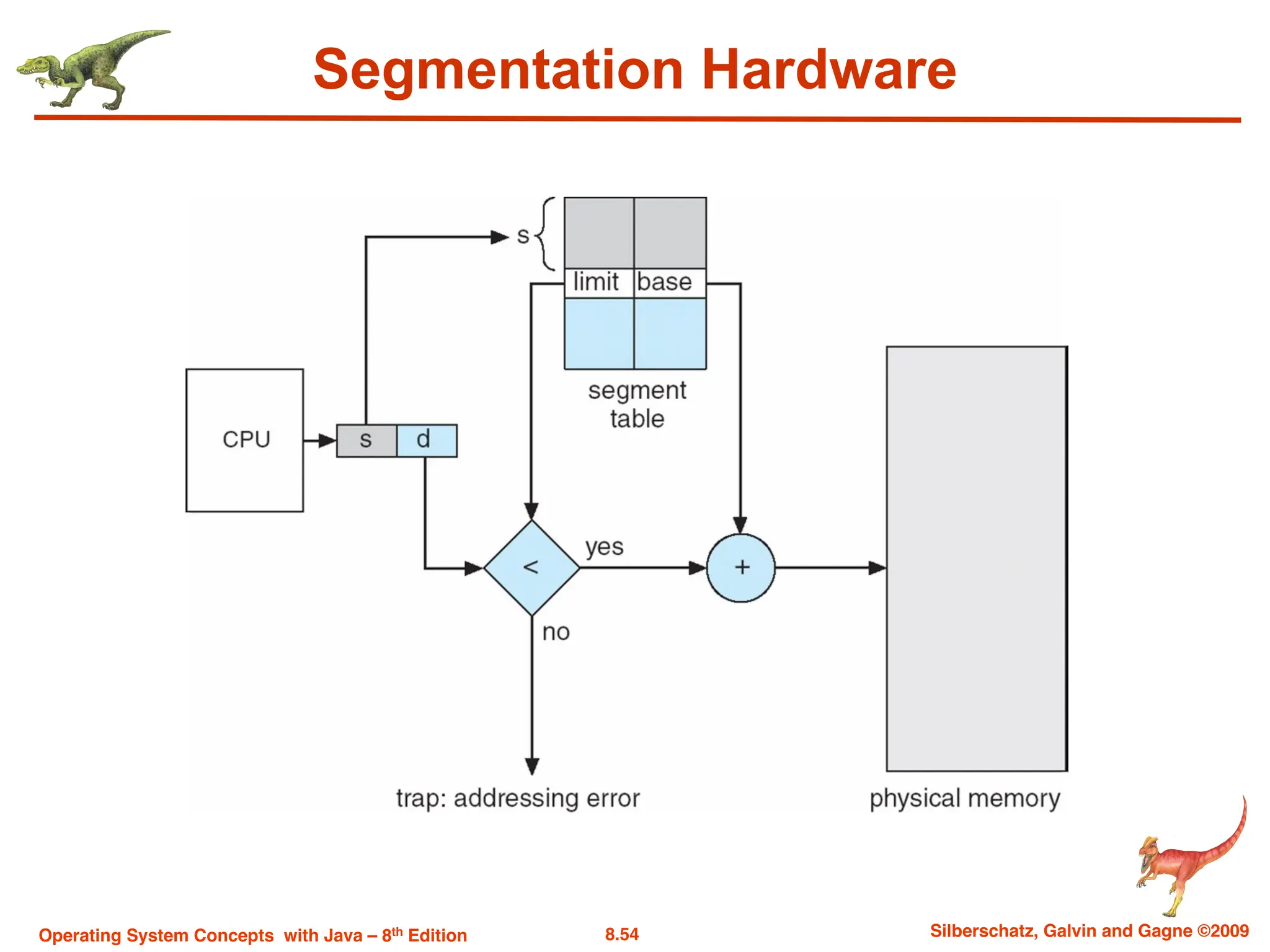

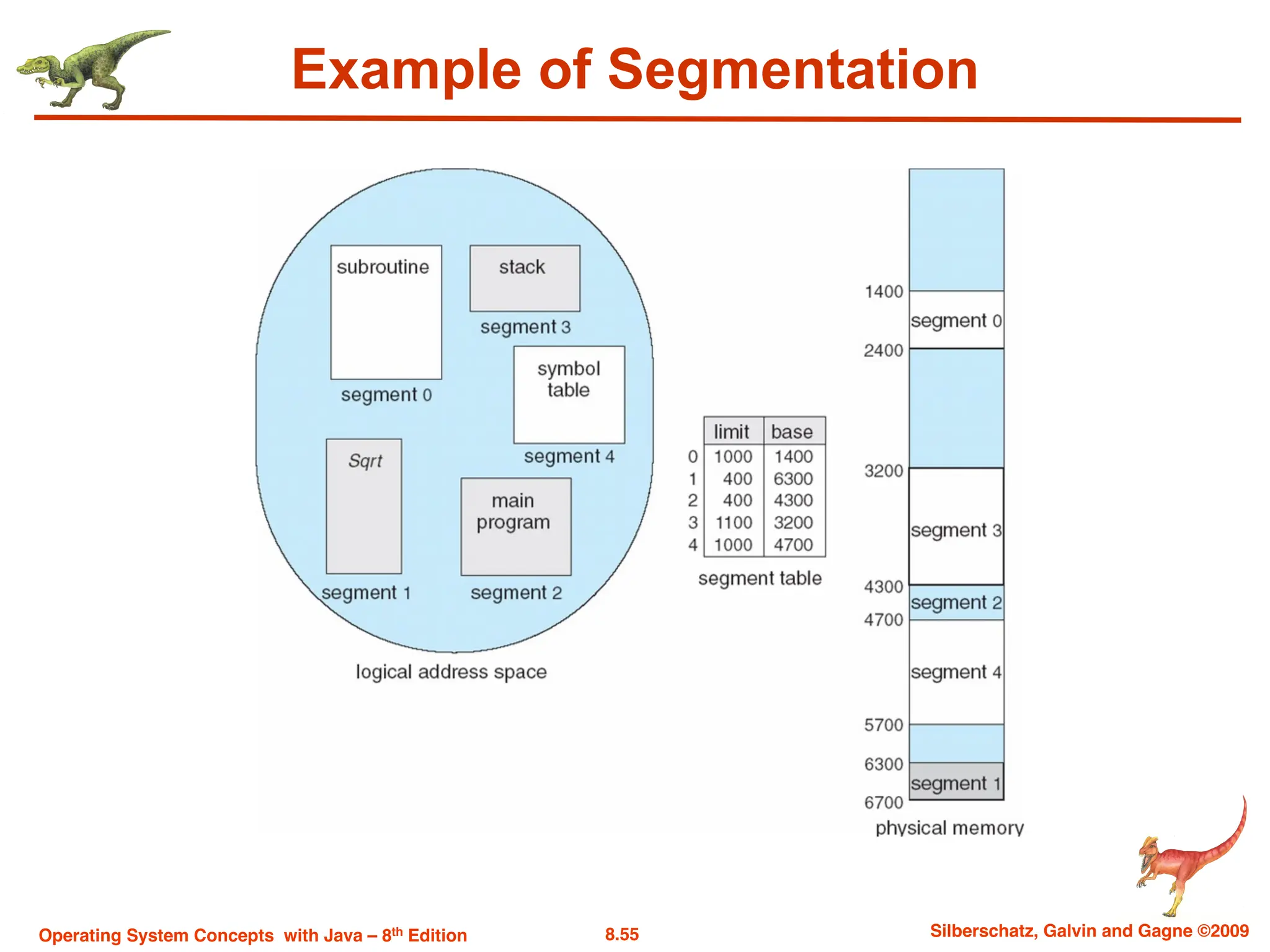

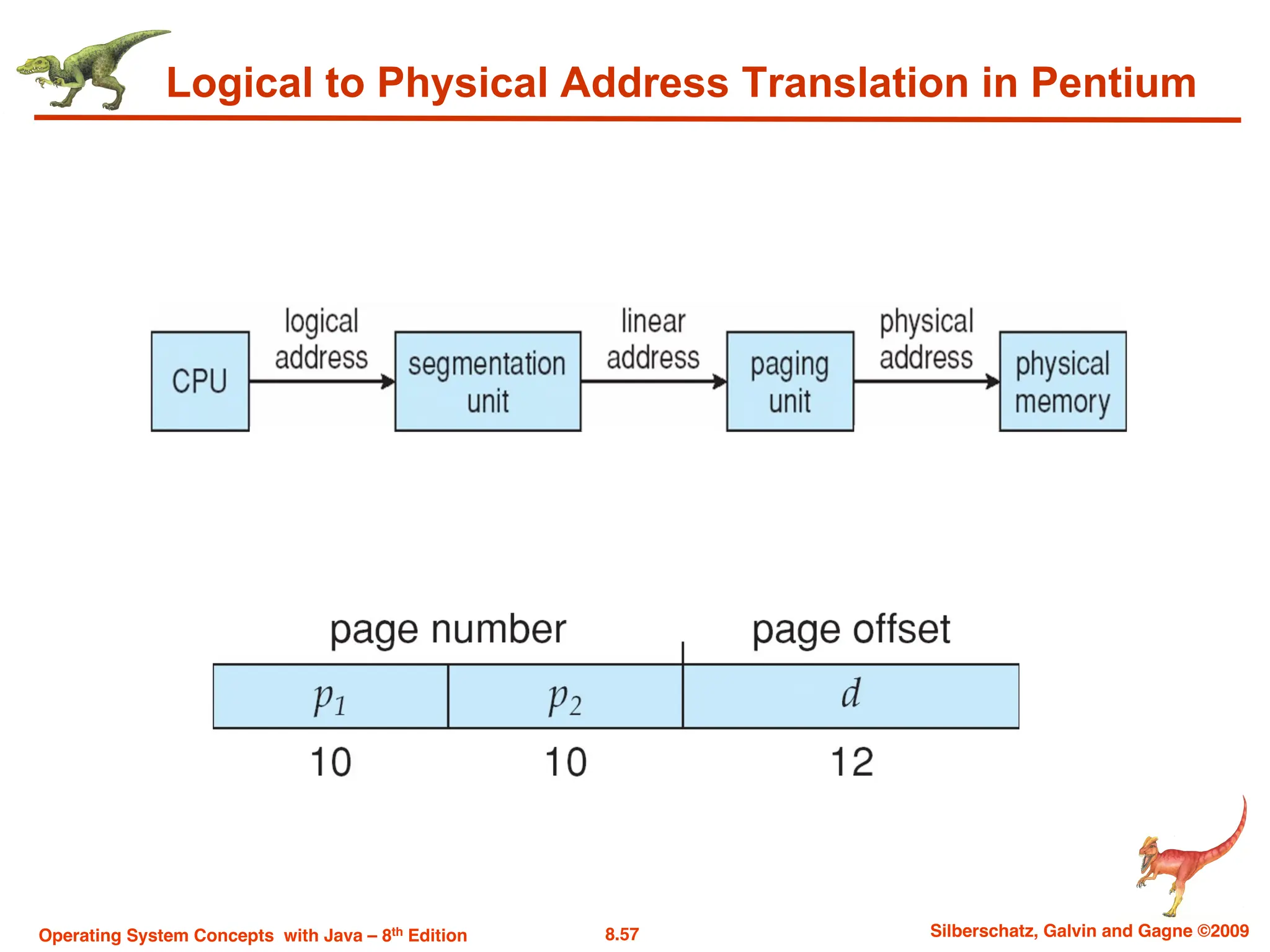

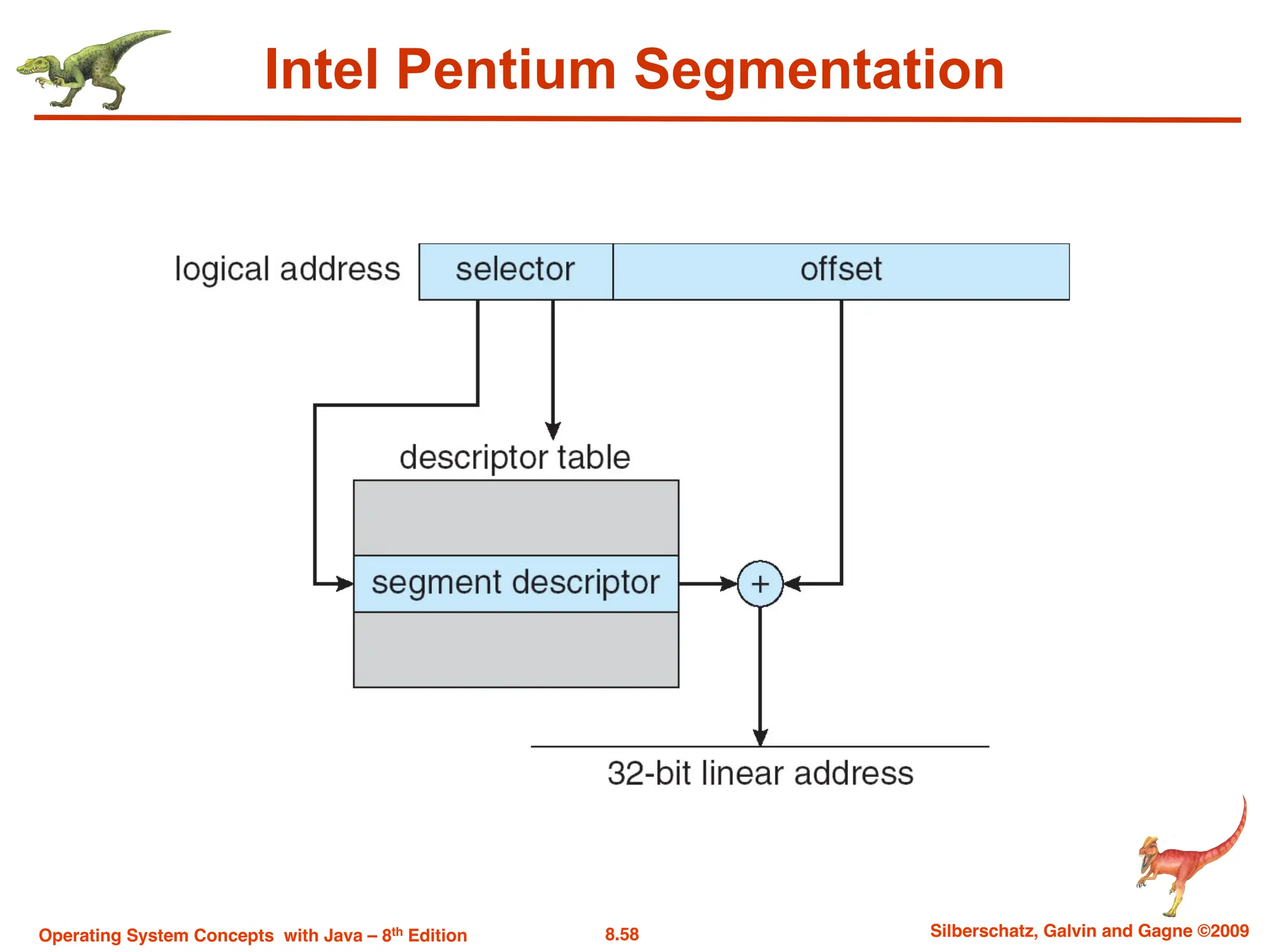

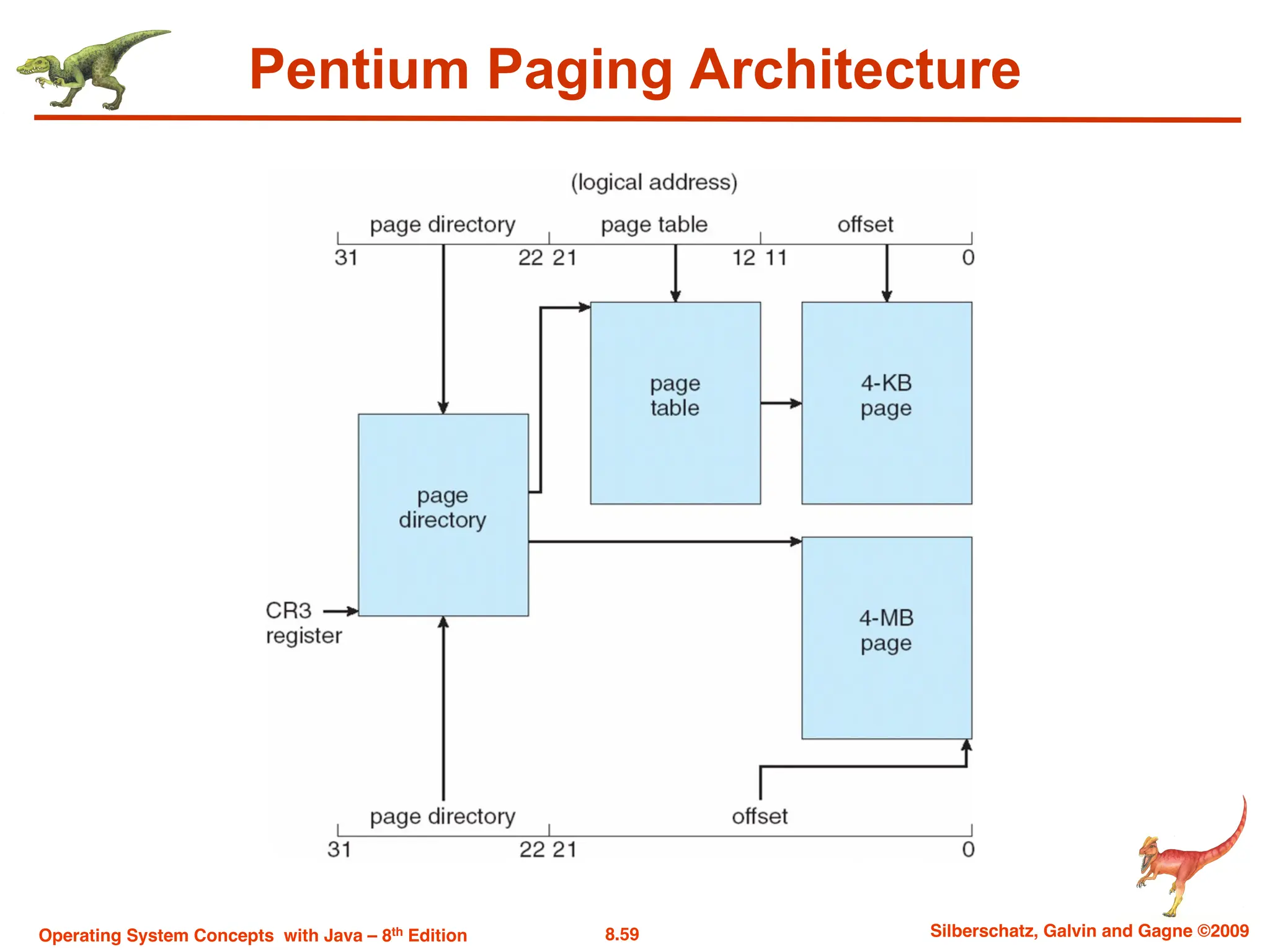

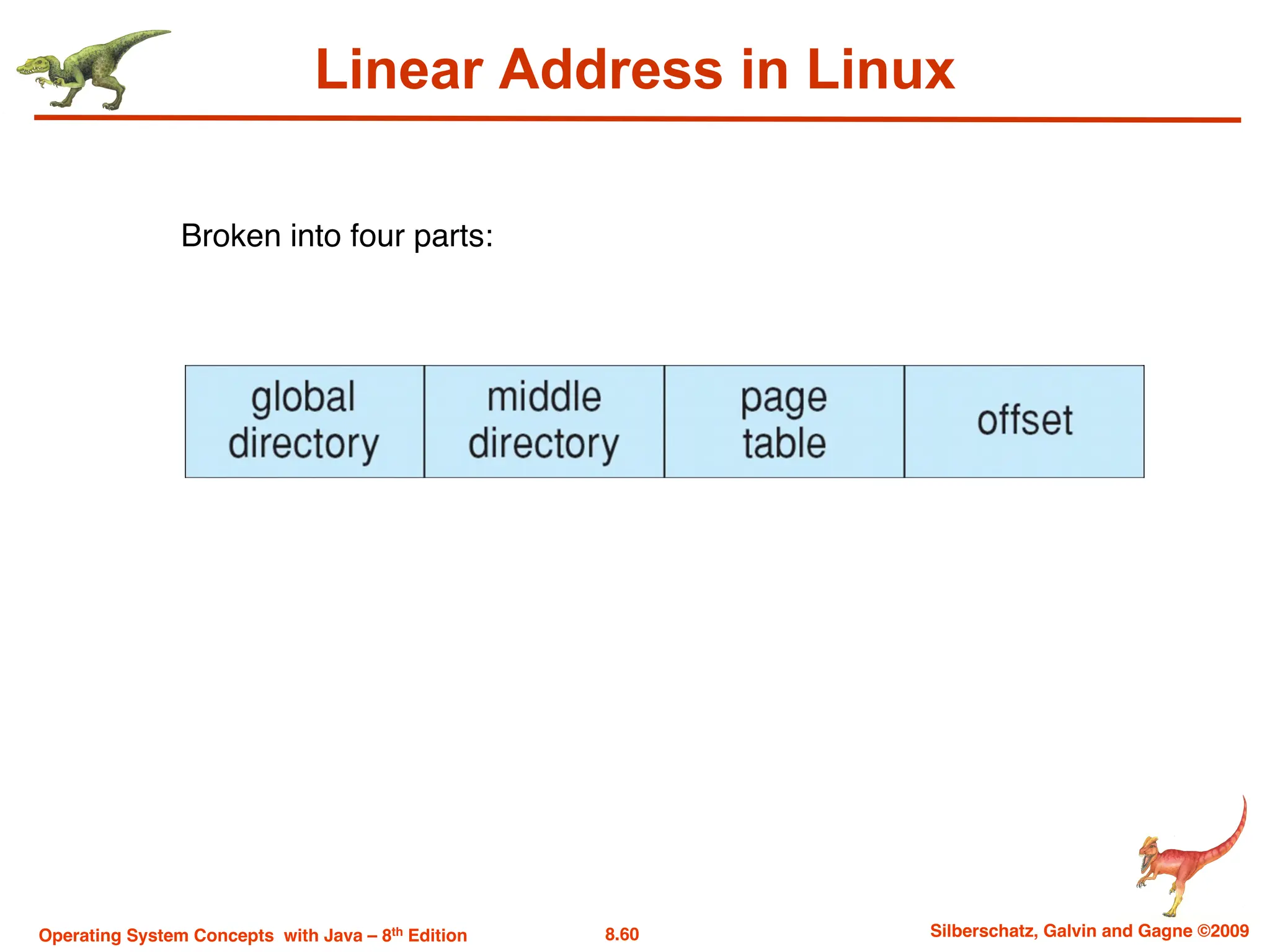

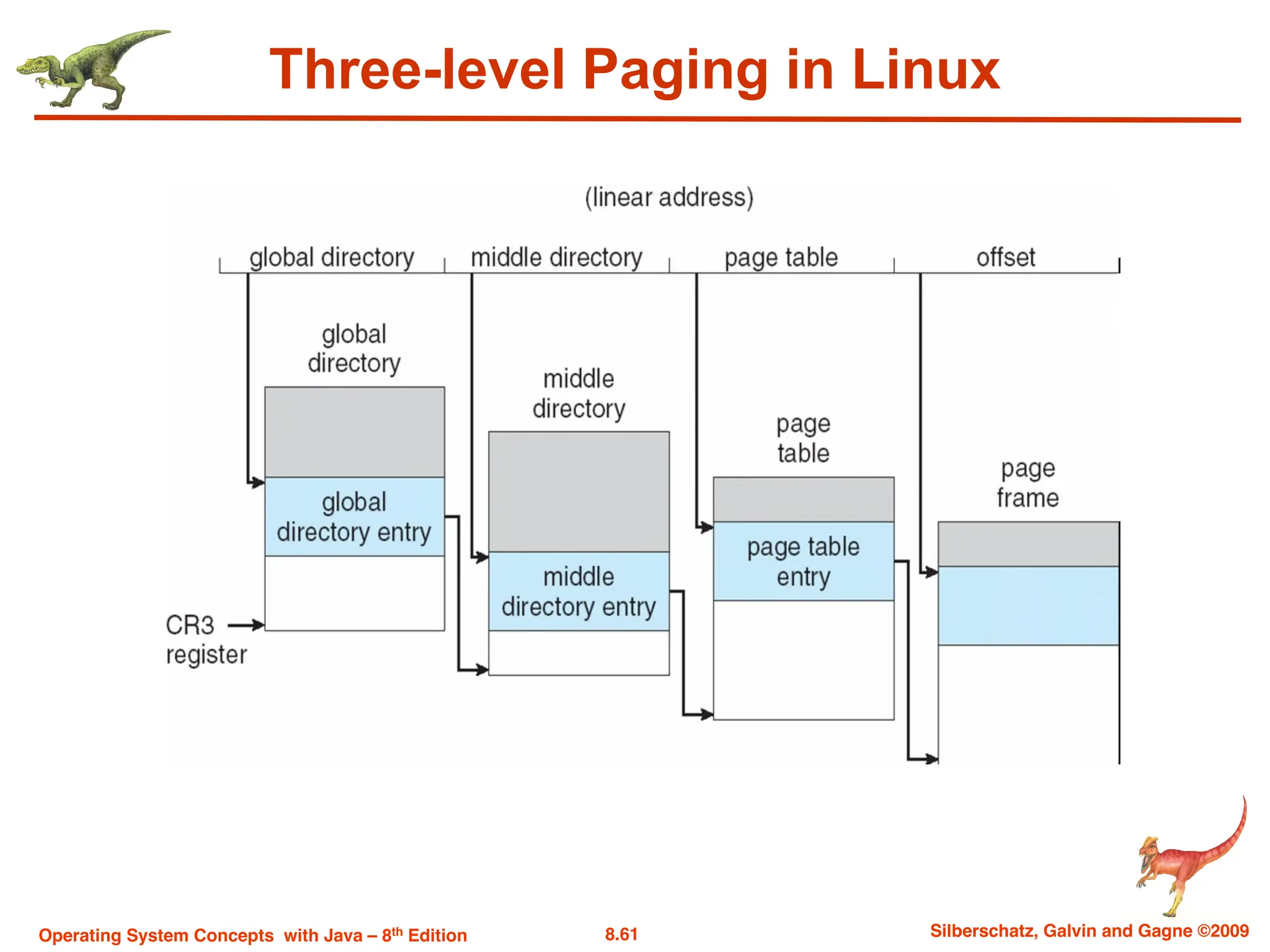

This document provides an overview of memory management techniques in operating systems, including paging, segmentation, and swapping. It discusses how logical and physical addresses are mapped, the use of page tables to translate virtual to physical addresses, and concepts like internal and external fragmentation that occur with different allocation strategies like contiguous allocation. Specific techniques covered include base/limit registers, dynamic loading and linking, and examples of first-fit and best-fit allocation algorithms.