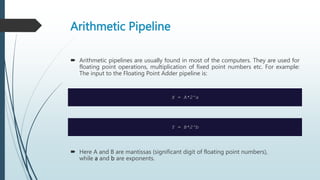

Computer Architecture presentation covers topics like pipelining, VLIW architecture, and loop optimizations. Pipelining allows storing and executing instructions in an orderly process by dividing the instruction cycle into stages. VLIW was invented by Josh Fisher in the 1980s and breaks instructions into basic operations that can execute in parallel. Pipeline scheduling is used to run pipelines at regular intervals and has benefits for continuous integration like automating recurring tasks. Loop unrolling attempts to minimize loop overhead by manually expanding the loop body multiple times.

![Example:

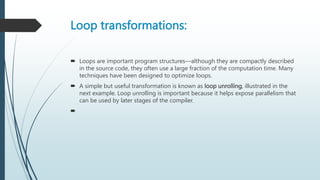

Here is a simple C loop:

for (i = 0; i < N; i++) {

a[i]=b[i]*c[i];

}

This loop is executed a fixed number of times, namely, N.

If we let N = 4, then we can substitute this straight-line code for the loop:

a[0] = b[0]*c[0];

a[1] = b[1]*c[1];

a[2] = b[2]*c[2];

a[3] = b[3]*c[3];](https://image.slidesharecdn.com/1-221208151927-b309514e/85/1-My-Presentation-pptx-26-320.jpg)