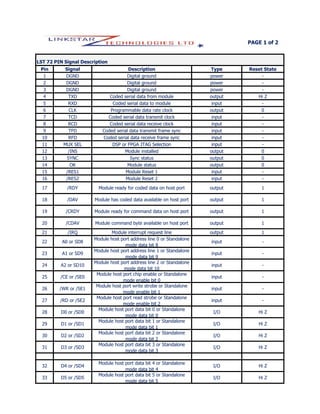

VOCODER LST 72 pin signal data

- 1. PAGE 1 of 2 Pin Signal Description Type Reset State 1 DGND Digital ground power - 2 DGND Digital ground power - 3 DGND Digital ground power - 4 TXD Coded serial data from module output Hi Z 5 RXD Coded serial data to module input - 6 CLK Programmable data rate clock output 0 7 TCD Coded serial data transmit clock input - 8 RCD Coded serial data receive clock input - 9 TFD Coded serial data transmit frame sync input - 10 RFD Coded serial data receive frame sync input - 11 MUX SEL DSP or FPGA JTAG Selection input - 12 /INS Module installed output 0 13 SYNC Sync status output 0 14 OK Module status output 0 15 /RES1 Module Reset 1 input - 16 /RES2 Module Reset 2 input - 17 /RDY Module ready for coded data on host port output 1 18 /DAV Module has coded data available on host port output 1 19 /CRDY Module ready for command data on host port output 1 20 /CDAV Module command byte available on host port output 1 21 /IRQ Module interrupt request line output 1 22 A0 or SD8 Module host port address line 0 or Standalone mode data bit 8 input - 23 A1 or SD9 Module host port address line 1 or Standalone mode data bit 9 input - 24 A2 or SD10 Module host port address line 2 or Standalone mode data bit 10 input - 25 /CE or /SE0 Module host port chip enable or Standalone mode enable bit 0 input - 26 /WR or /SE1 Module host port write strobe or Standalone mode enable bit 1 input - 27 /RD or /SE2 Module host port read strobe or Standalone mode enable bit 2 input - 28 D0 or /SD0 Module host port data bit 0 or Standalone mode data bit 0 I/O Hi Z 29 D1 or /SD1 Module host port data bit 1 or Standalone mode data bit 1 I/O Hi Z 30 D2 or /SD2 Module host port data bit 2 or Standalone mode data bit 2 I/O Hi Z 31 D3 or /SD3 Module host port data bit 3 or Standalone mode data bit 3 I/O Hi Z 32 D4 or /SD4 Module host port data bit 4 or Standalone mode data bit 4 I/O Hi Z 33 D5 or /SD5 Module host port data bit 5 or Standalone mode data bit 5 I/O Hi Z LST 72 PIN Signal Description

- 2. Pin Signal Description Type Reset State 34 D6 or /SD6 Module host port data bit 6 or Standalone mode data bit 6 I/O Hi Z 35 D7 or /SD7 Module host port data bit 7 or Standalone mode data bit 7 I/O Hi Z 36 VDD Module Power(digital) power - 37 VDD Module Power(digital) power - 38 N/C Reserved for factory function N/C - 39 Serial_IN or /SD11 Async Serial IN or Standalone mode data bit 11 input - 40 Serial_OUT or /SD12 Async Serial OUT or Standalone mode data bit 12 output 1 41 Async Sel HOST Serial select or Standalone mode data bit 13 input - 42-48 JTAG Lines DSP and FPGA JTAG Lines N/C - 49 TXP PCM serial data from module output Hi Z 50 RXC PCM serial data to internal CODEC input - 51 RXP PCM serial data to module input - 52 TXC PCM data from internal CODEC output Hi Z 53 TCP PCM transmit clock to module input - 54 RCC PCM receive clock to internal CODEC input - 55 C2M 2.048 MHz clock output 0 56 RCP PCM receive clock to module input - 57 TCC PCM transmit clock to internal CODEC input - 58 TFP PCM transmit frame sync to module input - 59 TFC PCM transmit frame sync to internal CODEC input - 60 C8K 8 kHz frame sync output 0 61 RFP PCM receive frame sync to module input - 62 RFC PCM receive frame sync to internal CODEC input - 63 E1 E-lead signaling output channel #1 output 0 64 E2 E-lead signaling output channel #2 output 0 65 M1 M-lead signaling output channel #1 input - 66 M2 M-lead signaling output channel #2 input - 67 Vcc Power to internal CODEC power - 68 IN+ Non-inverting analog input to internal CODEC input - 69 IN- Inverting analog input to internal CODEC input - 70 AGND Ground for internal CODEC power - 71 OUT+ Non-inverting analog output from internal CODEC output Hi Z 72 OUT- inverting analog output from internal CODEC output Hi Z LST Vocoder Mechanical Data PAGE 2 of 2 ©Linkstar Technologies Ltd, 2016 Product Design & Utility Patents Pending