Report

Share

Recommended

More Related Content

Similar to jp_EDA Tools Proficiency

Similar to jp_EDA Tools Proficiency (20)

Keynote: Machine Learning for Design Automation at DAC 2018

Keynote: Machine Learning for Design Automation at DAC 2018

Overcoming challenges of_verifying complex mixed signal designs

Overcoming challenges of_verifying complex mixed signal designs

Megamodeling of Complex, Distributed, Heterogeneous CPS Systems

Megamodeling of Complex, Distributed, Heterogeneous CPS Systems

jp_EDA Tools Proficiency

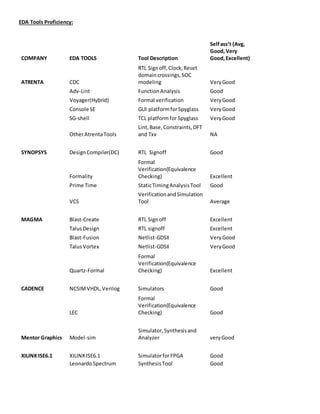

- 1. EDA Tools Proficiency: COMPANY EDA TOOLS Tool Description Selfass’t (Avg, Good,Very Good,Excellent) ATRENTA CDC RTL Signoff,Clock,Reset domaincrossings,SOC modeling VeryGood Adv-Lint FunctionAnalysis Good Voyager(Hybrid) Formal verification VeryGood Console SE GUI platformforSpyglass VeryGood SG-shell TCL platformfor Spyglass VeryGood OtherAtrentaTools Lint,Base,Constraints,DFT and Txv NA SYNOPSYS DesignCompiler(DC) RTL Signoff Good Formality Formal Verification(Equivalence Checking) Excellent Prime Time StaticTimingAnalysisTool Good VCS VerificationandSimulation Tool Average MAGMA Blast-Create RTL Signoff Excellent TalusDesign RTL signoff Excellent Blast-Fusion Netlist-GDSII Very Good TalusVortex Netlist-GDSII VeryGood Quartz-Formal Formal Verification(Equivalence Checking) Excellent CADENCE NCSIMVHDL,Verilog Simulators Good LEC Formal Verification(Equivalence Checking) Good Mentor Graphics Model-sim Simulator,Synthesisand Analyzer veryGood XILINX ISE6.1 XILINXISE6.1 SimulatorforFPGA Good LeonardoSpectrum SynthesisTool Good