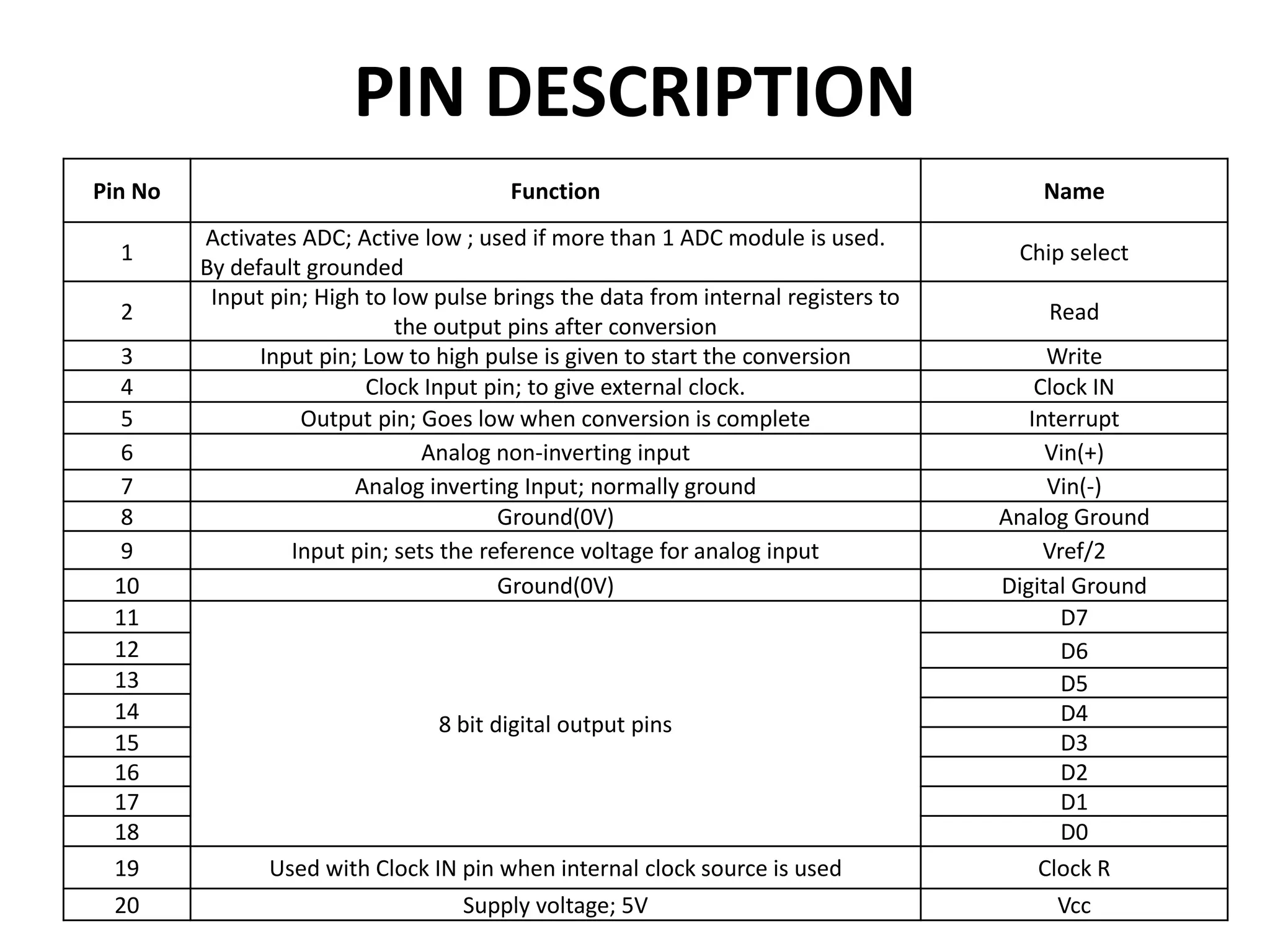

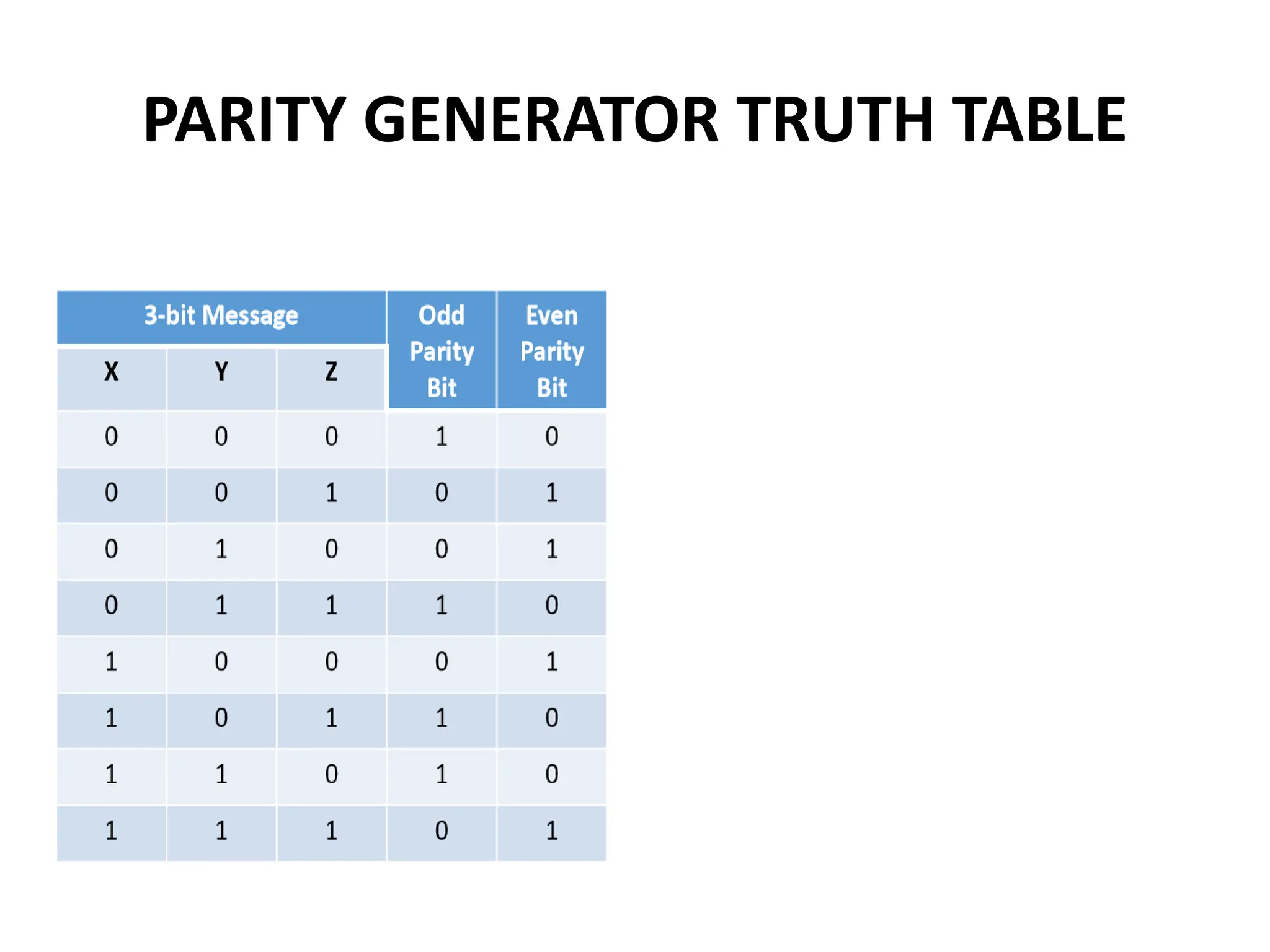

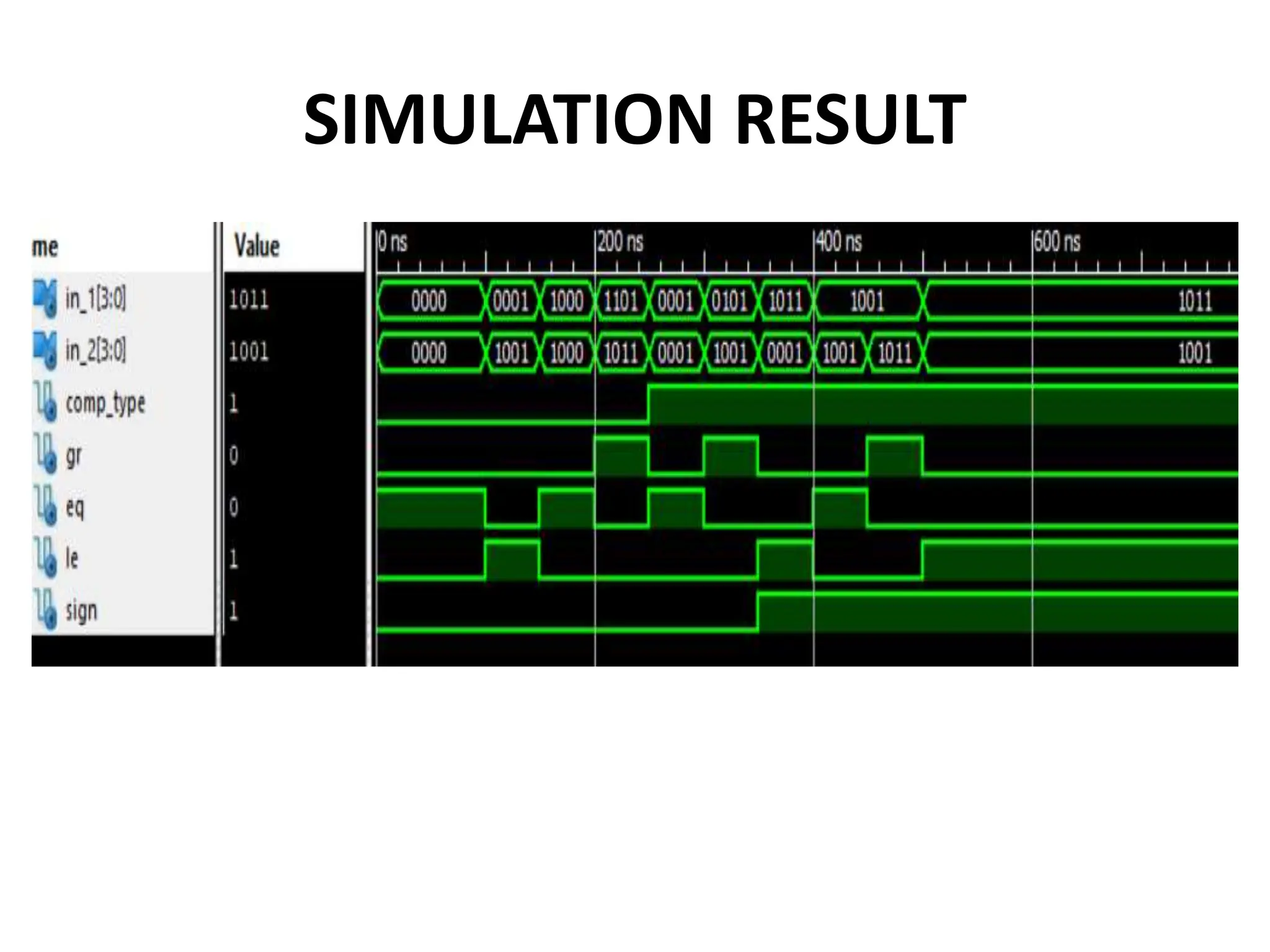

The document details the VHDL code for the ADC0804, a 4-bit magnitude comparator, and a parity generator, including features, pin descriptions, interface schematics, and simulation results. The ADC0804 is an 8-bit parallel analog-to-digital converter ideal for applications requiring moderate accuracy, with a conversion time of up to 100 μs. Additionally, it discusses the functionality of the parity generator for error detection in binary transmissions and the operation of the comparator for multi-bit binary number comparisons.