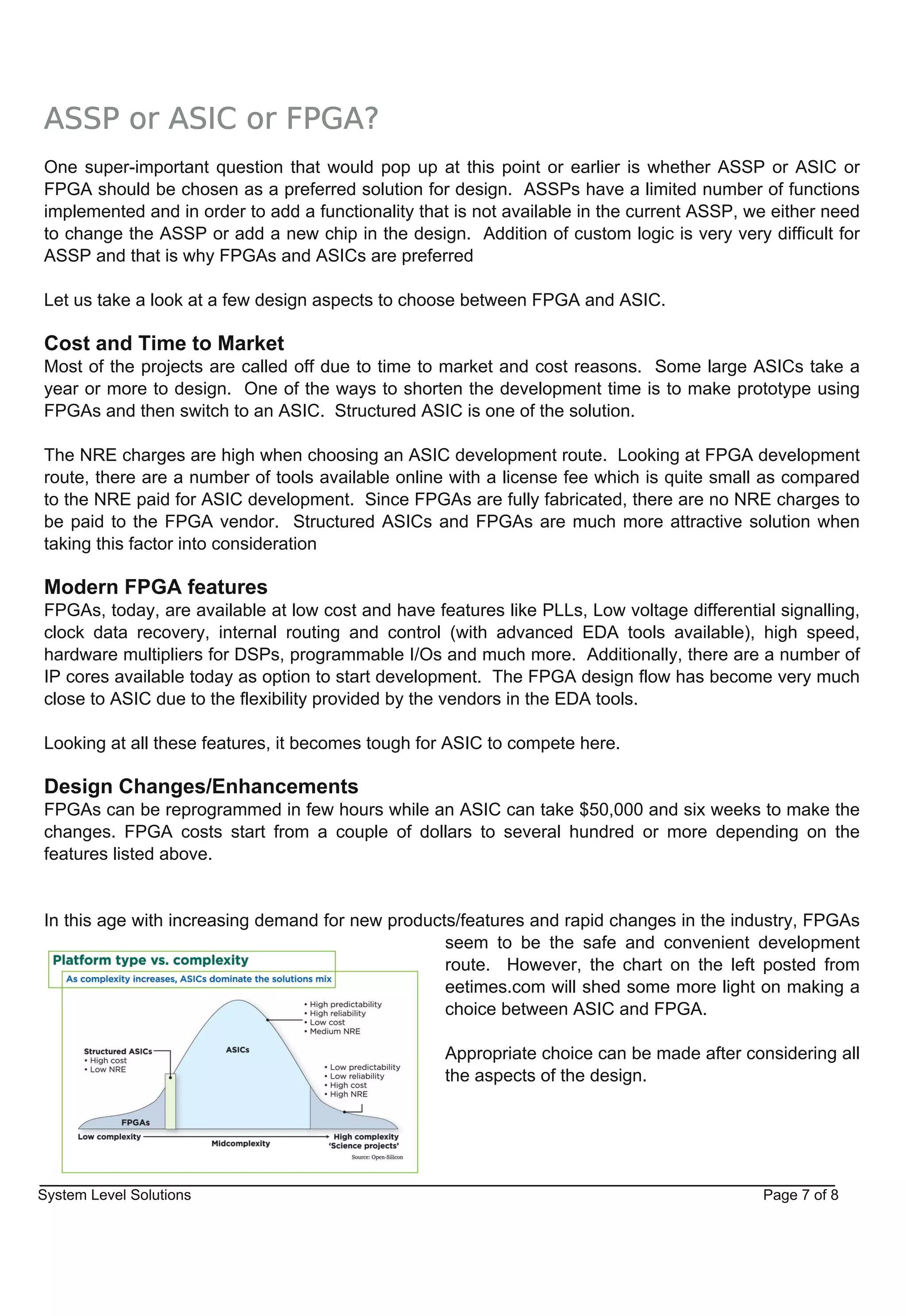

The whitepaper discusses the integration of superspeed USB and NAND flash technologies in various consumer electronics and peripherals, emphasizing the importance of design factors that affect performance and longevity. It outlines key features of superspeed USB, including its high data transfer rates and efficiency compared to USB 2.0, while also detailing the characteristics of NAND flash memory and its usage across devices. Furthermore, it provides insights into development systems available for creating designs that leverage these technologies, highlighting the advantages of FPGAs over ASICs in terms of flexibility and cost-effectiveness.