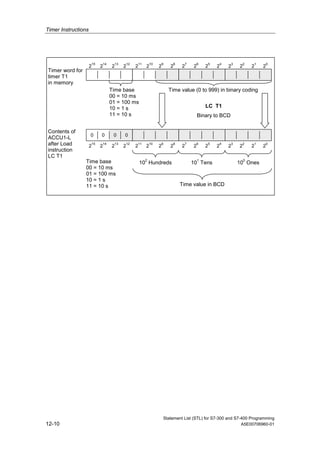

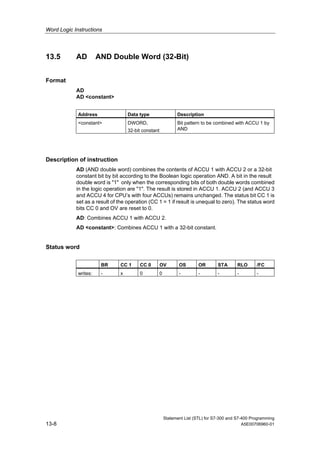

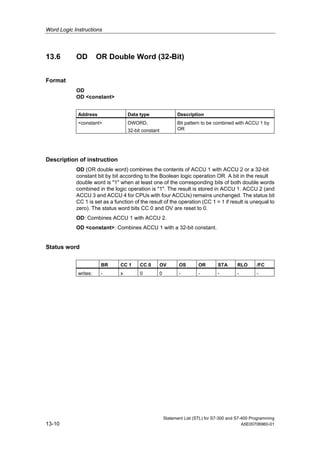

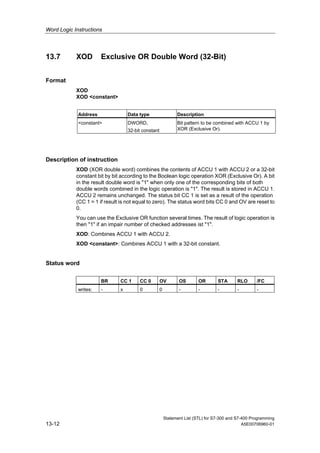

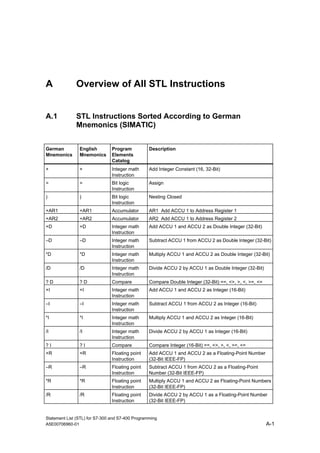

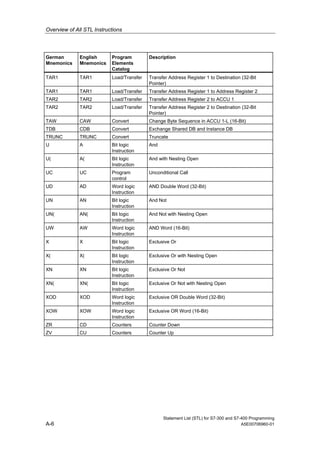

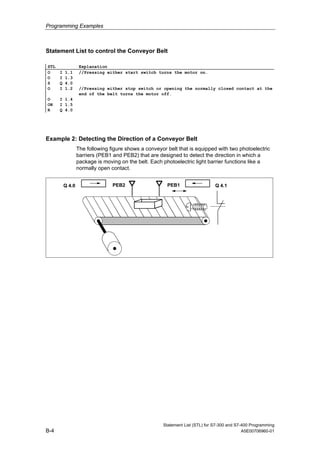

This document provides an overview of the contents and instructions covered in the "Statement List (STL) for S7-300 and S7-400 Programming Reference Manual". The manual describes the STL programming language for Siemens S7-300 and S7-400 programmable logic controllers. It covers bit logic, comparison, conversion, counter, data block, logic control, integer math, floating-point math, load/transfer, program control, shift/rotate, timer and word logic instructions. The document also includes programming examples and information on parameter transfer.