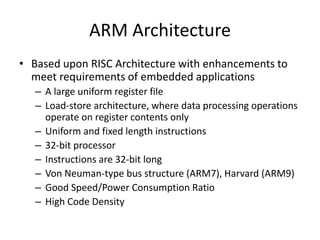

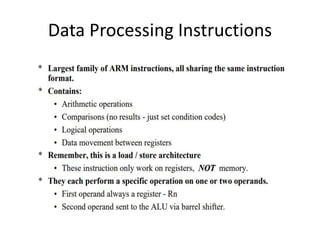

The document discusses the ARM architecture. It describes the history and development of ARM, including being developed in the 1980s in England and the founding of ARM Limited in 1990. It notes ARM is based on the RISC architecture and enhances it for embedded applications. ARM implements both 32-bit and 16-bit instruction sets. The document outlines key features of the ARM architecture like the Thumb instruction set, memory management, register-based operations, conditional execution, and the instruction set categories.

![• In register-indirect addressing, the value

stored in the register is used as the address to

be fetched from memory; the result of that

fetch is the desired operand value.

• LDR r0,[r1]

• LDR r0,[r1, -r2]

• LDR r0,[r1, #4]](https://image.slidesharecdn.com/presentation1-230512052935-deb49223/85/Presentation1-pptx-41-320.jpg)