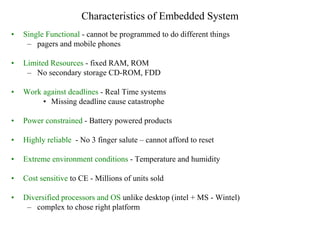

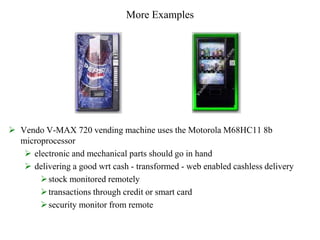

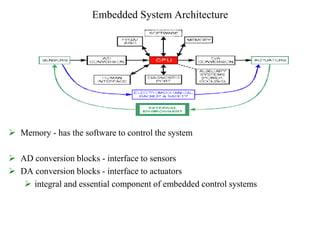

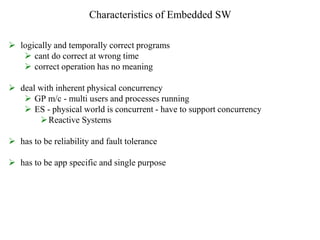

This document discusses embedded systems and their future. Embedded systems like cellular phones, PDAs, and other mobile devices are displacing traditional PCs and laptops. They are shaping the landscape of mobile applications and web. Embedded systems consist of both hardware and software and are designed to perform specific tasks without human intervention by interacting with sensors and actuators. The future of computing lies in embedded systems of the 21st century.