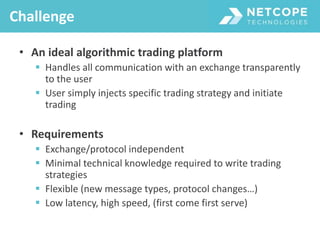

Netcope Technologies offers low-latency FPGA-based solutions for algorithmic and high-frequency trading, emphasizing flexibility and ease of use. Their platform supports various trading protocols and ensures minimal tick-to-trade latency while allowing users to implement custom trading strategies. Key features include pre-trade risk checks and customizable monitoring capabilities, enabling efficient and secure trading operations with multiple exchanges.