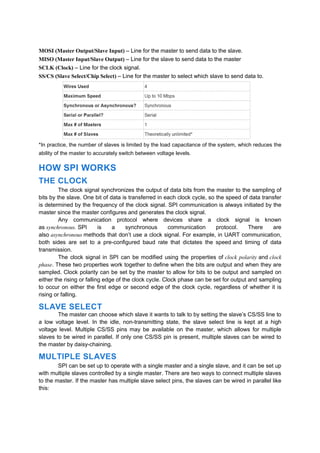

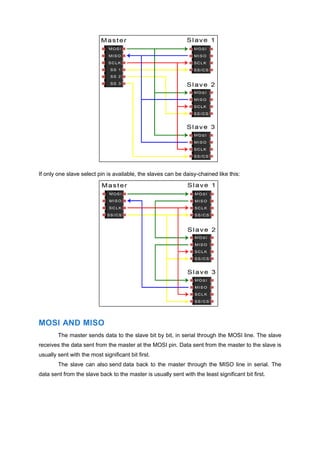

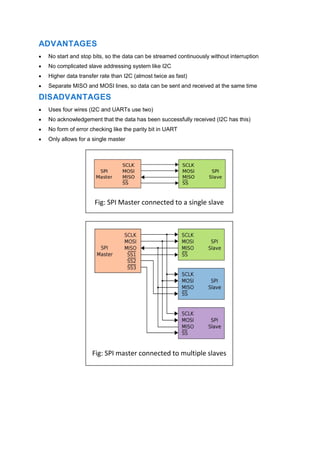

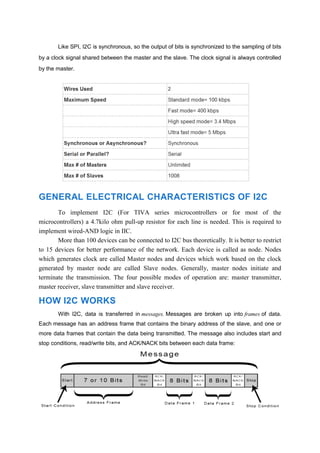

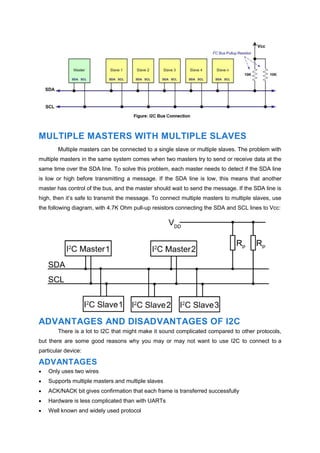

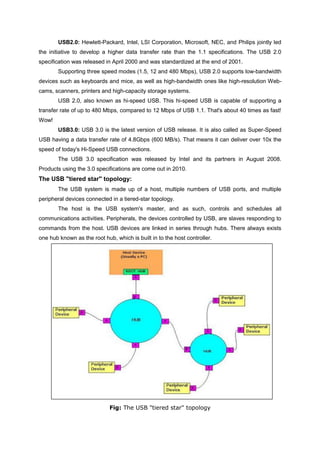

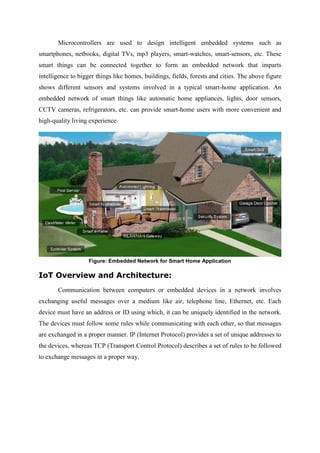

The document discusses embedded communication protocols, focusing on three common protocols: SPI, I2C, and UART. It explains the basics of data transmission methods, including parallel and serial communication, detailing their advantages and disadvantages. Additionally, it highlights how these protocols work in microcontrollers, their implementation, and practical applications in electronic projects.