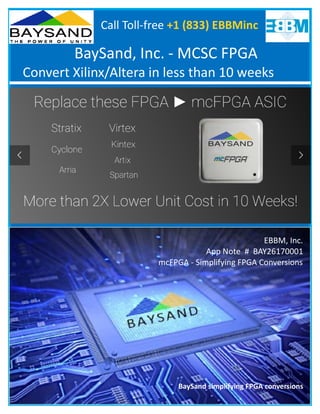

Convert Altera Xilinx FPGA to BaySand mcFPGA

•

1 like•216 views

BaySand offers several configurable logic platforms including the mcFPGA, which can replace Xilinx/Altera FPGAs with up to 10x power reduction, 5x performance improvement, and 10x lower price. The mcFPGA uses BaySand's MCSC technology and can be delivered in packaged and tested form within 7-10 weeks from receiving the customer's RTL design. BaySand's comprehensive solution includes logic platforms, cell libraries, I/Os, memory, PLLs, PHYs, transceivers and tools to implement complete custom logic designs.

Report

Share

Report

Share

Download to read offline

Recommended

Selvakumar Maniyan - Resume - Jan 2016

Selvakumar Maniyan has over 15 years of experience implementing and troubleshooting complex network systems including routing, switching, IP address management, and network security. He has worked on projects for companies such as Tata Consultancy Services, Agilent Technologies, and Society for Electronic Transactions and Security. His technical skills include Cisco, Juniper, Alcatel-Lucent, F5 Load Balancers, and Bluecat IPAM. He has experience designing, implementing, and managing data center networks, WANs, wireless networks, and network security configurations.

State Of FPGA: Current & Future - A Panel discussion @ 4th FPGA Camp

The panelists discussed their views on the current state and future of FPGAs. Mark expressed concerns about soft error rates and power densities in high-end FPGAs. Gordon said the industry is healthy but the race to more logic cells has pushed single architectures. Daniel said the line between FPGAs and ASICs is blurring and more niche and application-specific solutions will emerge. Chris said higher-level design flows will be needed to meet complexity demands. Umar viewed FPGAs as programmable processing engines well-suited for product architecture risk.

Milestones Achieved Rd Catiller

The document outlines several milestones and accomplishments in the person's career developing computer systems and components. They developed new methods for detecting microcode memory failures, designed performance monitoring and communication systems, completed software for a communications project, designed a data acquisition system for racing, and developed models and systems for disk drive validation. Their work resulted in several patents and positions at companies, and they now operate their own consulting business.

Client Virtualization reference architacture- cn

This document discusses HP desktop virtualization reference architectures. It begins by introducing HP Virtual Connect technology and the StorageWorks P4000 SAN for desktop virtualization. It then presents a reference architecture for HP desktop virtualization built upon the StorageWorks P4800 SAN. The architecture is capable of accommodating up to 1,600 productivity users using VMware View, Hyper-V, or Citrix XenDesktop with HP BladeSystems, Flex-10 networking, SAN/iQ storage software, and Insight Control management.

Frost & Sullivan Whitepaper: How to achieve and all IP platform using switch ...

Compelling whitepaper highlighting the benefits of using Long Reach PoE innovation to move to an all IP platform

Resource guide-30th-edition

ATTO manufactures a broad portfolio of high-performance storage and network connectivity products designed to work together to help customers better store, manage, analyze and deliver data. Their products include Fibre Channel, SAS/SATA, iSCSI, Ethernet, FCoE, and Thunderbolt host bus adapters (HBAs), RAID adapters, network interface cards (NICs), storage controllers, switches, Thunderbolt adapters, and software. ATTO provides tested solutions qualified with leading vendors in workstations, servers, storage and applications.

#IBMEdge: Flash Storage Session

IBM FlashSystem and other SSD's are being adopted for OLTP and Analytics applications. Fast 16Gb Flash storage requires a reliable, high performance network to ensure applications can utilize it effectively. Learn how to plan for a highspeed reliable network to handle the increased demands while delivering reliable application response times. Understand the reliability, performance, and simplified management features of Gen5 FC and Fabric Vision. Be prepared for the next jump in SAN's.

Is Your Network Ready?

Fibre channel is on the rise, and the data center transformation is upon us! Join Brocade's Technical Development Manager, Mike Naylor as he explains how Brocade Gen5 Fabric can simplify your network infrastructure, reduce costs and maximize uptime.

Recommended

Selvakumar Maniyan - Resume - Jan 2016

Selvakumar Maniyan has over 15 years of experience implementing and troubleshooting complex network systems including routing, switching, IP address management, and network security. He has worked on projects for companies such as Tata Consultancy Services, Agilent Technologies, and Society for Electronic Transactions and Security. His technical skills include Cisco, Juniper, Alcatel-Lucent, F5 Load Balancers, and Bluecat IPAM. He has experience designing, implementing, and managing data center networks, WANs, wireless networks, and network security configurations.

State Of FPGA: Current & Future - A Panel discussion @ 4th FPGA Camp

The panelists discussed their views on the current state and future of FPGAs. Mark expressed concerns about soft error rates and power densities in high-end FPGAs. Gordon said the industry is healthy but the race to more logic cells has pushed single architectures. Daniel said the line between FPGAs and ASICs is blurring and more niche and application-specific solutions will emerge. Chris said higher-level design flows will be needed to meet complexity demands. Umar viewed FPGAs as programmable processing engines well-suited for product architecture risk.

Milestones Achieved Rd Catiller

The document outlines several milestones and accomplishments in the person's career developing computer systems and components. They developed new methods for detecting microcode memory failures, designed performance monitoring and communication systems, completed software for a communications project, designed a data acquisition system for racing, and developed models and systems for disk drive validation. Their work resulted in several patents and positions at companies, and they now operate their own consulting business.

Client Virtualization reference architacture- cn

This document discusses HP desktop virtualization reference architectures. It begins by introducing HP Virtual Connect technology and the StorageWorks P4000 SAN for desktop virtualization. It then presents a reference architecture for HP desktop virtualization built upon the StorageWorks P4800 SAN. The architecture is capable of accommodating up to 1,600 productivity users using VMware View, Hyper-V, or Citrix XenDesktop with HP BladeSystems, Flex-10 networking, SAN/iQ storage software, and Insight Control management.

Frost & Sullivan Whitepaper: How to achieve and all IP platform using switch ...

Compelling whitepaper highlighting the benefits of using Long Reach PoE innovation to move to an all IP platform

Resource guide-30th-edition

ATTO manufactures a broad portfolio of high-performance storage and network connectivity products designed to work together to help customers better store, manage, analyze and deliver data. Their products include Fibre Channel, SAS/SATA, iSCSI, Ethernet, FCoE, and Thunderbolt host bus adapters (HBAs), RAID adapters, network interface cards (NICs), storage controllers, switches, Thunderbolt adapters, and software. ATTO provides tested solutions qualified with leading vendors in workstations, servers, storage and applications.

#IBMEdge: Flash Storage Session

IBM FlashSystem and other SSD's are being adopted for OLTP and Analytics applications. Fast 16Gb Flash storage requires a reliable, high performance network to ensure applications can utilize it effectively. Learn how to plan for a highspeed reliable network to handle the increased demands while delivering reliable application response times. Understand the reliability, performance, and simplified management features of Gen5 FC and Fabric Vision. Be prepared for the next jump in SAN's.

Is Your Network Ready?

Fibre channel is on the rise, and the data center transformation is upon us! Join Brocade's Technical Development Manager, Mike Naylor as he explains how Brocade Gen5 Fabric can simplify your network infrastructure, reduce costs and maximize uptime.

SoC~FPGA~ASIC~Embedded

Jasmin Ibrahimovic is a senior design and verification consultant with over 20 years of experience in FPGA, SoC, and ASIC development. She specializes in hardware-assisted computing, interfaces, and microarchitectures. She has worked on mission-critical and carrier-class electronic products across various industries including computing, networking, wireless, and more. Her experience includes roles at Qualcomm, Chili.CHIPS, AMCC, Copper Mountain Networks, Nortel Networks, Gandalf Data, and Energoinvest/IRCA.

Who Is This Guy?

This document provides biographical information about an experienced engineer with expertise in system-on-chip (SoC) design, field-programmable gate array (FPGA) design, application-specific integrated circuit (ASIC) design, embedded systems design, and high-speed serial connectivity. The engineer has over 20 years of experience in the electronics industry working on advanced product developments. Educational background includes a BSEE degree and professional training in areas like SoC design, FPGA design, Verilog, system verification, and more. References and samples of past work are also provided.

hyperlynx_compress.pdf

This document discusses using Mentor Graphics tools like Hyperlynx SI and PI to analyze signal and power integrity for PCB designs. It covers pre-layout and post-layout simulations that can be used to develop design rules and verify signal quality. Specific analysis techniques are described like modeling IC behavior, developing termination strategies, and evaluating power delivery networks.

TechWiseTV Workshop: Programmable ASICs

Why trade performance for flexibility when you can program your network with new protocols and capabilities at wire speed?

In this workshop learn how ASICs are made, why flexible silicon is critical to the future of networking and what you can do with Cisco’s next-generation UADP 2.0.

Resources:

Watch the related TechWiseTV episode: http://bit.ly/2fiqH1f

Watch the TechWiseTV: New Era in Networking playlist: http://bit.ly/2jpoRjB

s2c-success-story-penstar.pdf

Penstar Technology is a leading Chinese IC design company that focuses on SoC products for digital TV and mobile devices. They needed to test a demux design but developing an FPGA prototyping board and the associated software would take too much time. Using S2C's FPGA prototyping system and C-API software, Penstar was able to quickly implement their demux design on FPGA and transmit large test stimuli via PCIe. This allowed them to reduce costs and the design cycle time. The setup allowed Penstar to run extensive tests via a C program that accessed FPGA memory, helping verify the design and launch their SoC to market faster.

resume_jason_v1

Jason Chang has over 15 years of experience in ASIC design and verification. He has worked at companies including AMD, Broadcom, and Allied Telesyn. His experience includes architecting and integrating USB and PCIe IP into server and client SOCs at AMD. He has expertise in Verilog, synthesis tools, and protocol integration.

scottjgriffith_CV

The document is a resume for Scott J. Griffith, an integrated circuit engineering consultant. It details his experience in custom integrated circuit design, CAD development, and providing analysis services including deconstruction of semiconductor devices, circuit extraction, and expert witness testimony. It lists his areas of expertise, technical skills, programming languages, and over 30 years of experience, including currently as principal of his own consulting firm and previously at Sun Microsystems as a senior engineer and manager.

Detailed Cv

This document is a resume for Mohamed Yousef Abdulghany Elmasry that includes his contact information, objective, education history, related experience working as a senior hardware/logic design engineer and network design engineer, skills including expertise in VHDL, embedded software and hardware design, and recent projects involving designing hardware security cores, communication protocols, and embedded systems.

s2c-success-story-ingenic.pdf

Ingenic faced challenges in verifying their innovative XBurst CPU technology due to limitations of their FPGA prototyping boards. S2C's high-capacity FPGA prototyping solutions using Prodigy Logic Modules allowed Ingenic to verify nearly their entire design in 1-2 days rather than weeks or months. This helped Ingenic optimize their development process, reduce risks, and get to market faster. Ingenic was impressed by S2C's support, reliability, and flexibility and plans continued collaboration using S2C's solutions to prototype future projects.

Asic

Application specific integrated circuits (ASICs) are microchips designed for special applications. There are two types: full-custom ASICs where all logic cells and mask layers are customized, and semi-custom where pre-designed logic cells have some customizable mask layers. ASICs have advantages over FPGAs like lower costs, higher speeds, and lower power usage, but have higher design costs and longer development times. Common applications of ASICs include aerospace systems, high-performance processors, and specialized consumer electronics.

Resume_A0

Michael Young is seeking an engineering position in southern California. He has over 25 years of experience in hardware and system design, including expertise in electronics, interfaces, power regulation, and PCB design. Previous roles include principal engineer at SMART Modular developing a NVDIMM product, hardware engineer at QLogic designing Fibre Channel adapters, and staff engineer at STEC designing an SSD. He has a Master's and Bachelor's in Electrical Engineering from Texas Tech University.

Resume_Bhasker

Bhasker has over 5 years of experience in PCB layout design and engineering. He has designed boards with high speed signals like DDR3, PCIe, and USB. Some of his project experience includes designing a 26 layer board with a 1mm BGA and high speed interfaces, and boards using Intel and ARM processors. He is proficient in Cadence Allegro and has experience across the entire design flow from schematics to fabrication files.

Traditional vs. SoC FPGA Design Flow A Video Pipeline Case Study

This presentation compares the impact of traditional FPGA engineering design flow to one employed with an SoC FPGA. The two approaches will be contrasted in terms of their impacts on system architecture design, debugging, risk mitigation, system integration, bring-up, feature enhancements, design obsolescence, and engineering effort. A case study is presented that explores these impacts within a video pipeline development effort.

Jay_Vicory_Resume_2018

This document contains a summary of Jay Vicory's professional experience and qualifications. It lists his contact information, followed by summaries of his engineering practice and management experience, formal education, and various engineering roles held from 2004 to the present. These roles involved developing embedded systems, hardware, firmware, software and managing projects for clients in industries such as audio, defense, and semiconductor development.

s2c-success-story-leadcore.pdf

Leadcore is a Chinese company that develops TD-LTE networking solutions including chips and terminals. They used S2C's FPGA-based rapid prototyping solutions to reduce development time and risks for their TD-LTE SoC design. The scalability and cost-effectiveness of S2C's solutions allowed Leadcore to concurrently develop driver software and verify algorithms. This improved the performance of Leadcore's TD-LTE products while shortening their design cycle. Leadcore was impressed by S2C's support and sees opportunities for long-term cooperation on future designs.

Vamsi_Resume

Vamsi Krishna is a seasoned IT professional with over 18 years of experience in infrastructure solutions such as networking, security, unified communications, and data centers. He has expertise in designing technical solutions and architectures for LAN, WAN, wireless networks, security, unified communications, and data centers. He is seeking a challenging position as a solutions architect where he can design technical solutions and architectures to meet customer requirements.

Peaceful coexistence among architectures

Title: Peaceful coexistence among architectures

Author: Andreas Olofsson

Location: Panel, HPEC 2009

Date: September 2009

MohanMG_Professional CV

MohanMelakadambur Ganesan has over 21 years of experience in hardware system architecture and team leadership in R&D. He has extensive expertise in analog and digital electronics design, microprocessor design, FPGA design, power supply design, and PCB layout. Some of his past projects include developing medical monitoring systems, SOHO networking platforms, wireless infrastructure equipment, and high-speed video storage systems. He is proficient in various EDA tools, embedded firmware, and regulatory certifications like EMI/EMC. He aims to utilize his skills and multi-domain experience to contribute to innovative technology products.

hjsklar CV

This document provides a summary of Horace Sklar's technical experience as a project manager, principal engineer, and technical consultant. Over his 35+ year career, he has specialized in digital signal and image processing system design for military and defense applications. Some of his areas of expertise include FPGA and ASIC design, hardware/software integration, requirements analysis, and project management. He has worked on numerous defense contracts involving satellite payloads, airborne systems, and ground-based detection systems.

lith-guest-lecture-2015

This document discusses system design and SoC/ASIC design at Ericsson. It covers mobile network infrastructure including radio base stations. It describes the cellular technology roadmap and increasing requirements for signal processing. It discusses systemization which aims to find the optimal combination of hardware and software components considering performance, cost, power, flexibility, and other factors. The document contrasts hardware and software solutions in terms of these trade-offs. It provides an example of random access and demodulation hardware design for a WCDMA receiver.

Skybuffer AI: Advanced Conversational and Generative AI Solution on SAP Busin...

Skybuffer AI, built on the robust SAP Business Technology Platform (SAP BTP), is the latest and most advanced version of our AI development, reaffirming our commitment to delivering top-tier AI solutions. Skybuffer AI harnesses all the innovative capabilities of the SAP BTP in the AI domain, from Conversational AI to cutting-edge Generative AI and Retrieval-Augmented Generation (RAG). It also helps SAP customers safeguard their investments into SAP Conversational AI and ensure a seamless, one-click transition to SAP Business AI.

With Skybuffer AI, various AI models can be integrated into a single communication channel such as Microsoft Teams. This integration empowers business users with insights drawn from SAP backend systems, enterprise documents, and the expansive knowledge of Generative AI. And the best part of it is that it is all managed through our intuitive no-code Action Server interface, requiring no extensive coding knowledge and making the advanced AI accessible to more users.

Monitoring and Managing Anomaly Detection on OpenShift.pdf

Monitoring and Managing Anomaly Detection on OpenShift

Overview

Dive into the world of anomaly detection on edge devices with our comprehensive hands-on tutorial. This SlideShare presentation will guide you through the entire process, from data collection and model training to edge deployment and real-time monitoring. Perfect for those looking to implement robust anomaly detection systems on resource-constrained IoT/edge devices.

Key Topics Covered

1. Introduction to Anomaly Detection

- Understand the fundamentals of anomaly detection and its importance in identifying unusual behavior or failures in systems.

2. Understanding Edge (IoT)

- Learn about edge computing and IoT, and how they enable real-time data processing and decision-making at the source.

3. What is ArgoCD?

- Discover ArgoCD, a declarative, GitOps continuous delivery tool for Kubernetes, and its role in deploying applications on edge devices.

4. Deployment Using ArgoCD for Edge Devices

- Step-by-step guide on deploying anomaly detection models on edge devices using ArgoCD.

5. Introduction to Apache Kafka and S3

- Explore Apache Kafka for real-time data streaming and Amazon S3 for scalable storage solutions.

6. Viewing Kafka Messages in the Data Lake

- Learn how to view and analyze Kafka messages stored in a data lake for better insights.

7. What is Prometheus?

- Get to know Prometheus, an open-source monitoring and alerting toolkit, and its application in monitoring edge devices.

8. Monitoring Application Metrics with Prometheus

- Detailed instructions on setting up Prometheus to monitor the performance and health of your anomaly detection system.

9. What is Camel K?

- Introduction to Camel K, a lightweight integration framework built on Apache Camel, designed for Kubernetes.

10. Configuring Camel K Integrations for Data Pipelines

- Learn how to configure Camel K for seamless data pipeline integrations in your anomaly detection workflow.

11. What is a Jupyter Notebook?

- Overview of Jupyter Notebooks, an open-source web application for creating and sharing documents with live code, equations, visualizations, and narrative text.

12. Jupyter Notebooks with Code Examples

- Hands-on examples and code snippets in Jupyter Notebooks to help you implement and test anomaly detection models.

More Related Content

Similar to Convert Altera Xilinx FPGA to BaySand mcFPGA

SoC~FPGA~ASIC~Embedded

Jasmin Ibrahimovic is a senior design and verification consultant with over 20 years of experience in FPGA, SoC, and ASIC development. She specializes in hardware-assisted computing, interfaces, and microarchitectures. She has worked on mission-critical and carrier-class electronic products across various industries including computing, networking, wireless, and more. Her experience includes roles at Qualcomm, Chili.CHIPS, AMCC, Copper Mountain Networks, Nortel Networks, Gandalf Data, and Energoinvest/IRCA.

Who Is This Guy?

This document provides biographical information about an experienced engineer with expertise in system-on-chip (SoC) design, field-programmable gate array (FPGA) design, application-specific integrated circuit (ASIC) design, embedded systems design, and high-speed serial connectivity. The engineer has over 20 years of experience in the electronics industry working on advanced product developments. Educational background includes a BSEE degree and professional training in areas like SoC design, FPGA design, Verilog, system verification, and more. References and samples of past work are also provided.

hyperlynx_compress.pdf

This document discusses using Mentor Graphics tools like Hyperlynx SI and PI to analyze signal and power integrity for PCB designs. It covers pre-layout and post-layout simulations that can be used to develop design rules and verify signal quality. Specific analysis techniques are described like modeling IC behavior, developing termination strategies, and evaluating power delivery networks.

TechWiseTV Workshop: Programmable ASICs

Why trade performance for flexibility when you can program your network with new protocols and capabilities at wire speed?

In this workshop learn how ASICs are made, why flexible silicon is critical to the future of networking and what you can do with Cisco’s next-generation UADP 2.0.

Resources:

Watch the related TechWiseTV episode: http://bit.ly/2fiqH1f

Watch the TechWiseTV: New Era in Networking playlist: http://bit.ly/2jpoRjB

s2c-success-story-penstar.pdf

Penstar Technology is a leading Chinese IC design company that focuses on SoC products for digital TV and mobile devices. They needed to test a demux design but developing an FPGA prototyping board and the associated software would take too much time. Using S2C's FPGA prototyping system and C-API software, Penstar was able to quickly implement their demux design on FPGA and transmit large test stimuli via PCIe. This allowed them to reduce costs and the design cycle time. The setup allowed Penstar to run extensive tests via a C program that accessed FPGA memory, helping verify the design and launch their SoC to market faster.

resume_jason_v1

Jason Chang has over 15 years of experience in ASIC design and verification. He has worked at companies including AMD, Broadcom, and Allied Telesyn. His experience includes architecting and integrating USB and PCIe IP into server and client SOCs at AMD. He has expertise in Verilog, synthesis tools, and protocol integration.

scottjgriffith_CV

The document is a resume for Scott J. Griffith, an integrated circuit engineering consultant. It details his experience in custom integrated circuit design, CAD development, and providing analysis services including deconstruction of semiconductor devices, circuit extraction, and expert witness testimony. It lists his areas of expertise, technical skills, programming languages, and over 30 years of experience, including currently as principal of his own consulting firm and previously at Sun Microsystems as a senior engineer and manager.

Detailed Cv

This document is a resume for Mohamed Yousef Abdulghany Elmasry that includes his contact information, objective, education history, related experience working as a senior hardware/logic design engineer and network design engineer, skills including expertise in VHDL, embedded software and hardware design, and recent projects involving designing hardware security cores, communication protocols, and embedded systems.

s2c-success-story-ingenic.pdf

Ingenic faced challenges in verifying their innovative XBurst CPU technology due to limitations of their FPGA prototyping boards. S2C's high-capacity FPGA prototyping solutions using Prodigy Logic Modules allowed Ingenic to verify nearly their entire design in 1-2 days rather than weeks or months. This helped Ingenic optimize their development process, reduce risks, and get to market faster. Ingenic was impressed by S2C's support, reliability, and flexibility and plans continued collaboration using S2C's solutions to prototype future projects.

Asic

Application specific integrated circuits (ASICs) are microchips designed for special applications. There are two types: full-custom ASICs where all logic cells and mask layers are customized, and semi-custom where pre-designed logic cells have some customizable mask layers. ASICs have advantages over FPGAs like lower costs, higher speeds, and lower power usage, but have higher design costs and longer development times. Common applications of ASICs include aerospace systems, high-performance processors, and specialized consumer electronics.

Resume_A0

Michael Young is seeking an engineering position in southern California. He has over 25 years of experience in hardware and system design, including expertise in electronics, interfaces, power regulation, and PCB design. Previous roles include principal engineer at SMART Modular developing a NVDIMM product, hardware engineer at QLogic designing Fibre Channel adapters, and staff engineer at STEC designing an SSD. He has a Master's and Bachelor's in Electrical Engineering from Texas Tech University.

Resume_Bhasker

Bhasker has over 5 years of experience in PCB layout design and engineering. He has designed boards with high speed signals like DDR3, PCIe, and USB. Some of his project experience includes designing a 26 layer board with a 1mm BGA and high speed interfaces, and boards using Intel and ARM processors. He is proficient in Cadence Allegro and has experience across the entire design flow from schematics to fabrication files.

Traditional vs. SoC FPGA Design Flow A Video Pipeline Case Study

This presentation compares the impact of traditional FPGA engineering design flow to one employed with an SoC FPGA. The two approaches will be contrasted in terms of their impacts on system architecture design, debugging, risk mitigation, system integration, bring-up, feature enhancements, design obsolescence, and engineering effort. A case study is presented that explores these impacts within a video pipeline development effort.

Jay_Vicory_Resume_2018

This document contains a summary of Jay Vicory's professional experience and qualifications. It lists his contact information, followed by summaries of his engineering practice and management experience, formal education, and various engineering roles held from 2004 to the present. These roles involved developing embedded systems, hardware, firmware, software and managing projects for clients in industries such as audio, defense, and semiconductor development.

s2c-success-story-leadcore.pdf

Leadcore is a Chinese company that develops TD-LTE networking solutions including chips and terminals. They used S2C's FPGA-based rapid prototyping solutions to reduce development time and risks for their TD-LTE SoC design. The scalability and cost-effectiveness of S2C's solutions allowed Leadcore to concurrently develop driver software and verify algorithms. This improved the performance of Leadcore's TD-LTE products while shortening their design cycle. Leadcore was impressed by S2C's support and sees opportunities for long-term cooperation on future designs.

Vamsi_Resume

Vamsi Krishna is a seasoned IT professional with over 18 years of experience in infrastructure solutions such as networking, security, unified communications, and data centers. He has expertise in designing technical solutions and architectures for LAN, WAN, wireless networks, security, unified communications, and data centers. He is seeking a challenging position as a solutions architect where he can design technical solutions and architectures to meet customer requirements.

Peaceful coexistence among architectures

Title: Peaceful coexistence among architectures

Author: Andreas Olofsson

Location: Panel, HPEC 2009

Date: September 2009

MohanMG_Professional CV

MohanMelakadambur Ganesan has over 21 years of experience in hardware system architecture and team leadership in R&D. He has extensive expertise in analog and digital electronics design, microprocessor design, FPGA design, power supply design, and PCB layout. Some of his past projects include developing medical monitoring systems, SOHO networking platforms, wireless infrastructure equipment, and high-speed video storage systems. He is proficient in various EDA tools, embedded firmware, and regulatory certifications like EMI/EMC. He aims to utilize his skills and multi-domain experience to contribute to innovative technology products.

hjsklar CV

This document provides a summary of Horace Sklar's technical experience as a project manager, principal engineer, and technical consultant. Over his 35+ year career, he has specialized in digital signal and image processing system design for military and defense applications. Some of his areas of expertise include FPGA and ASIC design, hardware/software integration, requirements analysis, and project management. He has worked on numerous defense contracts involving satellite payloads, airborne systems, and ground-based detection systems.

lith-guest-lecture-2015

This document discusses system design and SoC/ASIC design at Ericsson. It covers mobile network infrastructure including radio base stations. It describes the cellular technology roadmap and increasing requirements for signal processing. It discusses systemization which aims to find the optimal combination of hardware and software components considering performance, cost, power, flexibility, and other factors. The document contrasts hardware and software solutions in terms of these trade-offs. It provides an example of random access and demodulation hardware design for a WCDMA receiver.

Similar to Convert Altera Xilinx FPGA to BaySand mcFPGA (20)

Traditional vs. SoC FPGA Design Flow A Video Pipeline Case Study

Traditional vs. SoC FPGA Design Flow A Video Pipeline Case Study

Recently uploaded

Skybuffer AI: Advanced Conversational and Generative AI Solution on SAP Busin...

Skybuffer AI, built on the robust SAP Business Technology Platform (SAP BTP), is the latest and most advanced version of our AI development, reaffirming our commitment to delivering top-tier AI solutions. Skybuffer AI harnesses all the innovative capabilities of the SAP BTP in the AI domain, from Conversational AI to cutting-edge Generative AI and Retrieval-Augmented Generation (RAG). It also helps SAP customers safeguard their investments into SAP Conversational AI and ensure a seamless, one-click transition to SAP Business AI.

With Skybuffer AI, various AI models can be integrated into a single communication channel such as Microsoft Teams. This integration empowers business users with insights drawn from SAP backend systems, enterprise documents, and the expansive knowledge of Generative AI. And the best part of it is that it is all managed through our intuitive no-code Action Server interface, requiring no extensive coding knowledge and making the advanced AI accessible to more users.

Monitoring and Managing Anomaly Detection on OpenShift.pdf

Monitoring and Managing Anomaly Detection on OpenShift

Overview

Dive into the world of anomaly detection on edge devices with our comprehensive hands-on tutorial. This SlideShare presentation will guide you through the entire process, from data collection and model training to edge deployment and real-time monitoring. Perfect for those looking to implement robust anomaly detection systems on resource-constrained IoT/edge devices.

Key Topics Covered

1. Introduction to Anomaly Detection

- Understand the fundamentals of anomaly detection and its importance in identifying unusual behavior or failures in systems.

2. Understanding Edge (IoT)

- Learn about edge computing and IoT, and how they enable real-time data processing and decision-making at the source.

3. What is ArgoCD?

- Discover ArgoCD, a declarative, GitOps continuous delivery tool for Kubernetes, and its role in deploying applications on edge devices.

4. Deployment Using ArgoCD for Edge Devices

- Step-by-step guide on deploying anomaly detection models on edge devices using ArgoCD.

5. Introduction to Apache Kafka and S3

- Explore Apache Kafka for real-time data streaming and Amazon S3 for scalable storage solutions.

6. Viewing Kafka Messages in the Data Lake

- Learn how to view and analyze Kafka messages stored in a data lake for better insights.

7. What is Prometheus?

- Get to know Prometheus, an open-source monitoring and alerting toolkit, and its application in monitoring edge devices.

8. Monitoring Application Metrics with Prometheus

- Detailed instructions on setting up Prometheus to monitor the performance and health of your anomaly detection system.

9. What is Camel K?

- Introduction to Camel K, a lightweight integration framework built on Apache Camel, designed for Kubernetes.

10. Configuring Camel K Integrations for Data Pipelines

- Learn how to configure Camel K for seamless data pipeline integrations in your anomaly detection workflow.

11. What is a Jupyter Notebook?

- Overview of Jupyter Notebooks, an open-source web application for creating and sharing documents with live code, equations, visualizations, and narrative text.

12. Jupyter Notebooks with Code Examples

- Hands-on examples and code snippets in Jupyter Notebooks to help you implement and test anomaly detection models.

Columbus Data & Analytics Wednesdays - June 2024

Columbus Data & Analytics Wednesdays, June 2024 with Maria Copot 20

Public CyberSecurity Awareness Presentation 2024.pptx

Cyber security awareness slides for a busisness by TreeTop Security

Dandelion Hashtable: beyond billion requests per second on a commodity server

This slide deck presents DLHT, a concurrent in-memory hashtable. Despite efforts to optimize hashtables, that go as far as sacrificing core functionality, state-of-the-art designs still incur multiple memory accesses per request and block request processing in three cases. First, most hashtables block while waiting for data to be retrieved from memory. Second, open-addressing designs, which represent the current state-of-the-art, either cannot free index slots on deletes or must block all requests to do so. Third, index resizes block every request until all objects are copied to the new index. Defying folklore wisdom, DLHT forgoes open-addressing and adopts a fully-featured and memory-aware closed-addressing design based on bounded cache-line-chaining. This design offers lock-free index operations and deletes that free slots instantly, (2) completes most requests with a single memory access, (3) utilizes software prefetching to hide memory latencies, and (4) employs a novel non-blocking and parallel resizing. In a commodity server and a memory-resident workload, DLHT surpasses 1.6B requests per second and provides 3.5x (12x) the throughput of the state-of-the-art closed-addressing (open-addressing) resizable hashtable on Gets (Deletes).

Introduction of Cybersecurity with OSS at Code Europe 2024

I develop the Ruby programming language, RubyGems, and Bundler, which are package managers for Ruby. Today, I will introduce how to enhance the security of your application using open-source software (OSS) examples from Ruby and RubyGems.

The first topic is CVE (Common Vulnerabilities and Exposures). I have published CVEs many times. But what exactly is a CVE? I'll provide a basic understanding of CVEs and explain how to detect and handle vulnerabilities in OSS.

Next, let's discuss package managers. Package managers play a critical role in the OSS ecosystem. I'll explain how to manage library dependencies in your application.

I'll share insights into how the Ruby and RubyGems core team works to keep our ecosystem safe. By the end of this talk, you'll have a better understanding of how to safeguard your code.

System Design Case Study: Building a Scalable E-Commerce Platform - Hiike

This case study explores designing a scalable e-commerce platform, covering key requirements, system components, and best practices.

Trusted Execution Environment for Decentralized Process Mining

Presentation of the paper "Trusted Execution Environment for Decentralized Process Mining" given during the CAiSE 2024 Conference in Cyprus on June 7, 2024.

SAP S/4 HANA sourcing and procurement to Public cloud

SAP S4 HANA to Public cloud data object differences

Your One-Stop Shop for Python Success: Top 10 US Python Development Providers

Simplify your search for a reliable Python development partner! This list presents the top 10 trusted US providers offering comprehensive Python development services, ensuring your project's success from conception to completion.

Skybuffer SAM4U tool for SAP license adoption

Manage and optimize your license adoption and consumption with SAM4U, an SAP free customer software asset management tool.

SAM4U, an SAP complimentary software asset management tool for customers, delivers a detailed and well-structured overview of license inventory and usage with a user-friendly interface. We offer a hosted, cost-effective, and performance-optimized SAM4U setup in the Skybuffer Cloud environment. You retain ownership of the system and data, while we manage the ABAP 7.58 infrastructure, ensuring fixed Total Cost of Ownership (TCO) and exceptional services through the SAP Fiori interface.

Generating privacy-protected synthetic data using Secludy and Milvus

During this demo, the founders of Secludy will demonstrate how their system utilizes Milvus to store and manipulate embeddings for generating privacy-protected synthetic data. Their approach not only maintains the confidentiality of the original data but also enhances the utility and scalability of LLMs under privacy constraints. Attendees, including machine learning engineers, data scientists, and data managers, will witness first-hand how Secludy's integration with Milvus empowers organizations to harness the power of LLMs securely and efficiently.

JavaLand 2024: Application Development Green Masterplan

My presentation slides I used at JavaLand 2024

Best 20 SEO Techniques To Improve Website Visibility In SERP

Boost your website's visibility with proven SEO techniques! Our latest blog dives into essential strategies to enhance your online presence, increase traffic, and rank higher on search engines. From keyword optimization to quality content creation, learn how to make your site stand out in the crowded digital landscape. Discover actionable tips and expert insights to elevate your SEO game.

zkStudyClub - LatticeFold: A Lattice-based Folding Scheme and its Application...

Folding is a recent technique for building efficient recursive SNARKs. Several elegant folding protocols have been proposed, such as Nova, Supernova, Hypernova, Protostar, and others. However, all of them rely on an additively homomorphic commitment scheme based on discrete log, and are therefore not post-quantum secure. In this work we present LatticeFold, the first lattice-based folding protocol based on the Module SIS problem. This folding protocol naturally leads to an efficient recursive lattice-based SNARK and an efficient PCD scheme. LatticeFold supports folding low-degree relations, such as R1CS, as well as high-degree relations, such as CCS. The key challenge is to construct a secure folding protocol that works with the Ajtai commitment scheme. The difficulty, is ensuring that extracted witnesses are low norm through many rounds of folding. We present a novel technique using the sumcheck protocol to ensure that extracted witnesses are always low norm no matter how many rounds of folding are used. Our evaluation of the final proof system suggests that it is as performant as Hypernova, while providing post-quantum security.

Paper Link: https://eprint.iacr.org/2024/257

FREE A4 Cyber Security Awareness Posters-Social Engineering part 3

Free A4 downloadable and printable Cyber Security, Social Engineering Safety and security Training Posters . Promote security awareness in the home or workplace. Lock them Out From training providers datahops.com

Energy Efficient Video Encoding for Cloud and Edge Computing Instances

Energy Efficient Video Encoding for Cloud and Edge Computing Instances

HCL Notes and Domino License Cost Reduction in the World of DLAU

Webinar Recording: https://www.panagenda.com/webinars/hcl-notes-and-domino-license-cost-reduction-in-the-world-of-dlau/

The introduction of DLAU and the CCB & CCX licensing model caused quite a stir in the HCL community. As a Notes and Domino customer, you may have faced challenges with unexpected user counts and license costs. You probably have questions on how this new licensing approach works and how to benefit from it. Most importantly, you likely have budget constraints and want to save money where possible. Don’t worry, we can help with all of this!

We’ll show you how to fix common misconfigurations that cause higher-than-expected user counts, and how to identify accounts which you can deactivate to save money. There are also frequent patterns that can cause unnecessary cost, like using a person document instead of a mail-in for shared mailboxes. We’ll provide examples and solutions for those as well. And naturally we’ll explain the new licensing model.

Join HCL Ambassador Marc Thomas in this webinar with a special guest appearance from Franz Walder. It will give you the tools and know-how to stay on top of what is going on with Domino licensing. You will be able lower your cost through an optimized configuration and keep it low going forward.

These topics will be covered

- Reducing license cost by finding and fixing misconfigurations and superfluous accounts

- How do CCB and CCX licenses really work?

- Understanding the DLAU tool and how to best utilize it

- Tips for common problem areas, like team mailboxes, functional/test users, etc

- Practical examples and best practices to implement right away

dbms calicut university B. sc Cs 4th sem.pdf

Its a seminar ppt on database management system using sql

Recently uploaded (20)

Skybuffer AI: Advanced Conversational and Generative AI Solution on SAP Busin...

Skybuffer AI: Advanced Conversational and Generative AI Solution on SAP Busin...

Monitoring and Managing Anomaly Detection on OpenShift.pdf

Monitoring and Managing Anomaly Detection on OpenShift.pdf

Public CyberSecurity Awareness Presentation 2024.pptx

Public CyberSecurity Awareness Presentation 2024.pptx

Dandelion Hashtable: beyond billion requests per second on a commodity server

Dandelion Hashtable: beyond billion requests per second on a commodity server

Introduction of Cybersecurity with OSS at Code Europe 2024

Introduction of Cybersecurity with OSS at Code Europe 2024

System Design Case Study: Building a Scalable E-Commerce Platform - Hiike

System Design Case Study: Building a Scalable E-Commerce Platform - Hiike

Trusted Execution Environment for Decentralized Process Mining

Trusted Execution Environment for Decentralized Process Mining

SAP S/4 HANA sourcing and procurement to Public cloud

SAP S/4 HANA sourcing and procurement to Public cloud

Your One-Stop Shop for Python Success: Top 10 US Python Development Providers

Your One-Stop Shop for Python Success: Top 10 US Python Development Providers

Generating privacy-protected synthetic data using Secludy and Milvus

Generating privacy-protected synthetic data using Secludy and Milvus

JavaLand 2024: Application Development Green Masterplan

JavaLand 2024: Application Development Green Masterplan

Best 20 SEO Techniques To Improve Website Visibility In SERP

Best 20 SEO Techniques To Improve Website Visibility In SERP

zkStudyClub - LatticeFold: A Lattice-based Folding Scheme and its Application...

zkStudyClub - LatticeFold: A Lattice-based Folding Scheme and its Application...

FREE A4 Cyber Security Awareness Posters-Social Engineering part 3

FREE A4 Cyber Security Awareness Posters-Social Engineering part 3

Overcoming the PLG Trap: Lessons from Canva's Head of Sales & Head of EMEA Da...

Overcoming the PLG Trap: Lessons from Canva's Head of Sales & Head of EMEA Da...

Energy Efficient Video Encoding for Cloud and Edge Computing Instances

Energy Efficient Video Encoding for Cloud and Edge Computing Instances

HCL Notes and Domino License Cost Reduction in the World of DLAU

HCL Notes and Domino License Cost Reduction in the World of DLAU

Convert Altera Xilinx FPGA to BaySand mcFPGA

- 1. BaySand, Inc. - MCSC FPGA Convert Xilinx/Altera in less than 10 weeks EBBM, Inc. App Note # BAY26170001 mcFPGA - Simplifying FPGA Conversions BaySand simplifying FPGA conversions Call Toll-free +1 (833) EBBMinc

- 2. simplifying FPGA conversions - Call Toll-free +1 (833) EBBMinc SoC Design Reuse Platform mcCAP FPGA ASIC Platform Solution mcASIC mcFPGA Multi Project Wafer (MPW) mcASIC Ultra Shuttle Licensing RISCV Technology IP Hard and Soft Cores SecureRF Ironwood™ SecureRF WalnutDSA™ CUSTOM LOGIC PLATFORM BaySand technology at work for youCONNECTING YOUR DESIGN TO THE TECHNOLOGY RESOURCES YOU NEED BaySand’s ultimate comprehensive multi-process node custom logic technology has the fastest time-to-market (TTM) and optimized unit cost (ASP) compared to any other existing solution! The MCSC (Metal Configurable Standard Cell) is patented, innovative disruptive 4 metal layer only configurable mcASIC, mcFPGA, mcCAP (SOC), and Field Configurable fcDSP products supporting designs from 14nm to 65nm. The mcFPGA is a drop-in replacement for Xilinx / Altera devices and provides up-to 10X power reduction, 5X performance improvement, and up-to 10X unit price (ASP) reduction. One major distinction is the ability to deliver Packaged & Tested (DFT, ATPG and BIST ) devices 7-10 weeks from RTL with no EDA license or proprietary tools required. Flexible solutions for your design needs BAYSANDs COMPREHENSIVE END TO END SOLUTION MCSC CUSTOM LOGIC PLATFORM BaySand has the options to articulate and realize your custom logic. Our family of metal configurable technologies, cell libraries, I/Os, memory, PLLs, PHYs, and trans- ceivers serve as the platform for a complete metal configurable product design. Fast quantum-resistant authentication and data protection solutions for low- resource IoT devices, high performance computing, and data farms with up to 60 times efficiency over ECC and up to 140 times less energy. The MCSC platform will protect your design even when quantum computers become available and render currently-used methods obsolete. MCSC Platform Benefits • Use your existing IDE tools • Clock Tree per design need • IO support for 1.6Gbps LVDS/DDR3 • Streamlined Test Program Development • NO TOOLING - Use existing package • USE EXISTING test board AND probe-card • Lowest Project Lifecycle Cost - Low NRE - Low unit cost

- 3. POWER BENCHMARK Lowest Power Consumption. Power is becoming the primary concern for most FPGA designs. Beyond meeting thermal constraints, lowering power improves system cost and reliability, and supports increased performance. By leveraging power advantage of MCSC Technology (inherent ASIC like power advantage), mcFPGA can achieve up to 10X power reduction compared to FPGAs by lowering both static and dynamic power consump- tion. FREQUENCY BENCHMARK Breaking through 28nm Xilinx/Altera FPGA Performance Limits. Building on the MCSC logic architecture and tech- nology, mcFPGA families enable much higher performance compared to FPGAs which may even be one or two process technology nodes ahead. Based on many FPGA design to ASIC migration examples, we can consist- ently achieve easy migration in terms of performance to mcF65L (65nm) or mcF40L (40nm) devices from 28nm FPGA devices. BAYSAND’s IP WIZARD on the WEB BaySand provides Xpresso, which mim- ics the functionality of IP wizards com- monly found in FPGA SW, to facilitate the designers ability to generate the desired IP function for the application and customization. The user interface is intuitive and similar to FPGA IP wiz- ards for various IPs and generates all files needed for implementation and verification. simplifying FPGA conversions - Call Toll-free +1 (833) EBBMinc

- 4. Dr. Salah M. Werfelli has over 30 years of experience in system and integrated circuit (IC) design, and Executive Management and leadership. Before Co-Founding BaySand he was an Executive Vice President for eASIC. Prior, he worked with Cadence Design Systems where he held various executive positions including corporate Vice President of Technology, responsible for M&A and business development worldwide. While serving with Cadence, he was the chief architect for the EDA industry’s first major outsourcing project with Unisys Corp. Ehud Yuhjtman has over 30 years of experience in the communication and chip market. Before joining BaySand, Inc. asExecutive Vice President, and Co-Founder, Mr. Yuhjtman served as CEO of FalconX Accelerator where he developed Low Power Digital Signal Processing IP with unique flexibility and “on the fly” configuration targeting image processing, mobile devices & stations, consumer, automotive, industrial and IoT markets. Jonathan Park has over 25 years of experience in engineering and executive management. As BaySand’s CTO, and Co-Founder, he has served to develop and to bring innovative and disruptive Metal Configurable Standard Cell (MCSC) technology to product realization. Prior to co-founding BaySand, he served as Vice President of Engineering at eASIC. Earlier in his career, he has developed and launched two subsequent generations of Altera’s “HardCopy” products. Mr. Park has 10 patents in the fields of metal programmable devices and methodology. Asher Hazanchuk has over 30 years of experience in product planning & engineering management. Before joining BaySand, Inc. as Executive Vice President, CTO DSP Engineering, and Co-Founder, Mr. Hazanchuk served as DSP solutions system architect at Lattice Semiconductor, where he received the 2011 Innovator of the Year Award and managed the DSP IP cores group at Altera. Mr. Hazanchuk developed more than 15 patents. Moazzem Hossain has over 20 years of experience in ASIC and EDA industries. Before joining BaySand, Inc. as Executive Vice President of Design Solutions, Mr. Hossain co-founded Fastrack Design, an ASIC design solutions and services company. Mr. Hossain has 4 patents and over 40 tech- nical publications in the areas of electronic design and design automation. BaySand, Inc. - Management Team BRIDGING the CUSTOM LOGIC GAP mcFPGA ==> mcASIC ==> mcSOC EBBM, Inc. AMERICA, GREECE, CANADA Sales / Field Application Engineers Call Toll-free +1 (833) EBBMinc for detailed BaySand Info and samples http://ebbm.net fae@ebbm.net ΜΙΛΆΜΕ ΕΛΛΗΝΙΚΆ, NOUS PARLONS FRANCAIS, FALAMOS PORTUGUES simplifying FPGA conversions © 2017 EBBM, Inc. EBBM, and the EBBM logo are trademarks of EBBM, Inc in the U.S. and/or other countries. BAYSAND, MCSC, XPRESSO, mcASIC, mcFPGA, mcCAP , fcDSP and the BAYSAND logo are trademarks of BAYSAND, Inc in the U.S. and/or other countries. Altera, Stratix, Cyclone, and Arria are trademarks of Intel Corp in the U.S. and/or other countries. Xilinx, Artix, Spartan, and Virtex are trademarks of Xilinx, Corp in the U.S. and/or other countries. SecureRF, Ironwood™ and WalnutDSA™ are trademarks of SecureRF Corp in the U.S. and/or other countries. * Benchmark data may vary in individual applications. * TTM - time to market for FPGA to ASIC statement of less than 10 week sample delivery is based from the date of receipt of customer RTL and approval by BaySand.