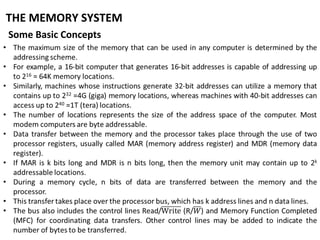

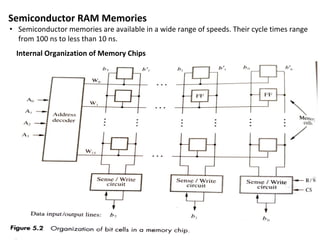

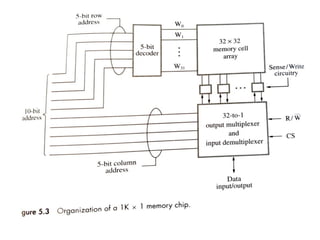

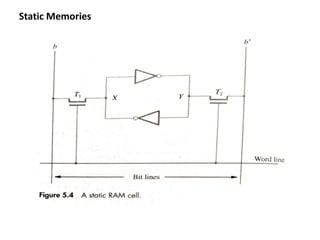

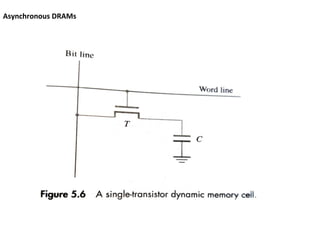

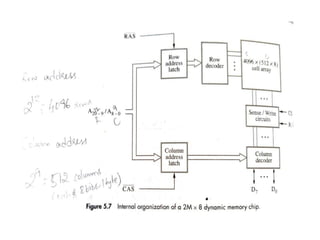

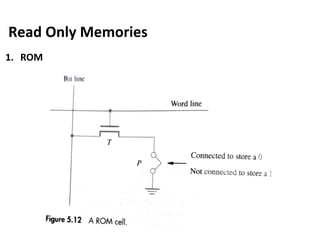

The document covers key concepts related to the memory system, including memory access time, memory cycle time, and different types of memory such as RAM, SRAM, and DRAM. It explains the internal organization of memory chips, read/write operations, and various types of read-only memories (ROMs) and their programmable variants. Additionally, it discusses newer technologies like EEPROM and flash memory, emphasizing their applications in portable devices and advantages over traditional memory types.