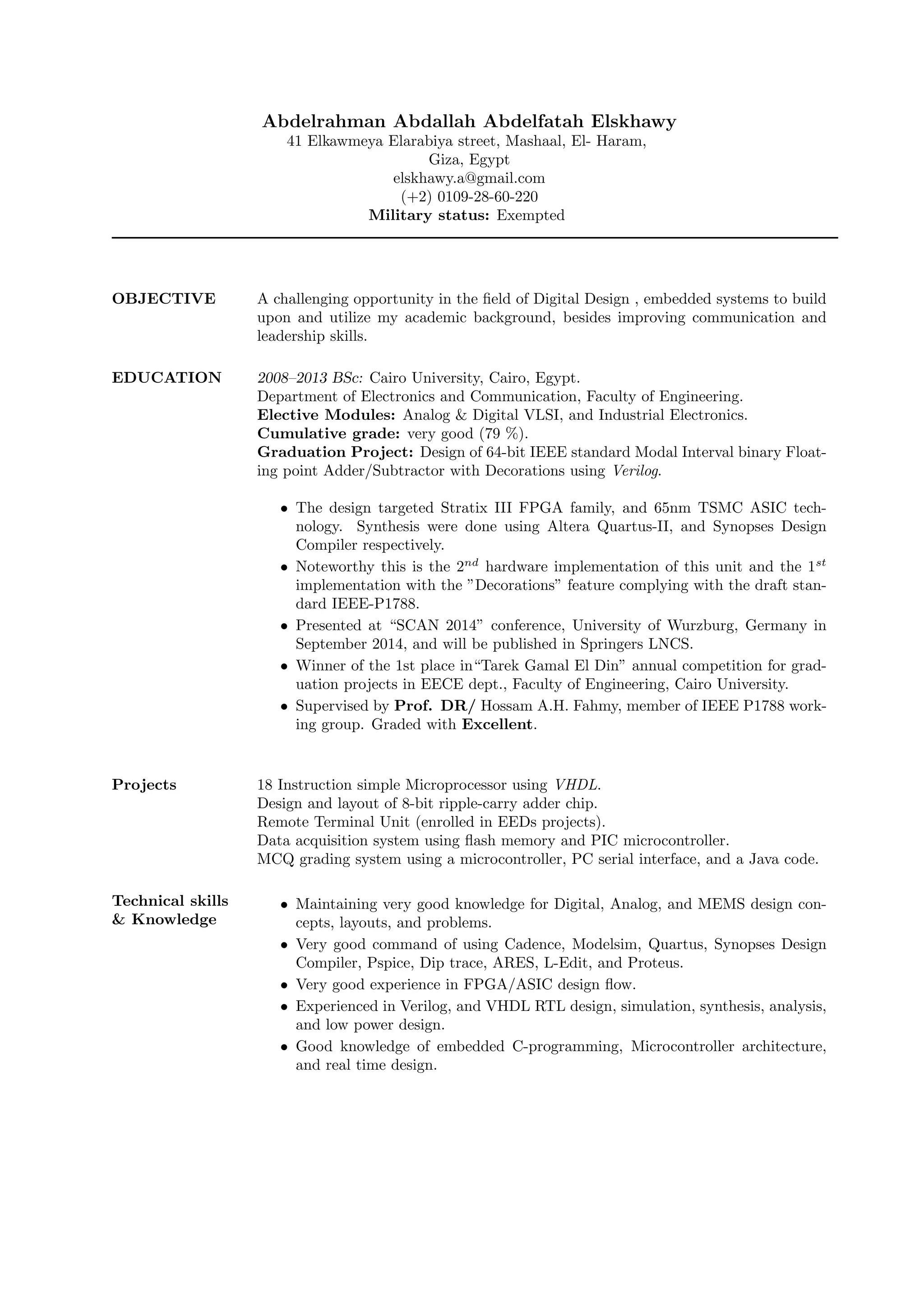

Abdelrahman Abdallah Abdelfatah Elskhawy is seeking a challenging opportunity in digital design and embedded systems. He has a BSc in electronics and communication from Cairo University, graduating with very good grades. His graduation project involved designing a 64-bit floating point adder/subtractor using Verilog. He has experience as an embedded systems developer and has skills in Verilog, VHDL, C programming, and CAD tools like Cadence and Quartus. In his free time he enjoys martial arts, chess, and reading.