Shift Register Applications for Serial to Parallel Conversion

•

0 likes•291 views

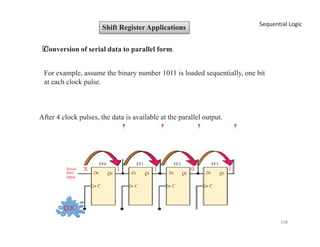

Shift registers can be used for converting serial data to parallel form and for delaying digital signals. An 8-bit serial-in serial-out shift register with a 40 MHz clock can delay a signal by 200 ns as the delay for each clock cycle is 25 ns and there are 8 cycles. Shift-register counters include ring counters where the output of the last flip-flop is fed to the input of the first flip-flop, and Johnson counters where the inverted output of the last flip-flop is connected to the first flip-flop, allowing them to require fewer flip-flops than ring counters for a given count.

Report

Share

Report

Share

Download to read offline

More Related Content

What's hot

What's hot (20)

Similar to Shift Register Applications for Serial to Parallel Conversion

Lec15 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Re...

Lec15 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Re...Hsien-Hsin Sean Lee, Ph.D.

Similar to Shift Register Applications for Serial to Parallel Conversion (20)

MEASUREMENT AND DISPLAY OF THE MAINS FREQUENCY USING PIC18F4520/50

MEASUREMENT AND DISPLAY OF THE MAINS FREQUENCY USING PIC18F4520/50

FREQUENCY COUNTERS AND TIME-INTERVAL MEASUREMENTS.pdf

FREQUENCY COUNTERS AND TIME-INTERVAL MEASUREMENTS.pdf

Lec15 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Re...

Lec15 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Re...

Recently uploaded

Bur Dubai Call Girls # 971504361175 # Call Girls In Bur Dubai || (UAE)

Bur Dubai Call Girls # 971504361175 # Call Girls In Bur Dubai || (UAE)Business Bay Call Girls || 0529877582 || Call Girls Service in Business Bay Dubai

Dxb Call Girls # +971529501107 # Call Girls In Dxb Dubai || (UAE)

Dxb Call Girls # +971529501107 # Call Girls In Dxb Dubai || (UAE)Business Bay Call Girls || 0529877582 || Call Girls Service in Business Bay Dubai

(NEHA) Call Girls Ahmedabad Booking Open 8617697112 Ahmedabad Escorts

(NEHA) Call Girls Ahmedabad Booking Open 8617697112 Ahmedabad EscortsCall girls in Ahmedabad High profile

Recently uploaded (20)

FULL ENJOY - 9953040155 Call Girls in Noida | Delhi

FULL ENJOY - 9953040155 Call Girls in Noida | Delhi

Bur Dubai Call Girls # 971504361175 # Call Girls In Bur Dubai || (UAE)

Bur Dubai Call Girls # 971504361175 # Call Girls In Bur Dubai || (UAE)

FULL ENJOY - 9953040155 Call Girls in Uttam Nagar | Delhi

FULL ENJOY - 9953040155 Call Girls in Uttam Nagar | Delhi

FULL ENJOY - 9953040155 Call Girls in Mahipalpur | Delhi

FULL ENJOY - 9953040155 Call Girls in Mahipalpur | Delhi

Call Girl in Bur Dubai O5286O4116 Indian Call Girls in Bur Dubai By VIP Bur D...

Call Girl in Bur Dubai O5286O4116 Indian Call Girls in Bur Dubai By VIP Bur D...

Dxb Call Girls # +971529501107 # Call Girls In Dxb Dubai || (UAE)

Dxb Call Girls # +971529501107 # Call Girls In Dxb Dubai || (UAE)

FULL ENJOY - 9953040155 Call Girls in Moti Nagar | Delhi

FULL ENJOY - 9953040155 Call Girls in Moti Nagar | Delhi

Call Girl Service In Dubai #$# O56521286O #$# Dubai Call Girls

Call Girl Service In Dubai #$# O56521286O #$# Dubai Call Girls

(NEHA) Call Girls Ahmedabad Booking Open 8617697112 Ahmedabad Escorts

(NEHA) Call Girls Ahmedabad Booking Open 8617697112 Ahmedabad Escorts

FULL ENJOY - 9953040155 Call Girls in Burari | Delhi

FULL ENJOY - 9953040155 Call Girls in Burari | Delhi

Downtown Call Girls O5O91O128O Pakistani Call Girls in Downtown

Downtown Call Girls O5O91O128O Pakistani Call Girls in Downtown

Gomti Nagar & High Profile Call Girls in Lucknow (Adult Only) 8923113531 Esc...

Gomti Nagar & High Profile Call Girls in Lucknow (Adult Only) 8923113531 Esc...

Charbagh / best call girls in Lucknow - Book 🥤 8923113531 🪗 Call Girls Availa...

Charbagh / best call girls in Lucknow - Book 🥤 8923113531 🪗 Call Girls Availa...

FULL ENJOY - 9953040155 Call Girls in Shaheen Bagh | Delhi

FULL ENJOY - 9953040155 Call Girls in Shaheen Bagh | Delhi

Hazratganj / Call Girl in Lucknow - Phone 🫗 8923113531 ☛ Escorts Service at 6...

Hazratganj / Call Girl in Lucknow - Phone 🫗 8923113531 ☛ Escorts Service at 6...

FULL ENJOY - 9953040155 Call Girls in Indirapuram | Delhi

FULL ENJOY - 9953040155 Call Girls in Indirapuram | Delhi

Shift Register Applications for Serial to Parallel Conversion

- 1. Shift Register Applications ‰Conversion of serial data to parallel form. Sequential Logic For example, assume the binary number 1011 is loaded sequentially, one bit at each clock pulse. After 4 clock pulses, the data is available at the parallel output. FF0 FF1 FF2 FF3 Serial X 1 1 0 1data D0 Q0 D1 Q1 D2 Q2 D3 Q3 input C C C C CLK 108

- 2. Shift Register Applications ‰Delay a digital signal Shift registers can be used to delay a digital signal by a predetermined amount. EXAMPLE: Sequential Logic An 8-bit serial in/serial out shift register has a 40 MHz clock. What is the total delay through the register? The delay for each clock is 1/40 MHz = 25 ns The total delay is 8 x 25 ns = 200 ns Data in CLK 40 MHz CLK Data in A SRG 8 Q7 B Q7 C Data out Data out td 109

- 3. SHIFT-REGISTER COUNTERS Sequential Logic Two types: ring counter and the Johnson (or shift) counter. ‰Ring Counter The simplest shift-register counter is essentially a circulating shift register connected so that the last FF shifts its value into the first FF. It is used to control the sequencing of operations in a system. (NOTE: The register need to be initialized to 1000) In general, a ring counter requires more FFs than a binary counter for the same MOD number (MOD-N requires N flip-flops) 110

- 4. Sequential Logic SHIFT-REGISTER COUNTERS ‰Johnson Counter like a normal ring counter except that the inverted output of the last FF is connected to the input of the first FF. For a given MOD number, a Johnson counter requires only half the number of FFs that a ring counter requires, but generally more than a binary counter. MOD-6 Johnson counter 111