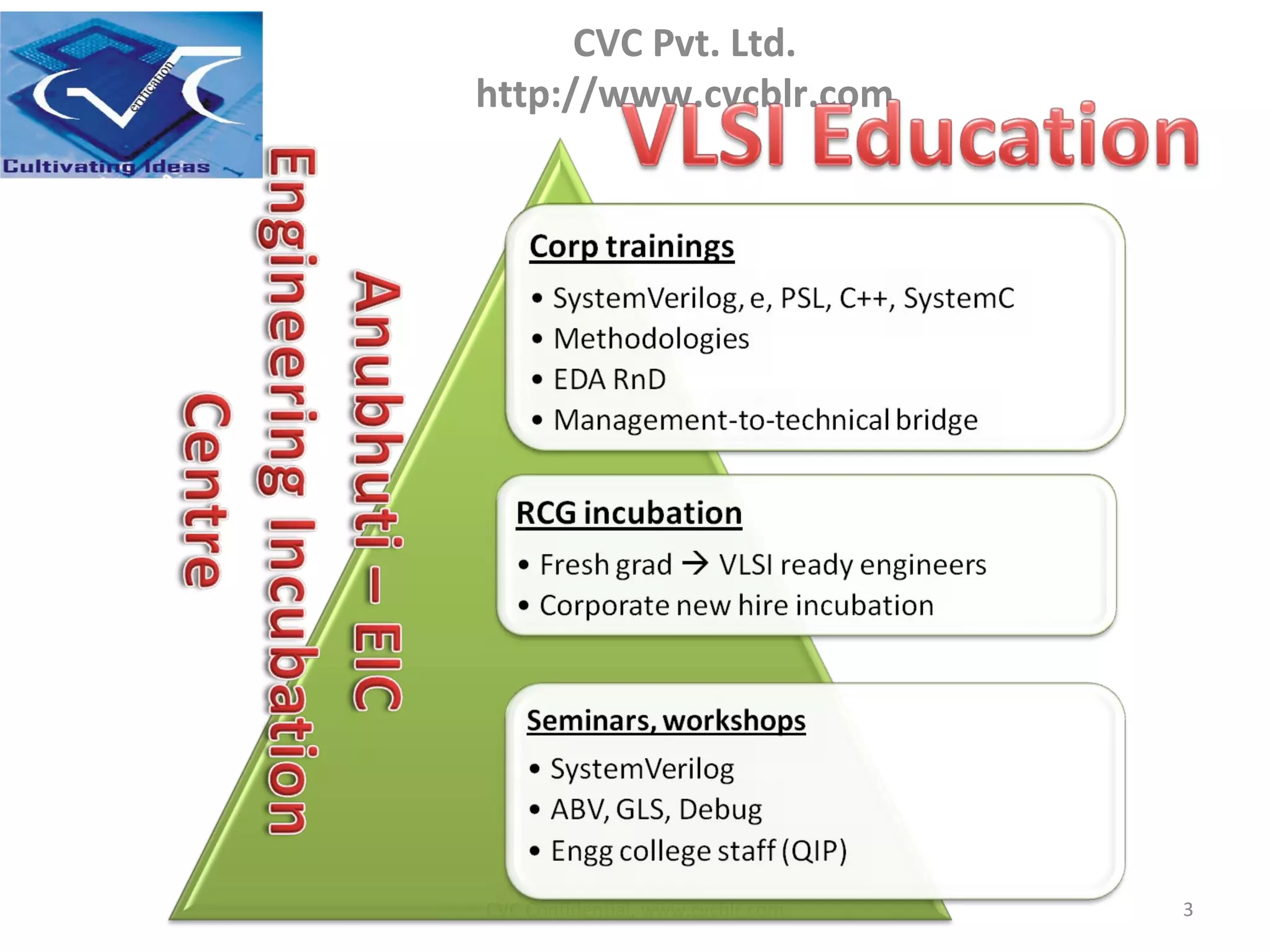

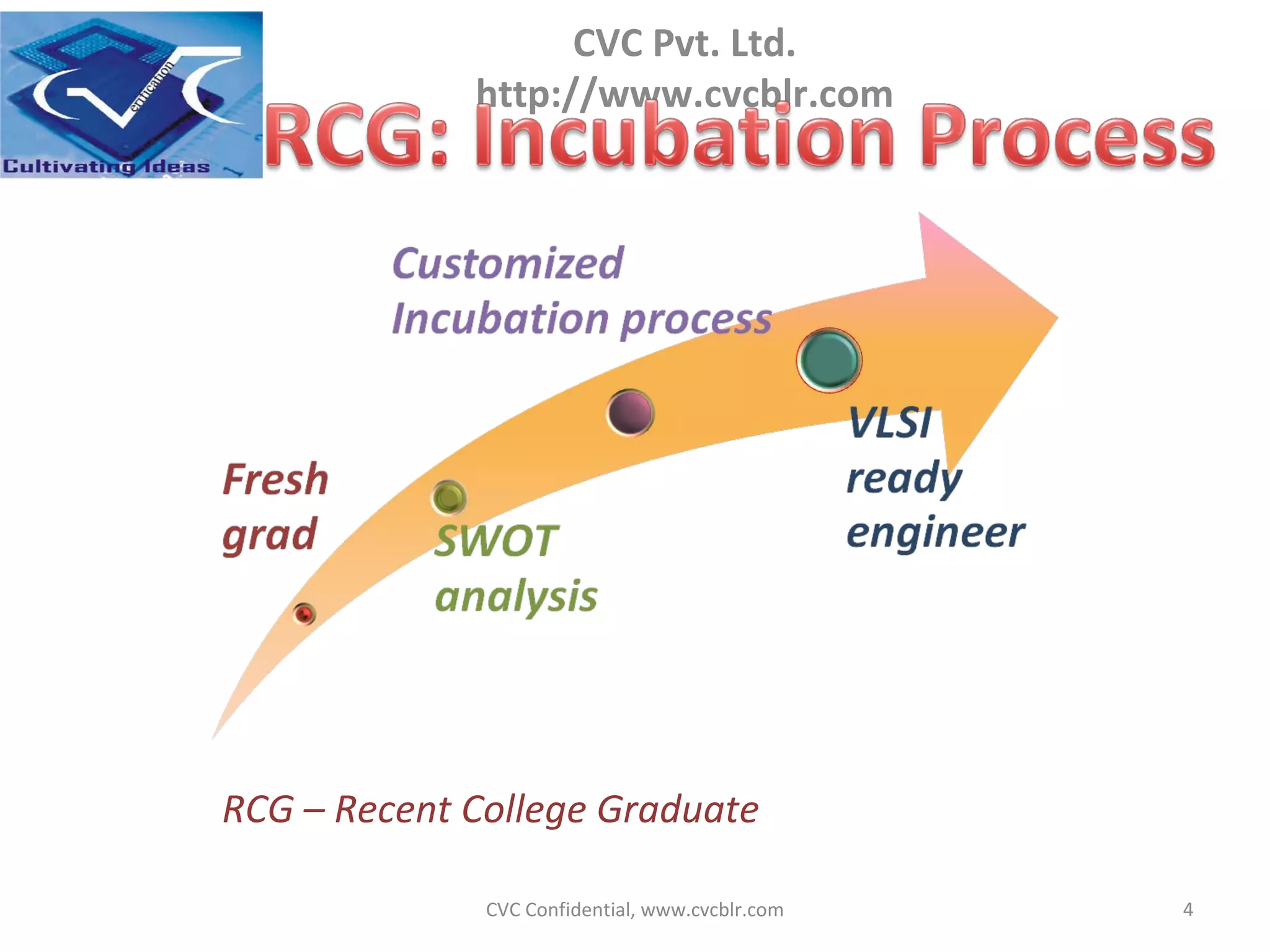

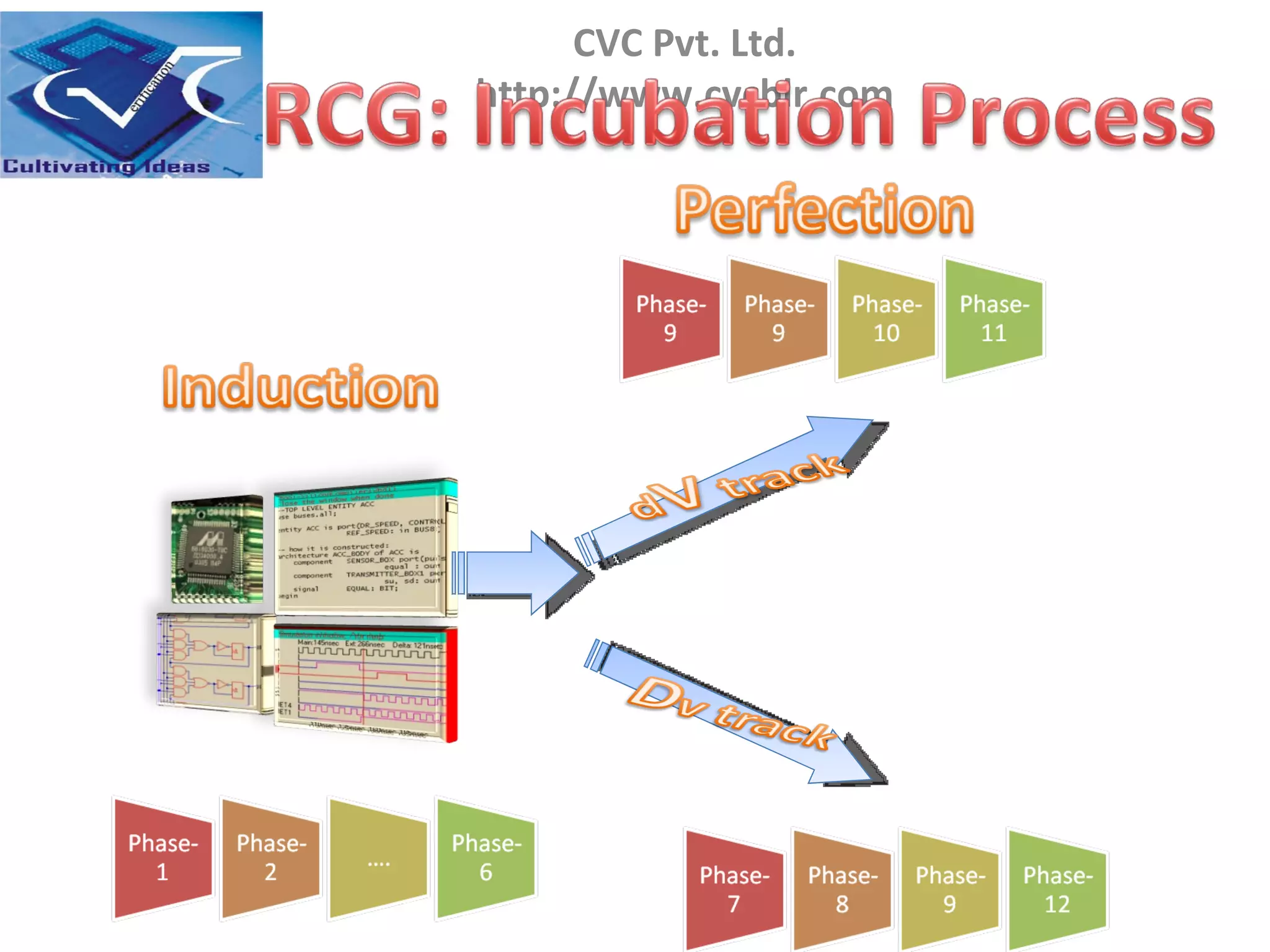

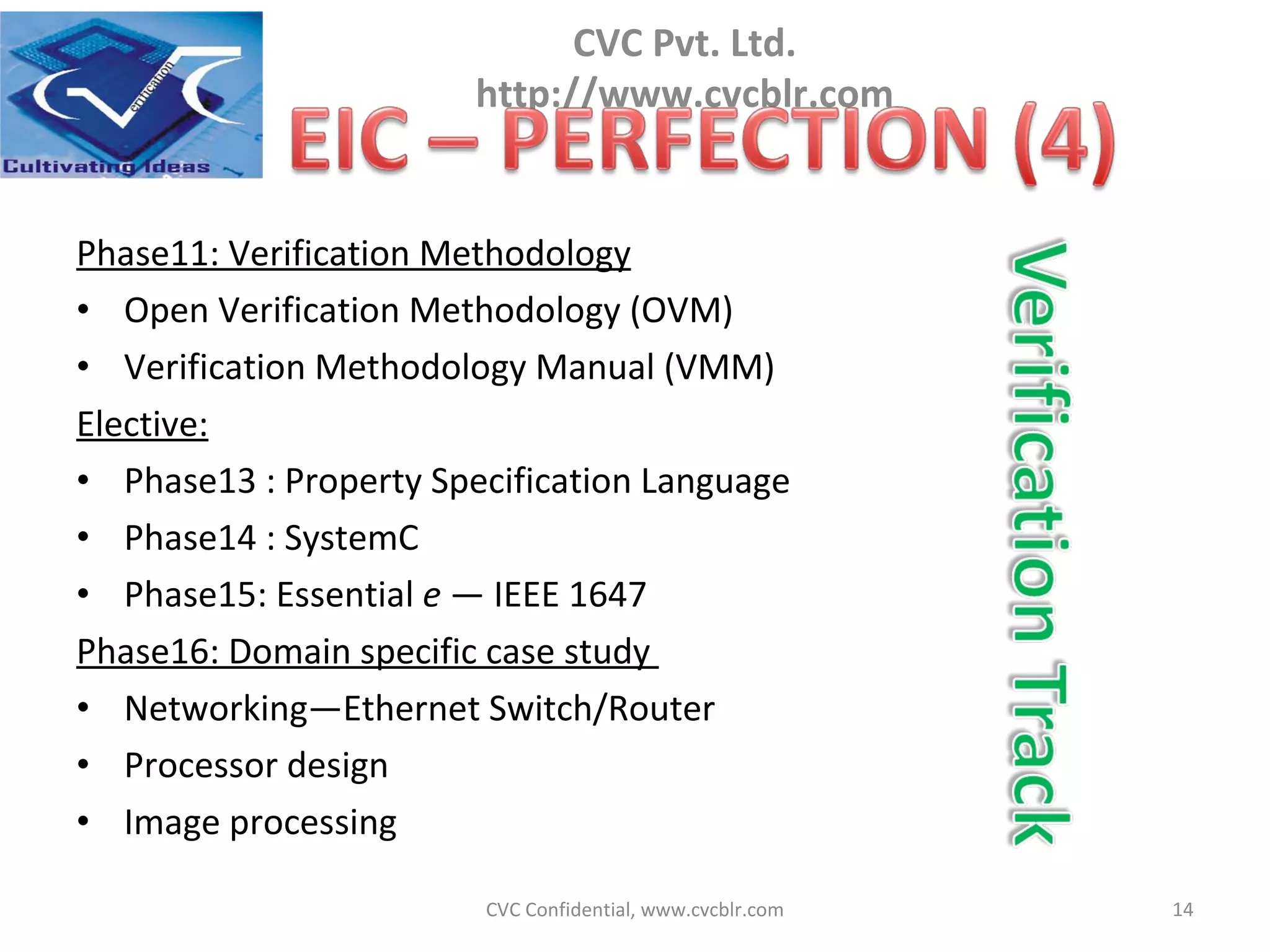

The document describes an Engineering Incubation Centre (EIC) program for recent college graduates. The 16-week program helps graduates transition to become productive VLSI design and verification professionals. It covers topics like digital design, HDLs, verification, and SystemVerilog through phases of induction, building basics, RTL design, verification methodology, and domain-specific case studies. The goal is to assess skills, provide tailored training, and guide graduates to dream jobs in the field.