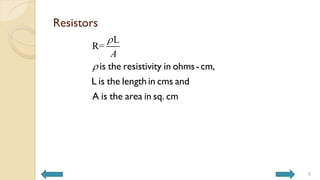

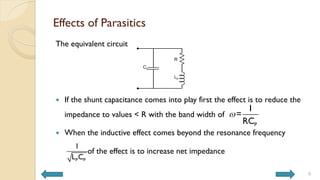

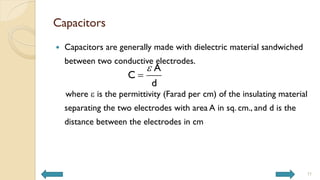

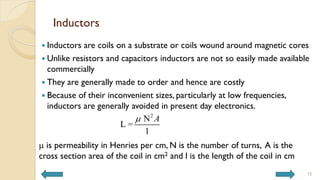

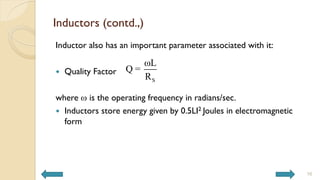

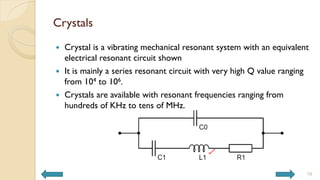

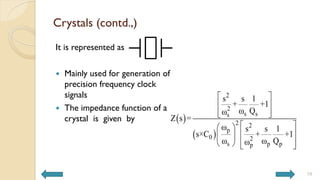

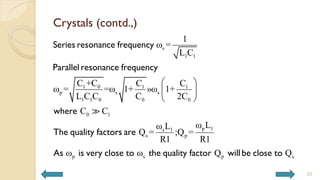

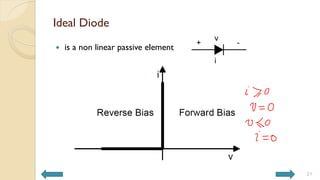

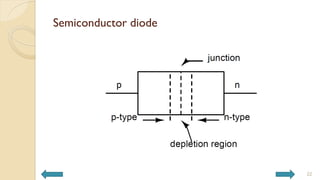

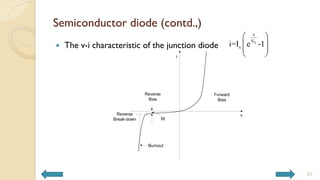

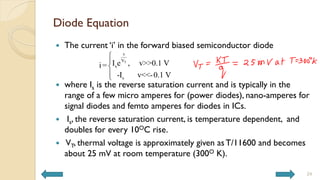

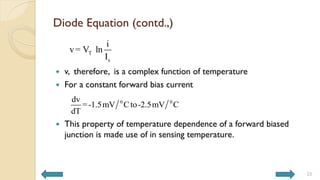

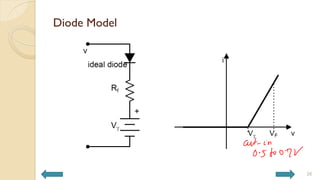

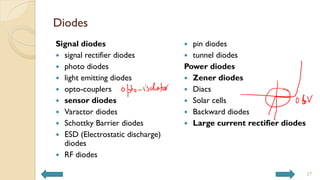

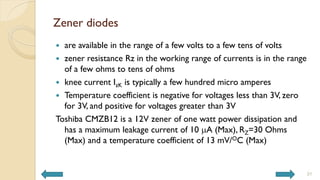

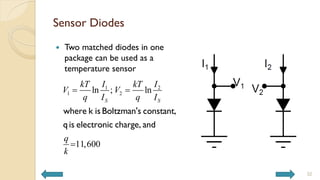

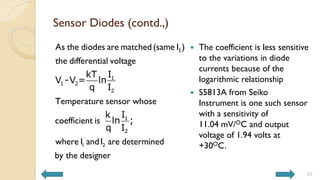

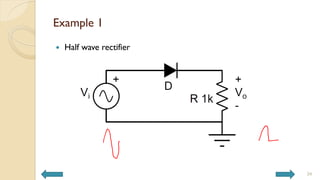

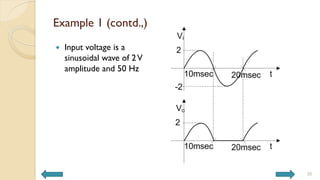

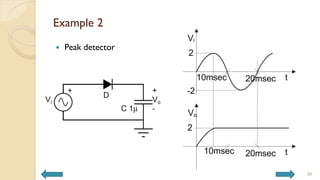

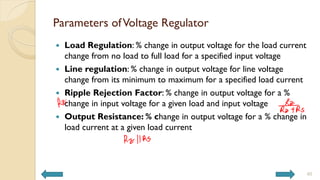

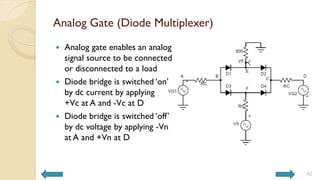

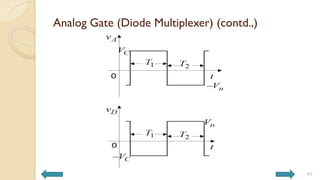

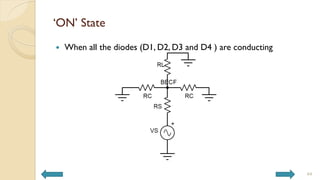

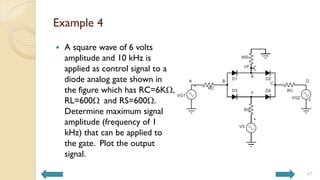

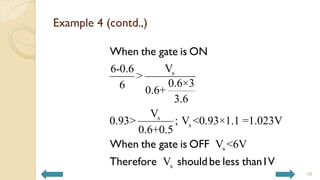

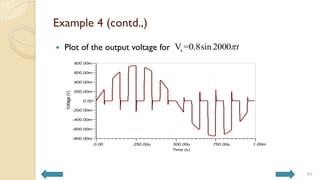

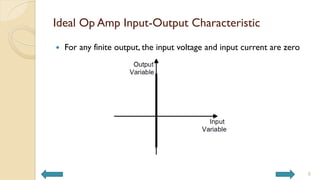

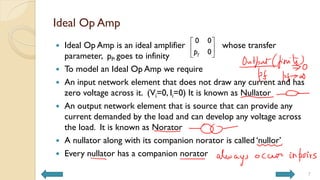

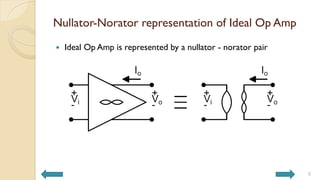

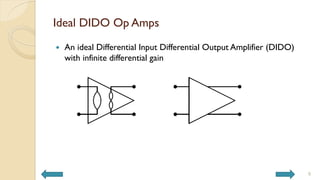

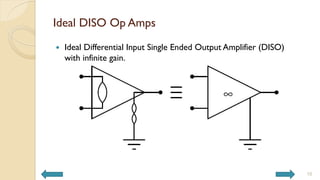

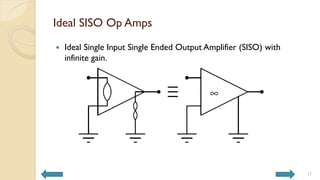

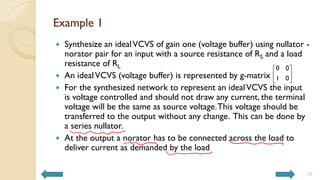

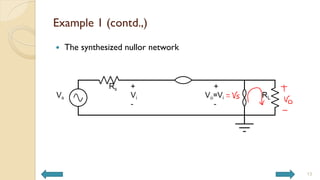

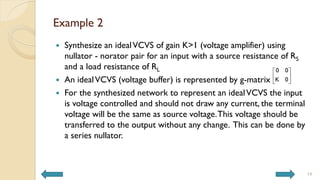

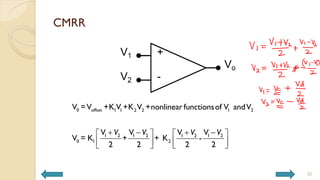

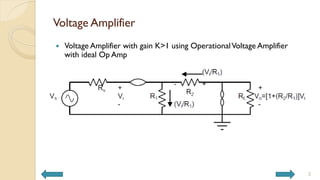

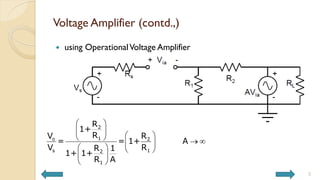

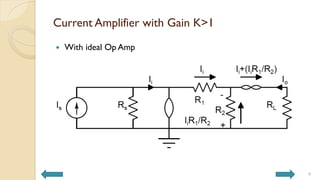

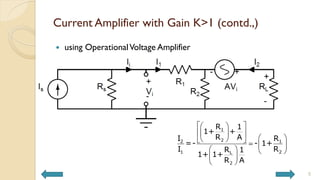

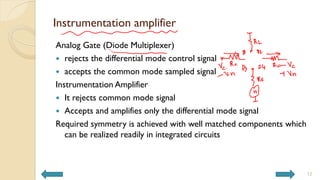

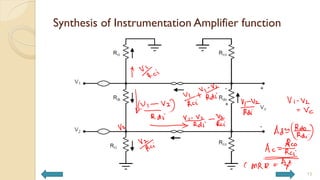

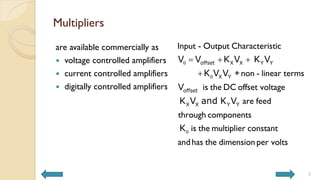

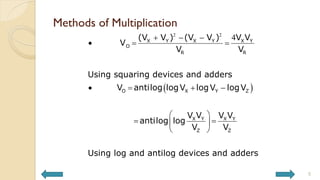

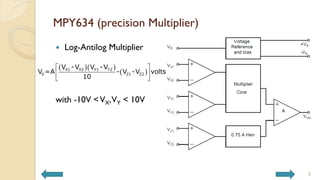

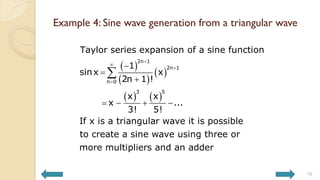

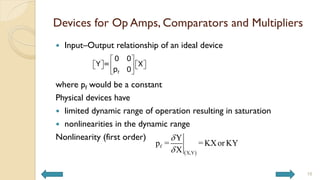

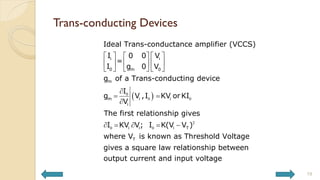

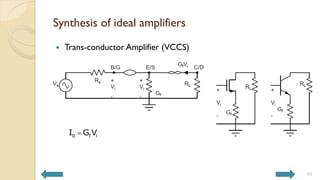

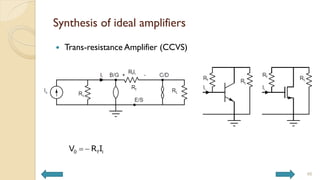

This document covers analog circuits and systems, focusing on passive and active electronic devices essential for analog signal processing. It details the characteristics and applications of resistors, capacitors, inductors, and diodes, as well as their parasitic effects and importance in circuit design. Additionally, it introduces operational amplifiers and their ideal models for mathematical functions in signal processing.