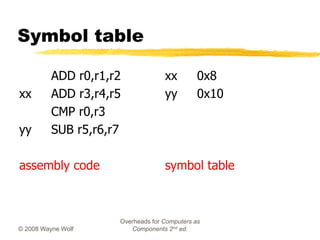

This document discusses different representations of computer programs, including source code, assembly code, and intermediate representations used by compilers. It describes state machines as a way to model program behavior and control flow. Specific program representations covered include data flow graphs, control-flow graphs, and single assignment form. The document also discusses the assembly and linking processes, how symbols are resolved, and relative versus absolute addressing.