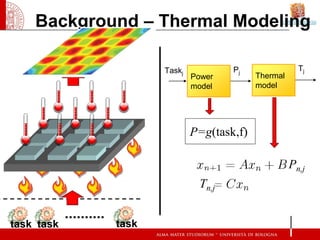

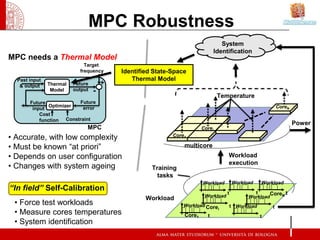

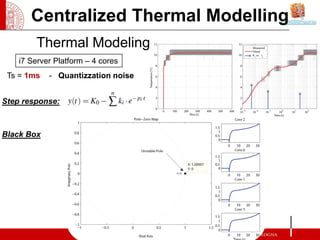

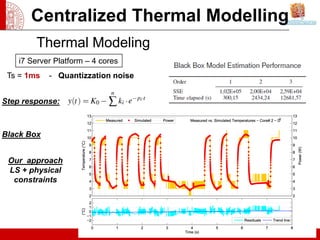

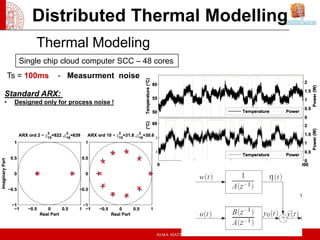

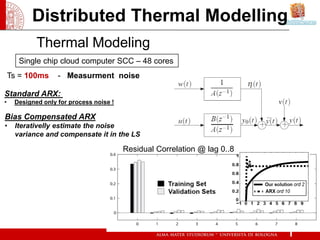

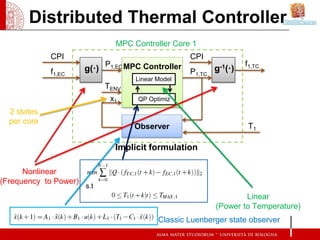

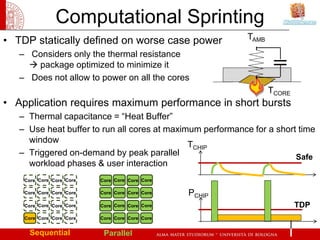

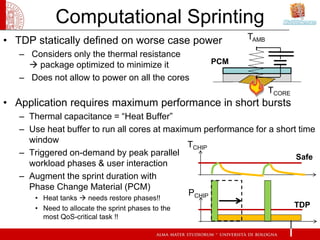

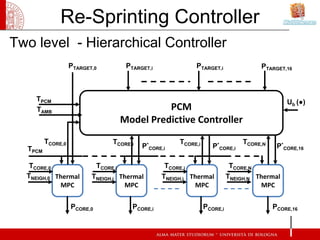

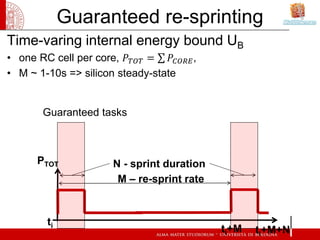

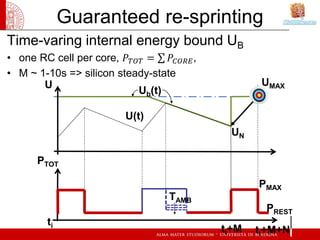

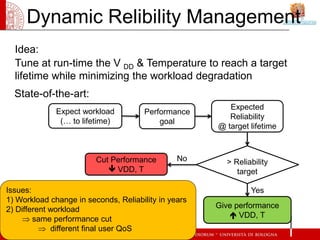

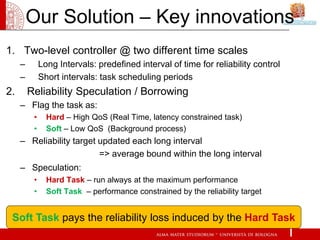

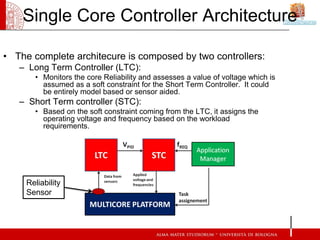

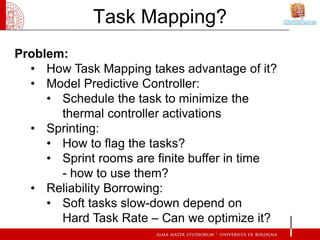

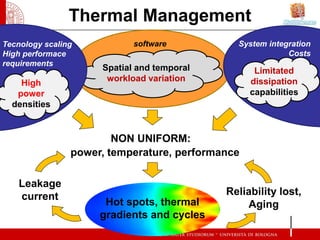

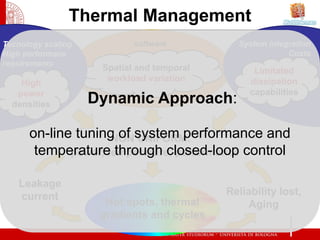

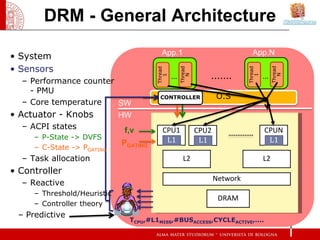

The document discusses advanced thermal management techniques, including thermal model learning and model predictive control to optimize performance in high-density computing environments. It outlines strategies for dynamic reliability management and computational sprinting to enhance processing capabilities while addressing thermal constraints and power dissipation. Additionally, it highlights the use of hierarchical controllers for balancing performance and reliability across workloads.

![Thermal Controller

Model Predictive

Controller

•Internal prediction:

avoid overshoot

•Optimization:

[Intel®, ISSCC 2007]

maximizes performance

Target

frequency

Classical feed-back Past input

& output Thermal Future +

controller Model output -

Future Future

• PID controllers input

Optimizer error

Threshold based • Better than threshold Cost

function Constraint

controller based approach MPC

• Centralized

• Cannot prevent overshoot

•T > Tmax low freq • aware of neighbor

•T < Tmin high freq cores thermal

• cannot prevent overshoot influence

• thermal cycle • All at once – MIMO

controller

• Complexity !!!](https://image.slidesharecdn.com/thermalcontrolkth-130109111608-phpapp02/85/Thermal-Control-Overview-6-320.jpg)