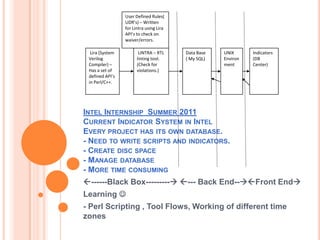

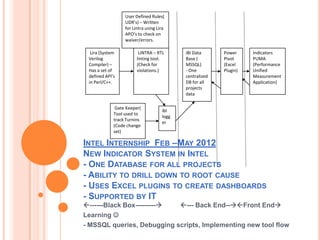

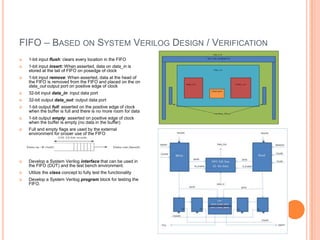

Rishi Sharma worked as an intern at Intel in 2011 and 2012 where he helped develop new indicator systems to track projects using a centralized database and dashboards. He also worked on virtualizing servers and syncing workstations. As a research assistant, he analyzed smart grid and power industry data. Previous jobs included work as a developer in India. Projects involved designing FIFO buffers in SystemVerilog, developing a PCI master/target handshake, and designing a parallel pipelined matrix multiplier.

![PARALLEL PIPELINED MATRIX MULTIPLIER

A and B are pre-stored in memory. Elements of A, B, and P are 32-bit integers. P should be

stored in memory. You can have up to four 32-bit wide memory banks.

Address port for a memory bank is 32-bit..

Memory bank gets proper control and address signals, it needs 8 cycles to retrieve or write 32

bits. The address phase takes one cycle.

Arithmetic unit can only operate on register-type data.

The results of the ALU cannot directly be written into the memory block.

The multiplication of two matrices A and B will begin when an input signal called START is

asserted.

PMM will assert and output signal called “DONE” when multiplication is done.

Develop a test bench for validating the data path.

Synthesize PMM and analyze the synthesized circuit using Synopsis Design Compiler tool.

VCS - Verilog Simulator – simulate / Code Coverage.

VCS – Design Complier – Synthesis Tool.

VCS – Design vision – Interface to communicate with the DC.

1.ADDRESS_STORE_A

2. ADDRESS_STORE_B_EVEN ,ADDRESS_STORE_B_ODD

3. DATA_MATRIX_A - A[7:0],A[15:8],A[23:16],A[31:24]

4. DATA _MATRIX_B - B_EVEN,B_ODD

5. DATA_MUL_A 6. DATA_MUL_B 7. MUL_OUTPUT 8. ADD_OUTPUT

9. EXEC_MEM_P_EVEN 10. EXEC_MEM_P_ODD 11. EXEC_MEM_P_EVEN

12. EXEC_MEM_P_ODD 13.MEM_WB_P_EVEN 14. MEM_WB_P_ODD

15. REG_OUTPUT 16.TEMP_REGISTER_EVEN TEMP_REGISTER_ODD

17. TEMP_REGISTER_EVEN [31:0] TEMP_REGISTER_EVEN [63:32]

TEMP_REGISTER_ODD[31:0] TEMP_REGISTER_ODD [63:32]

18. DATA_MATRIX_P](https://image.slidesharecdn.com/rishikeshsharmaportfolio-13476442492173-phpapp01-120914123840-phpapp01/85/Rishikesh-Sharma-Portfolio-10-320.jpg)