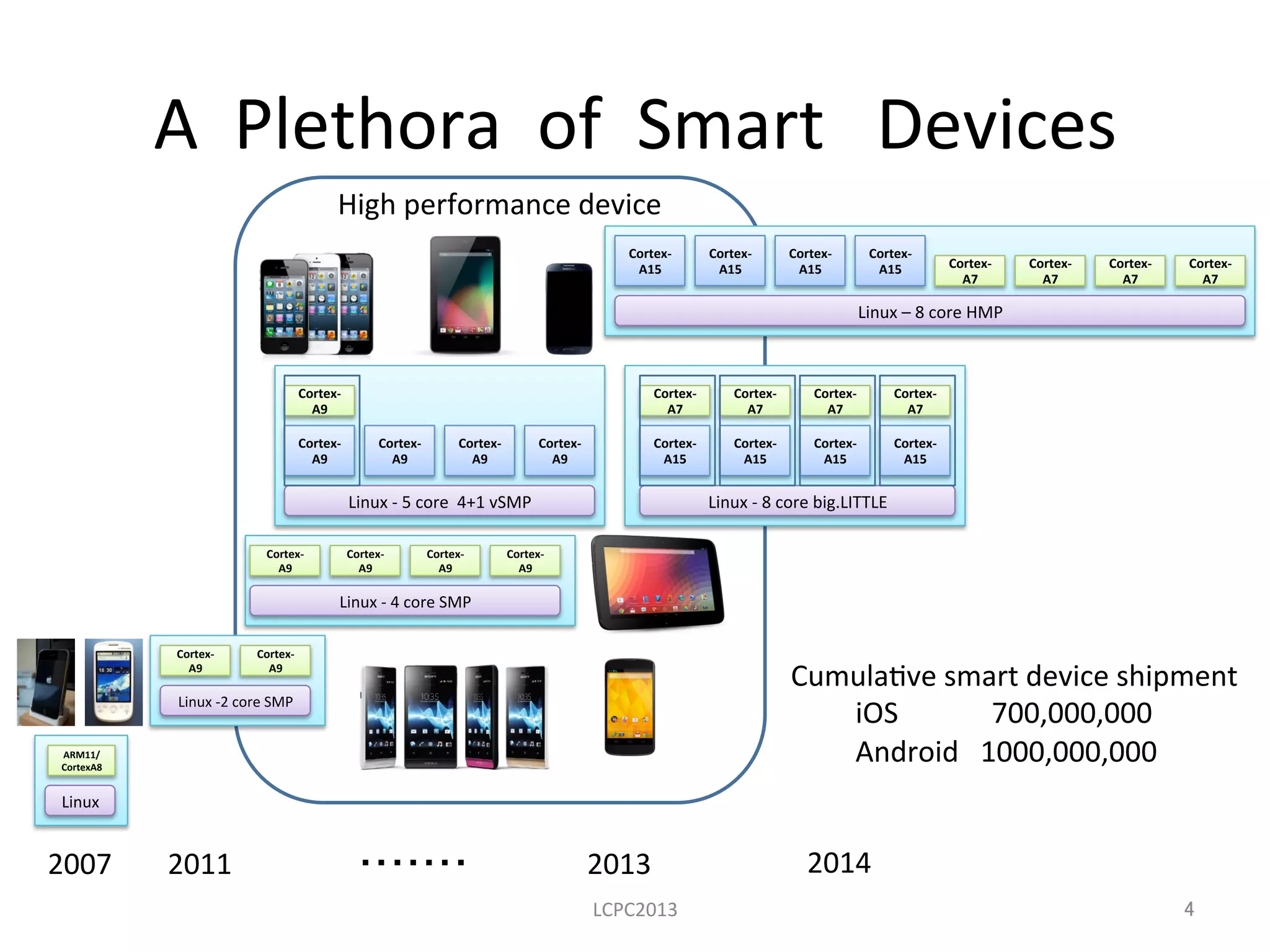

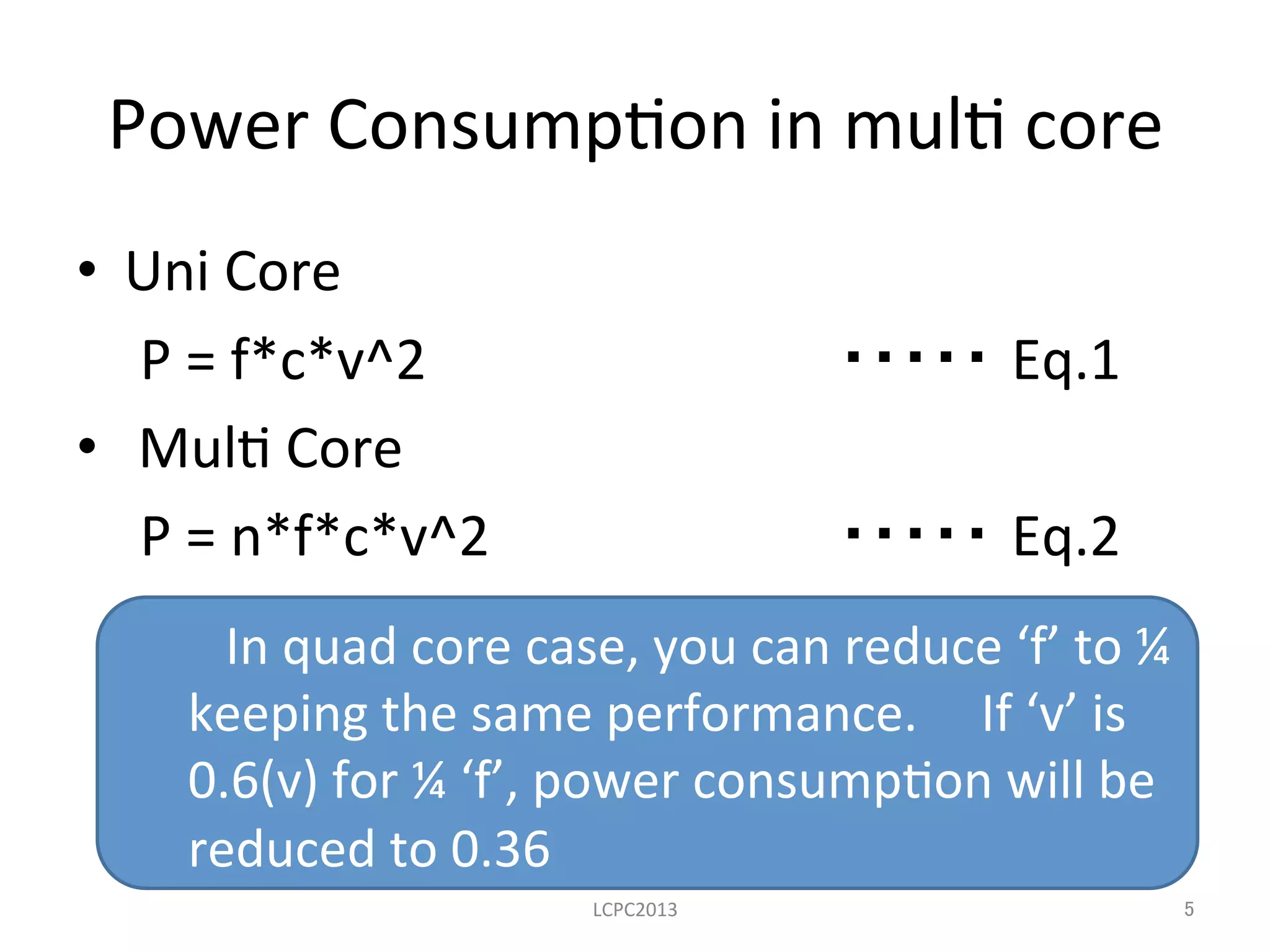

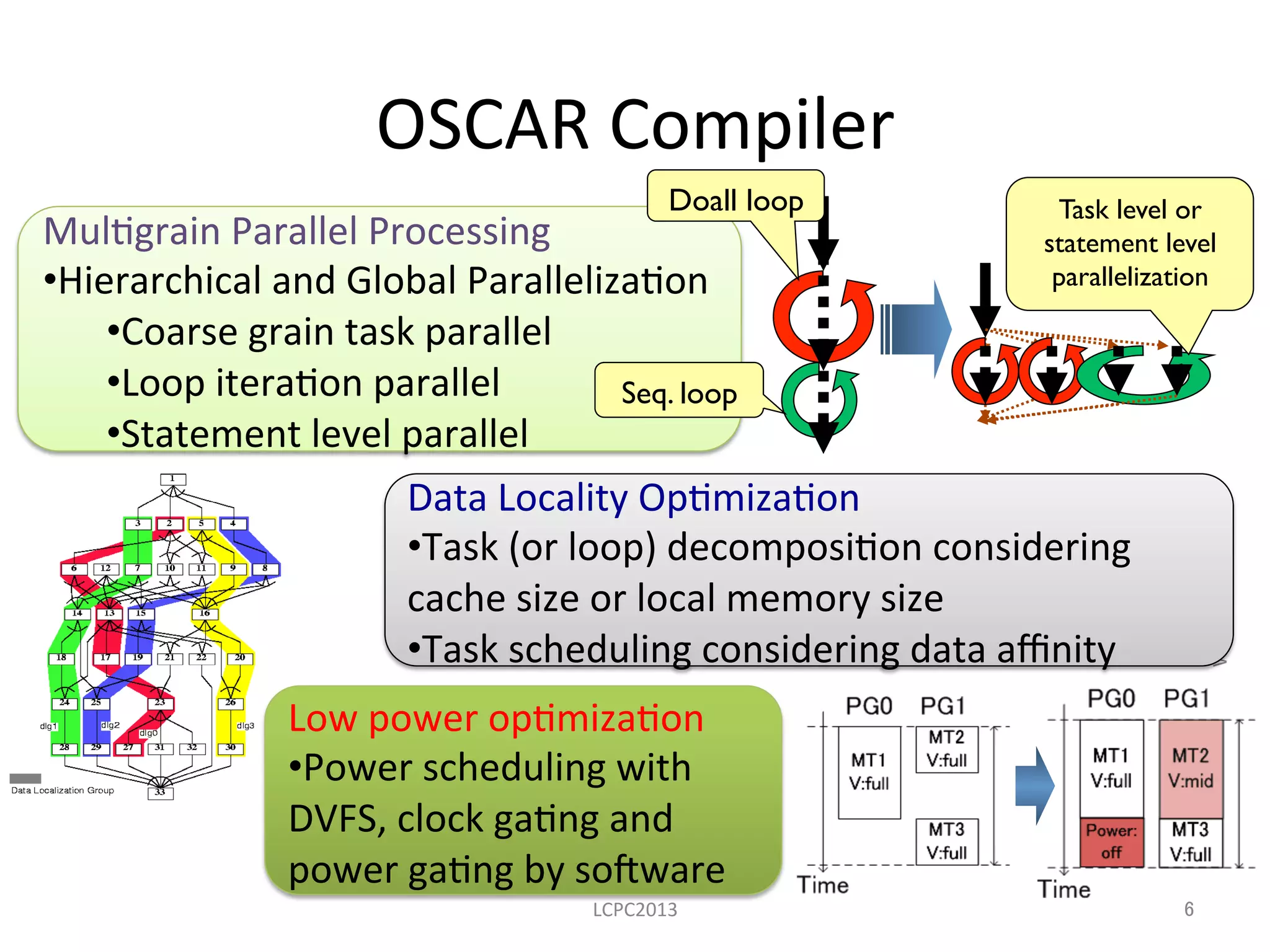

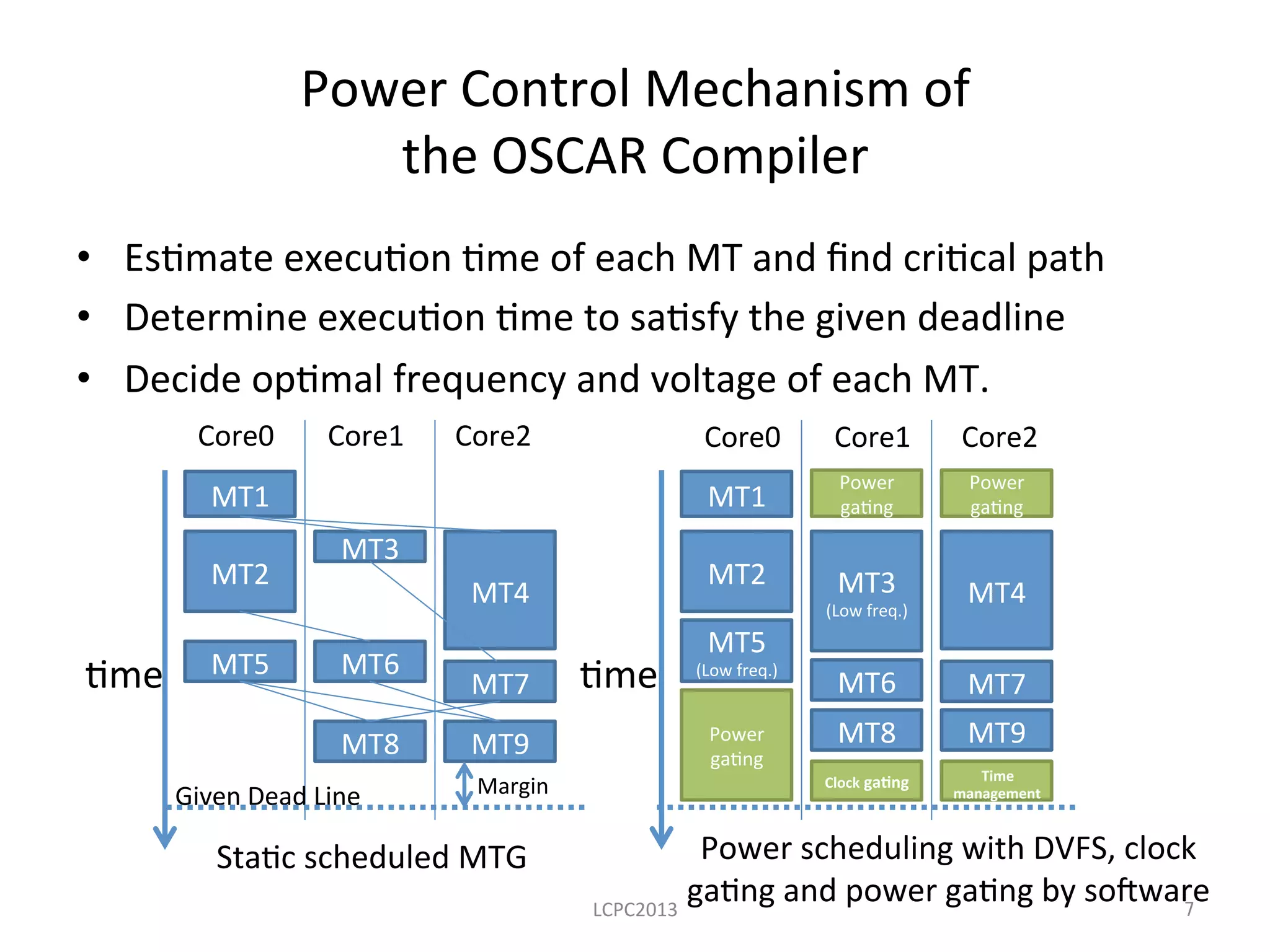

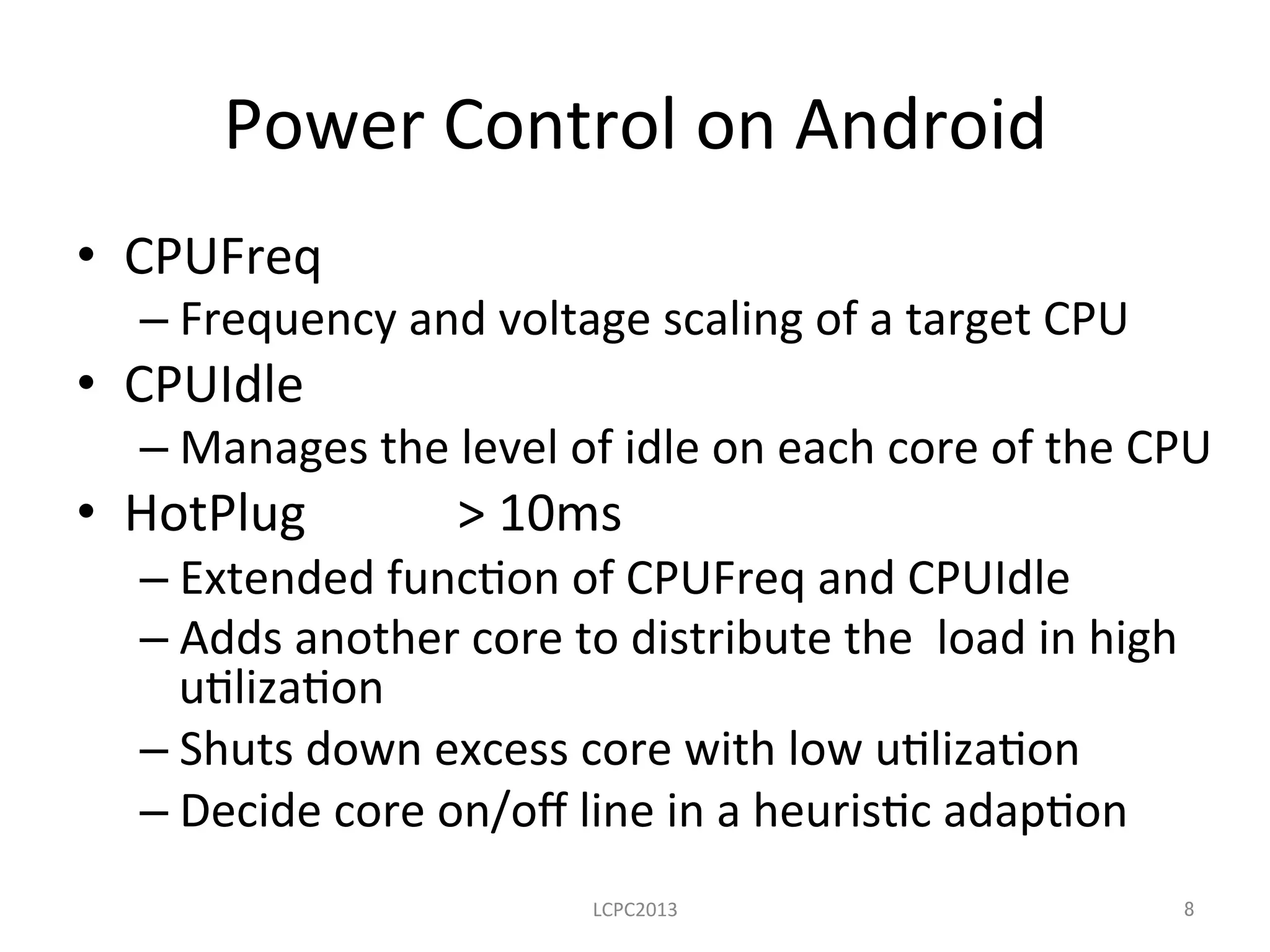

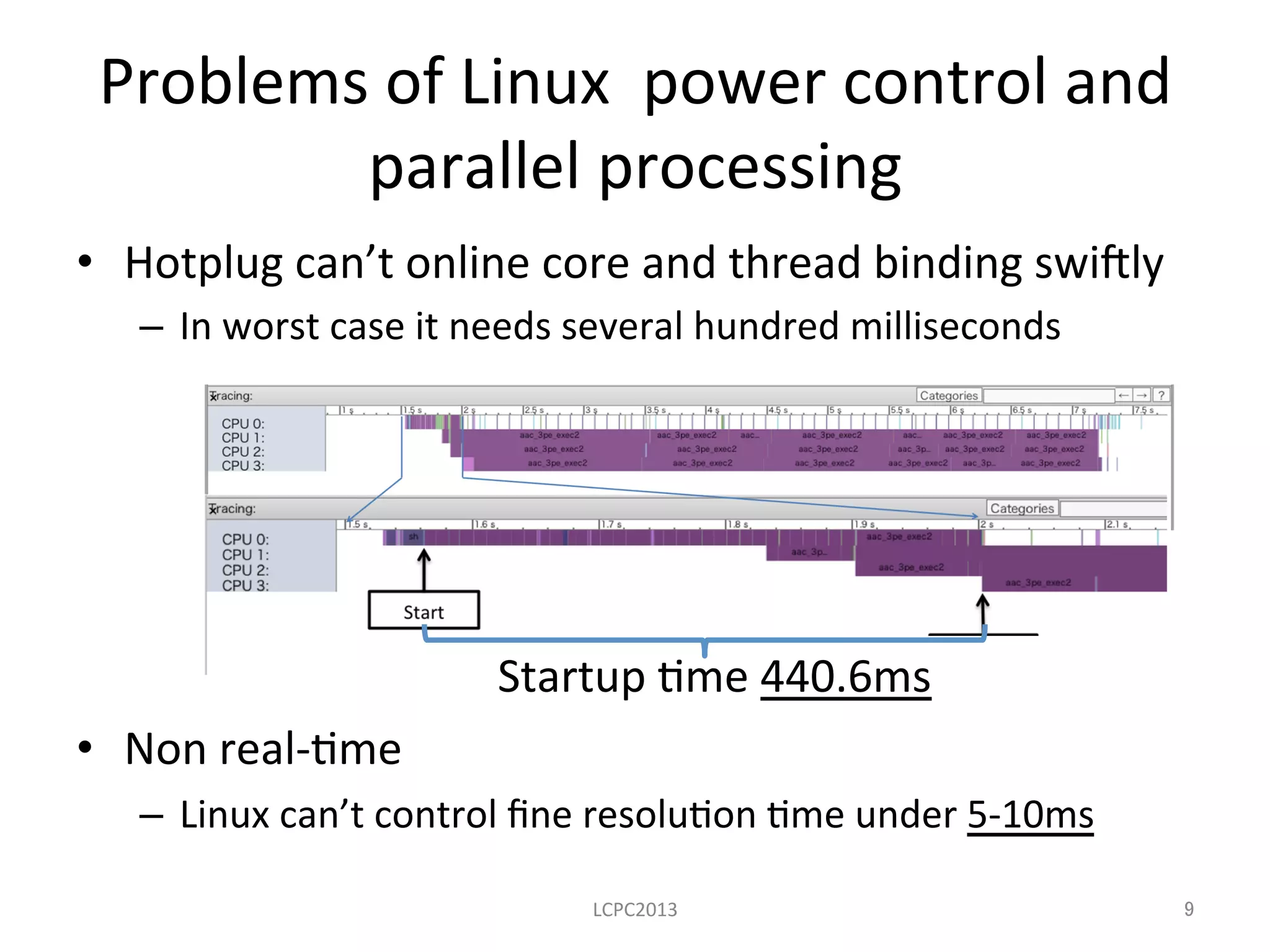

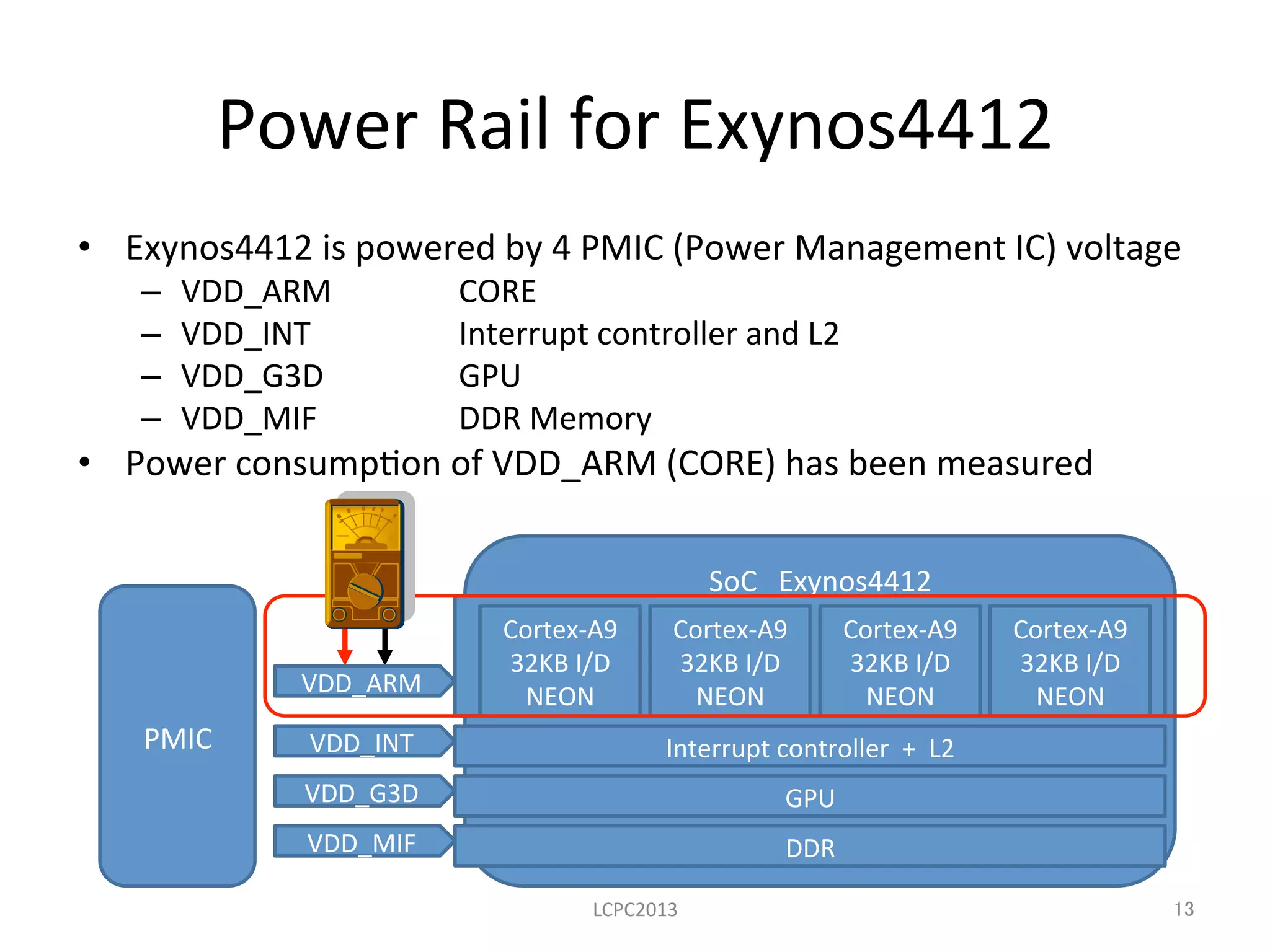

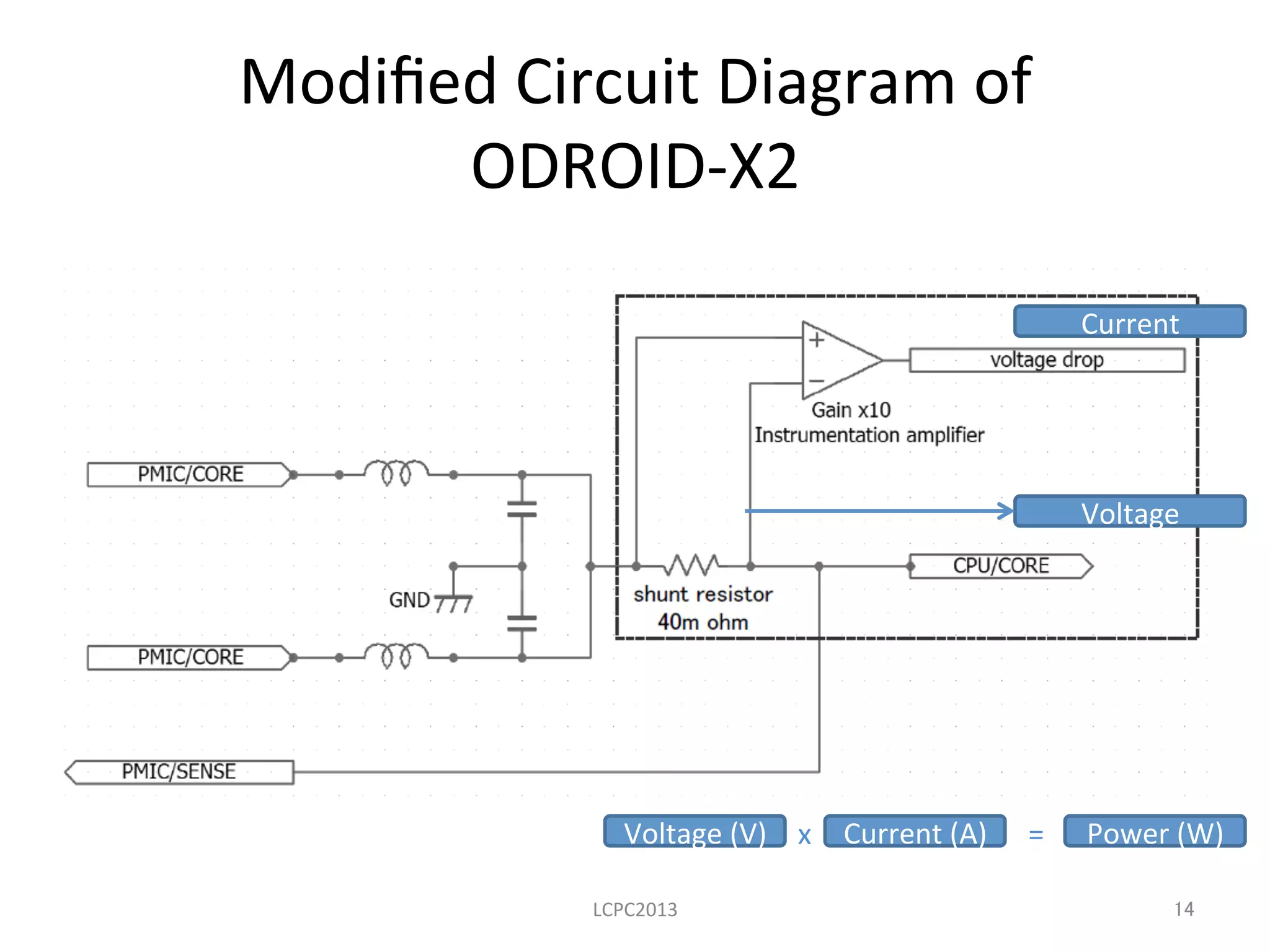

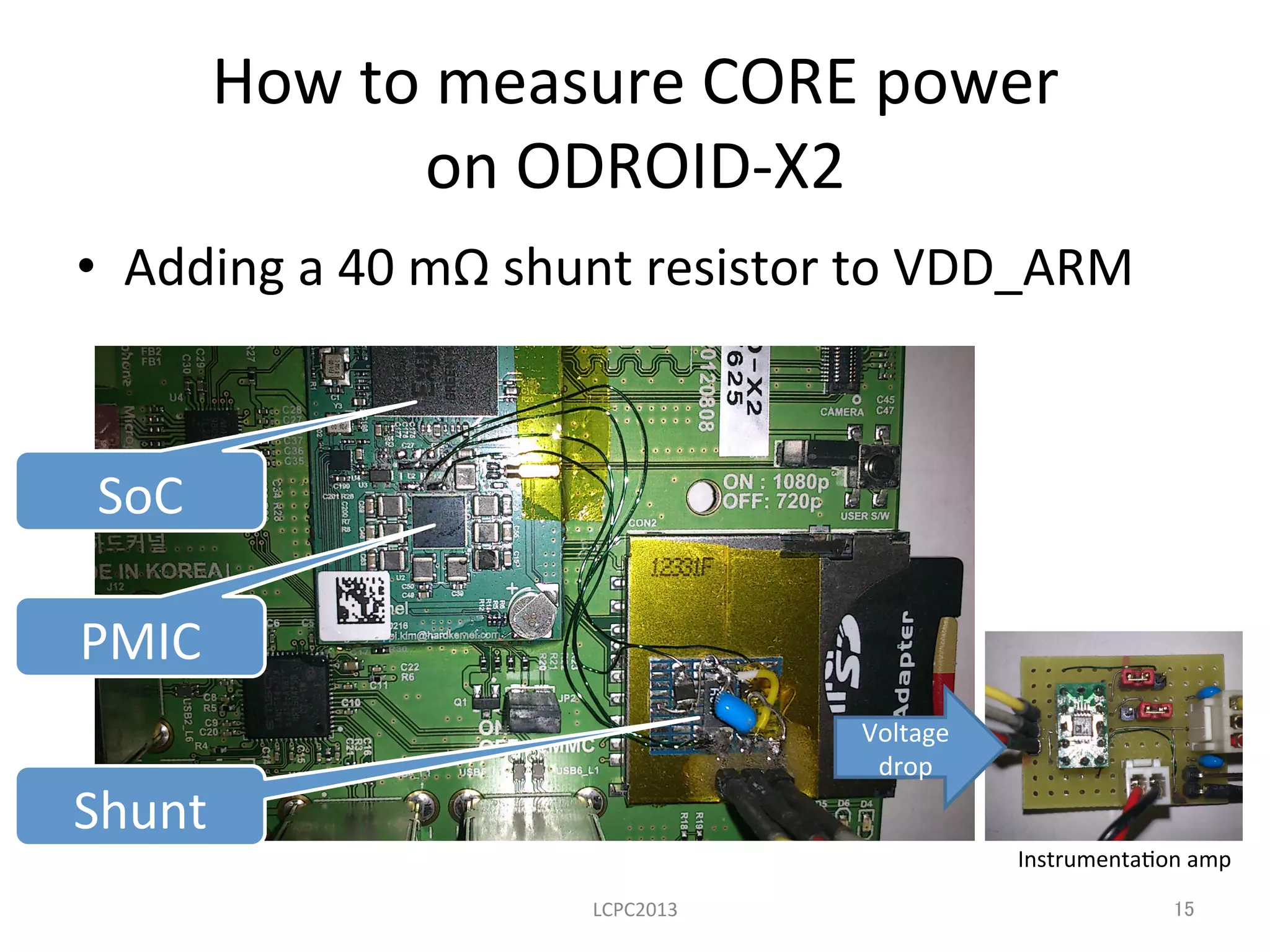

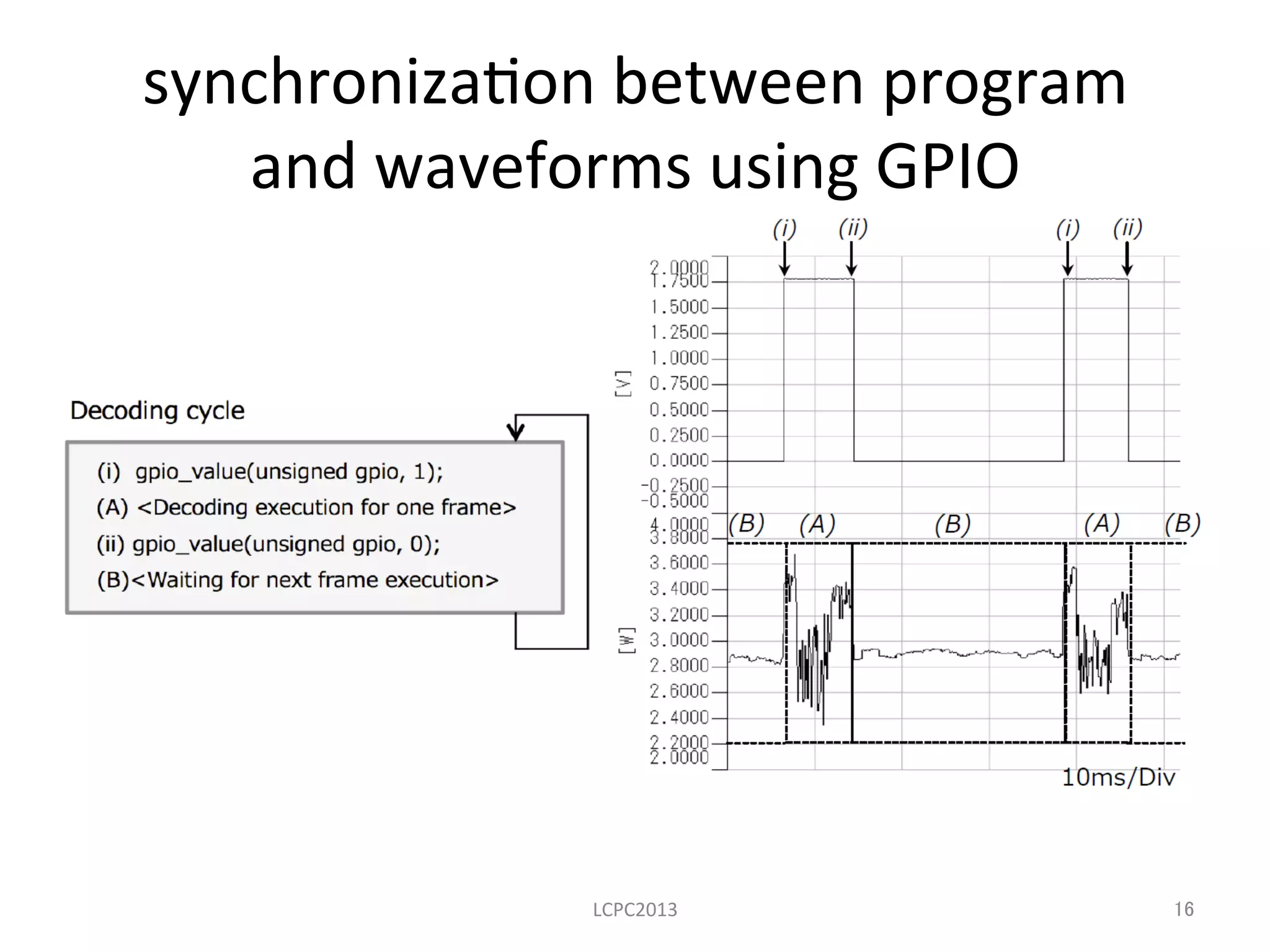

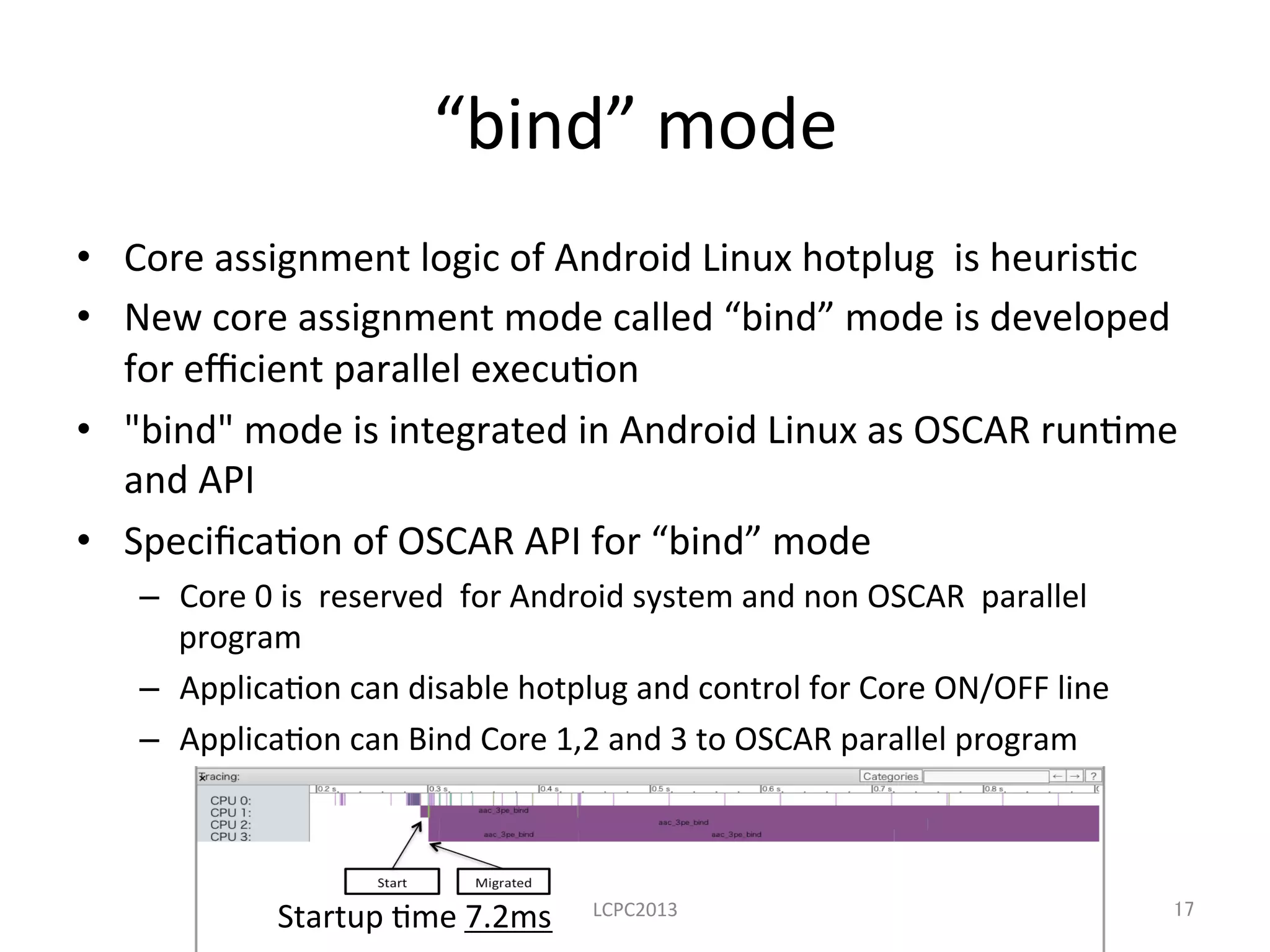

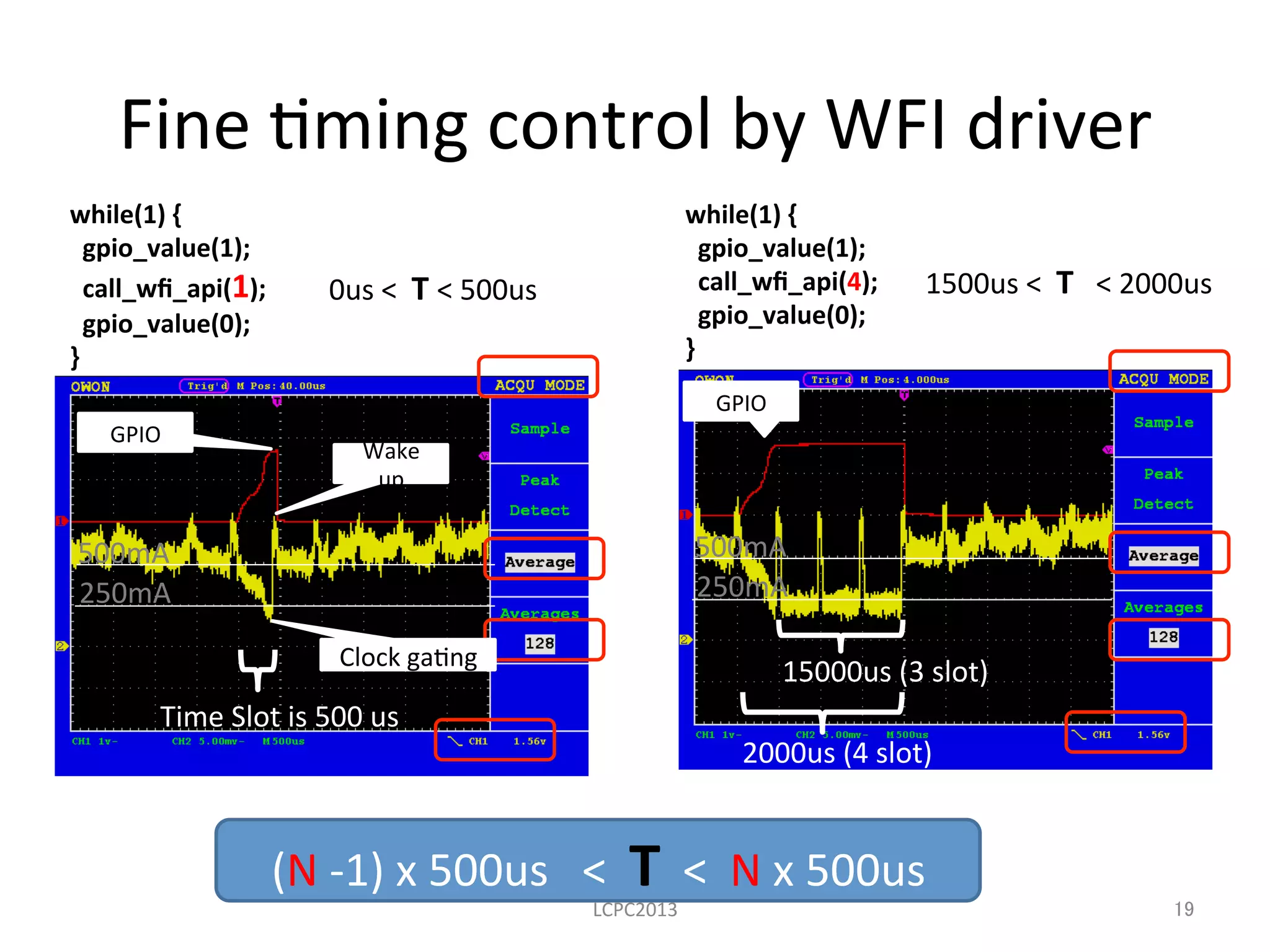

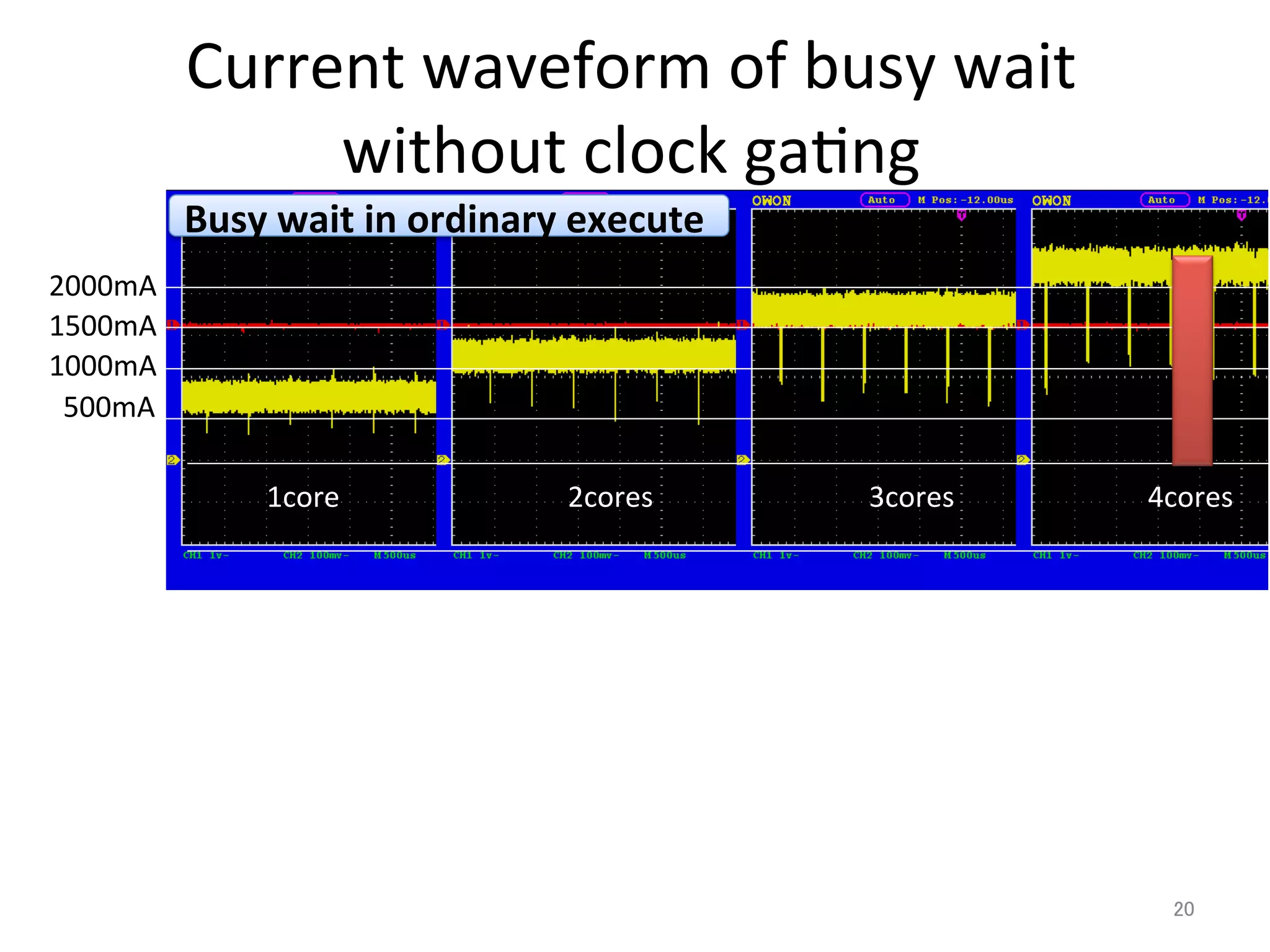

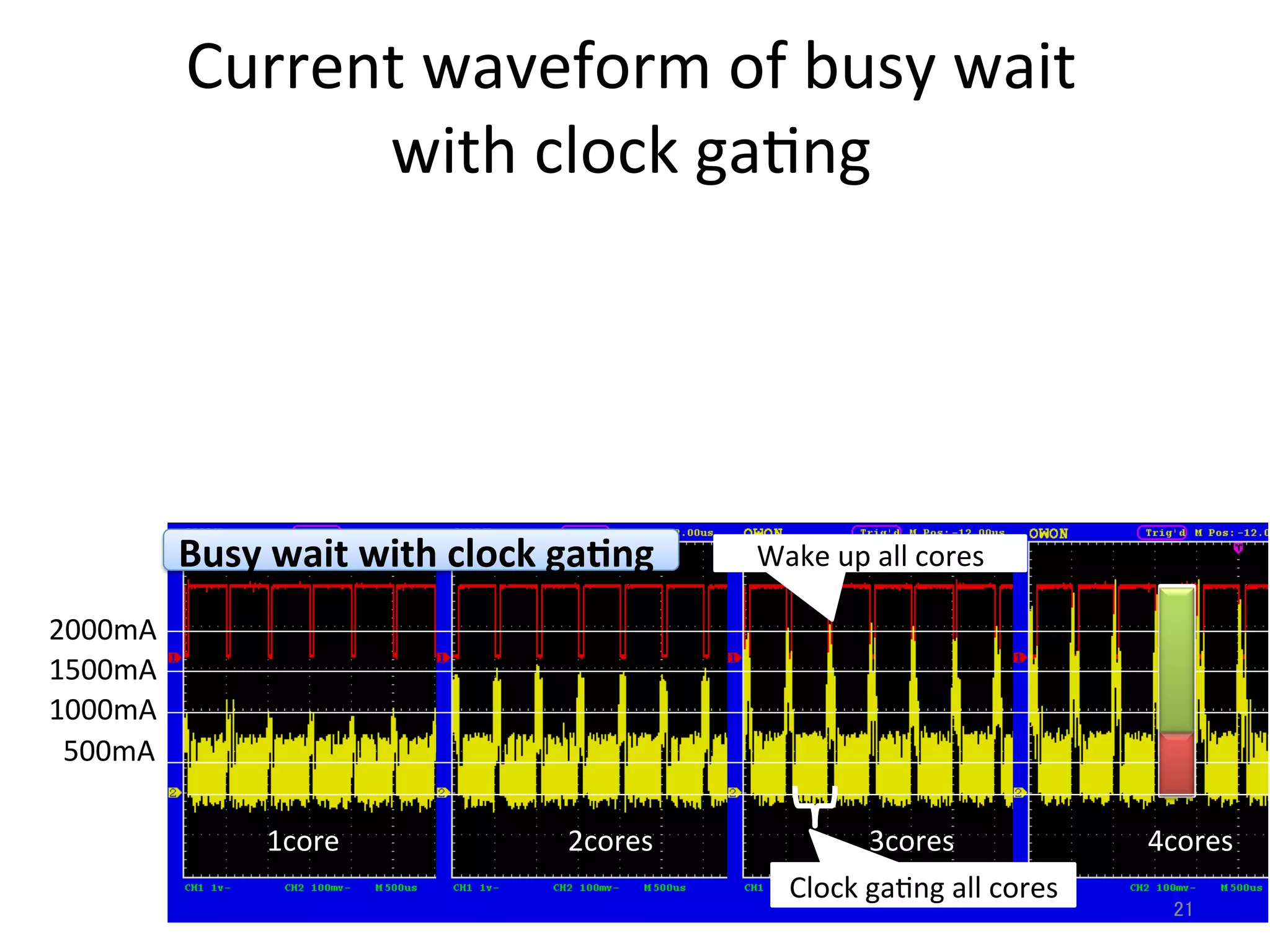

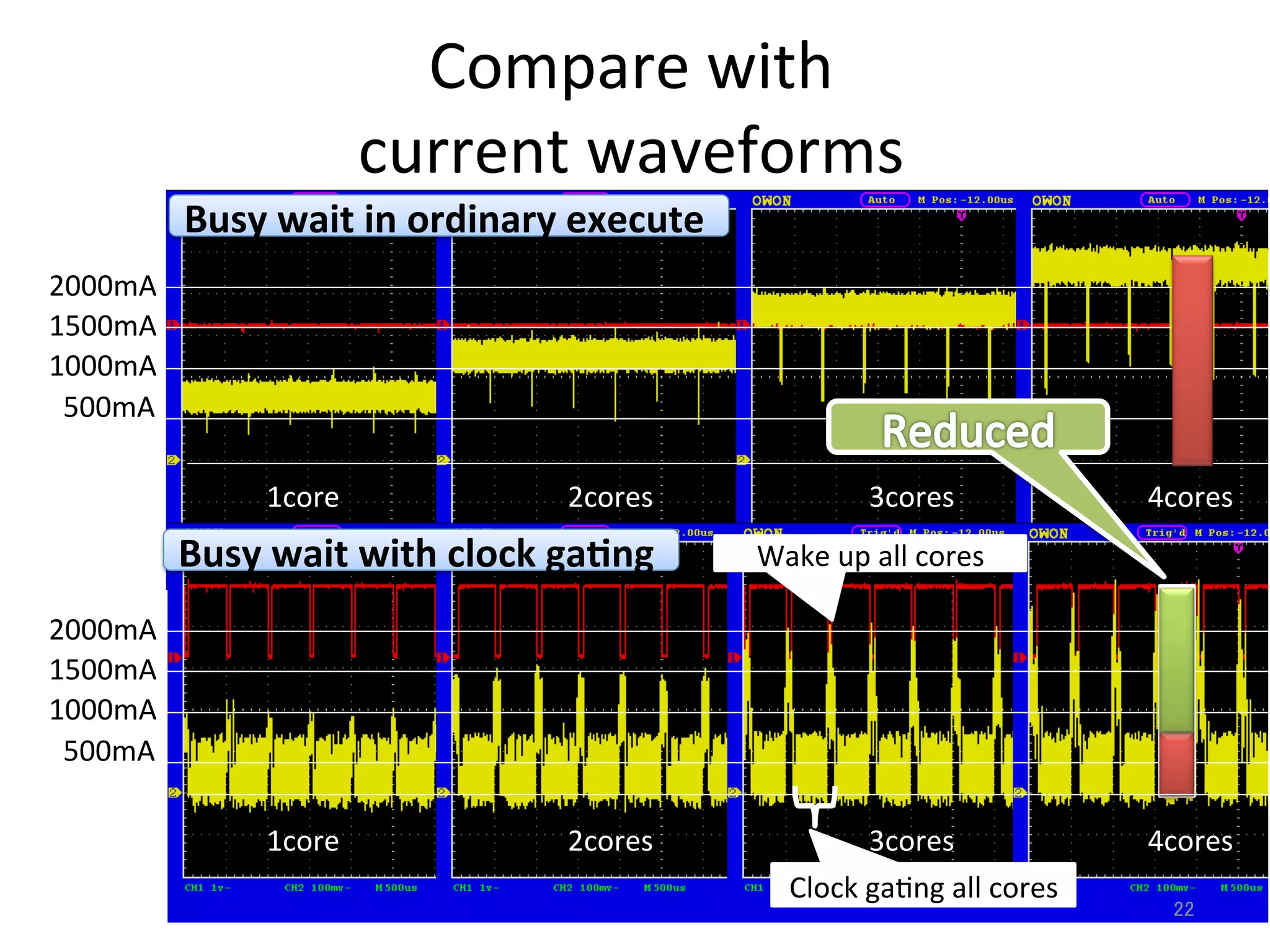

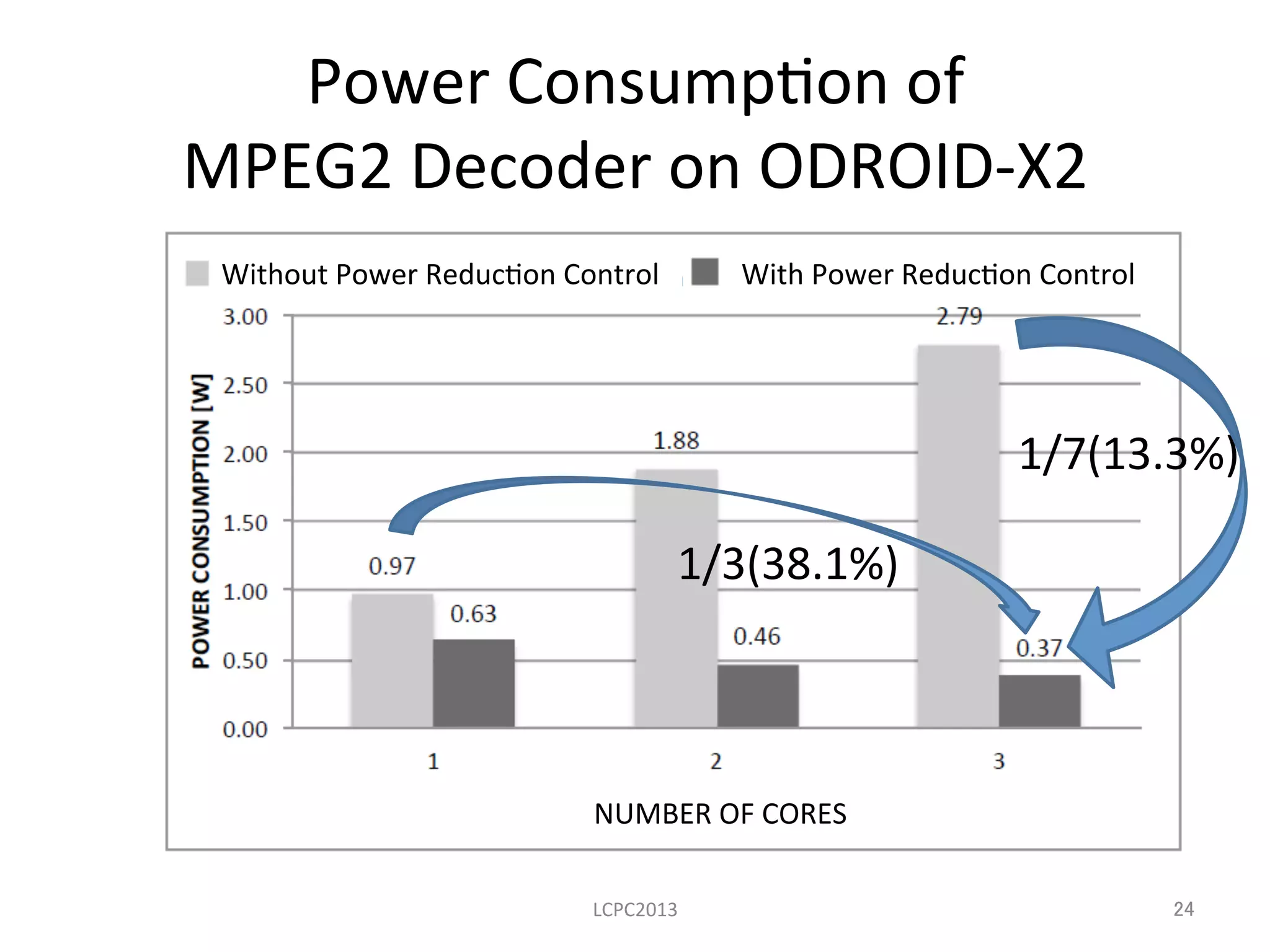

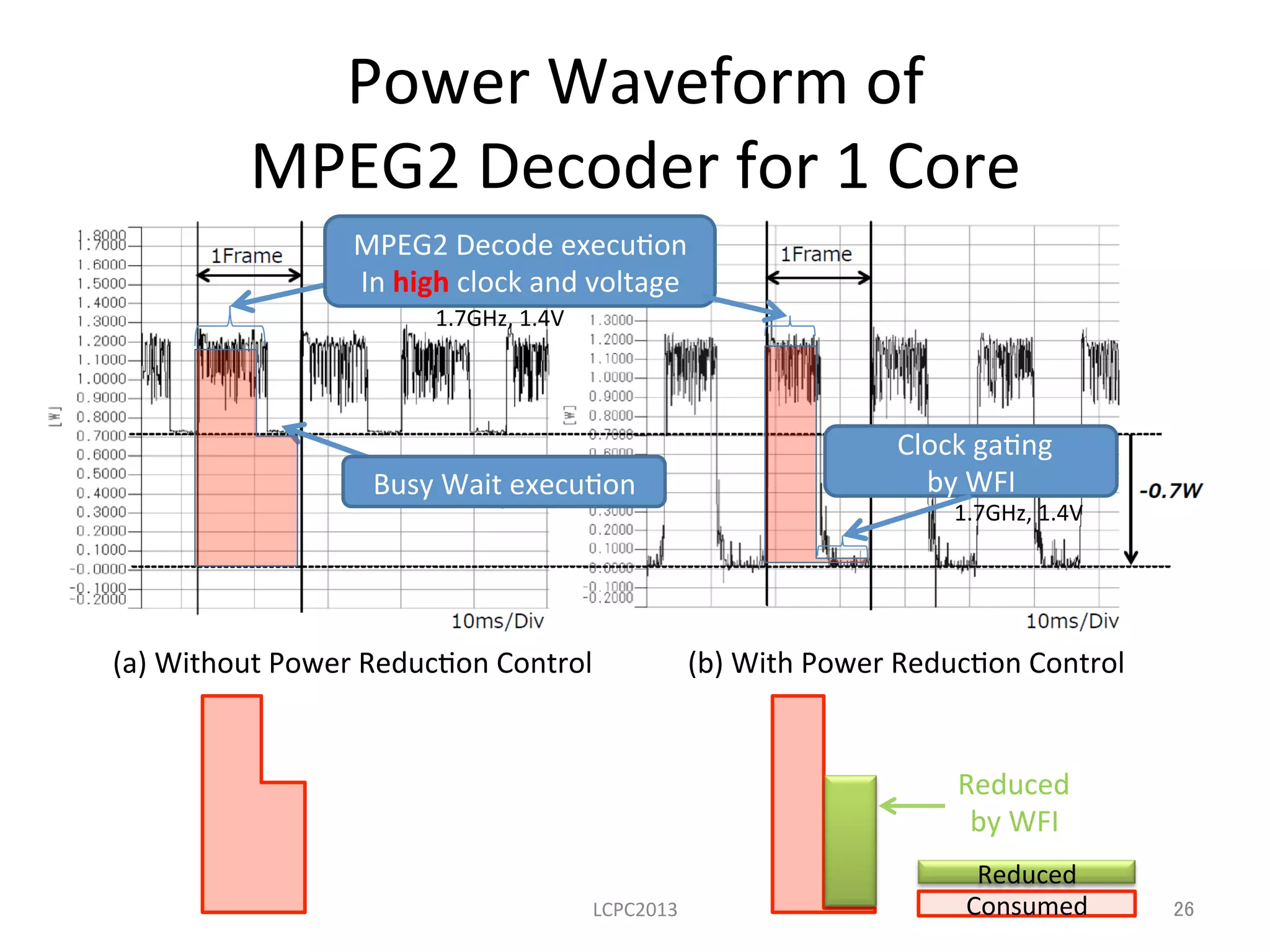

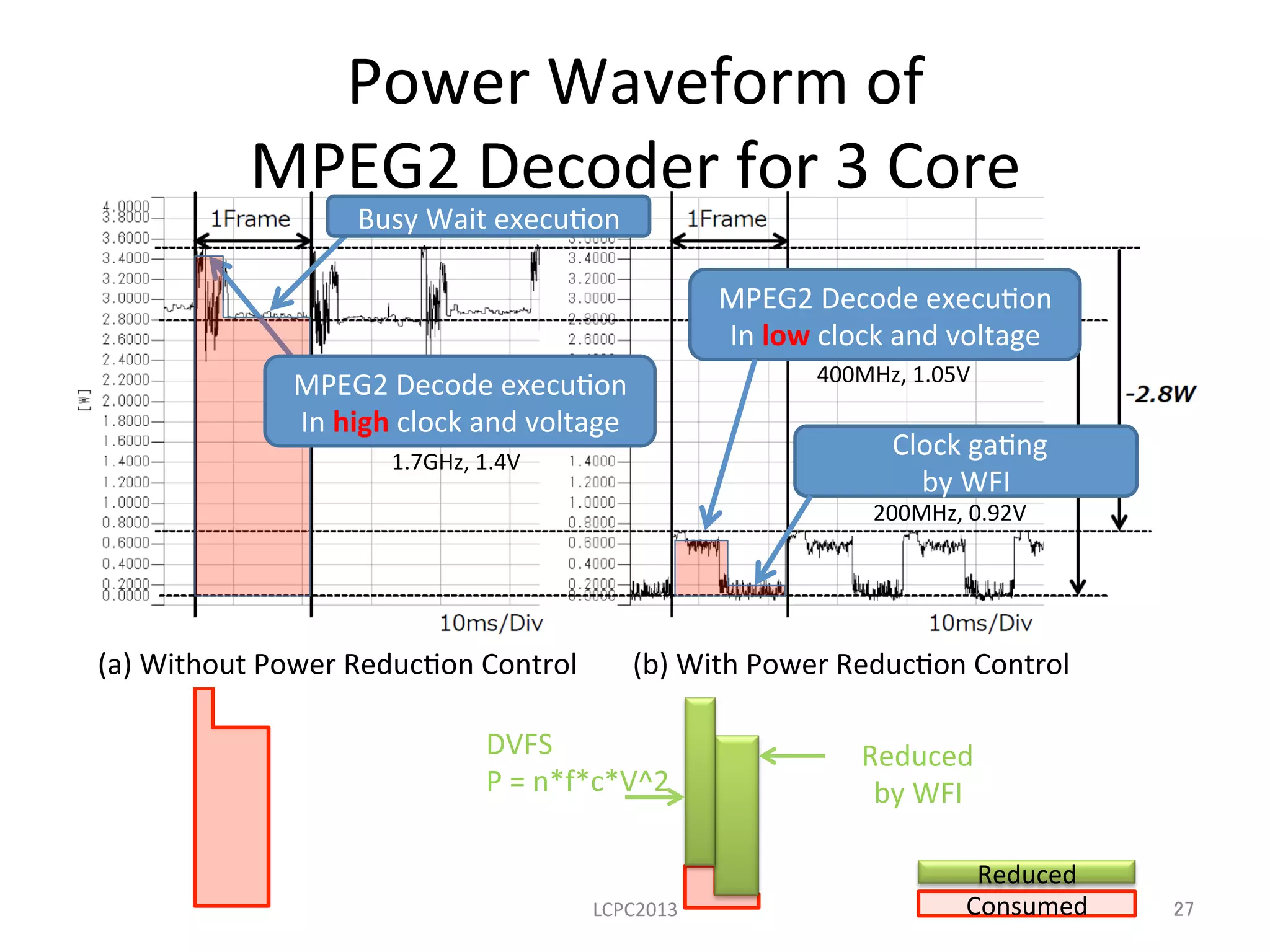

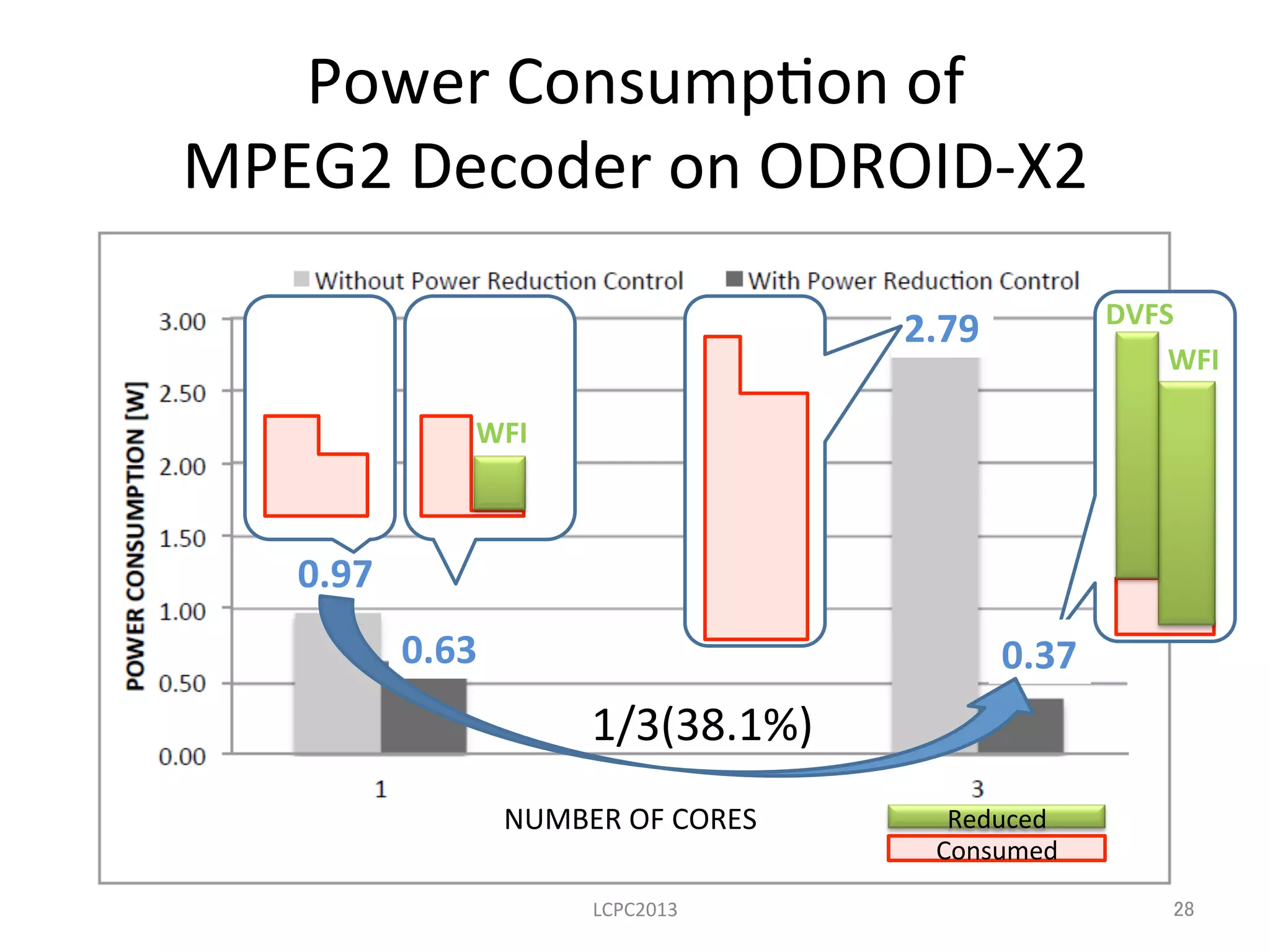

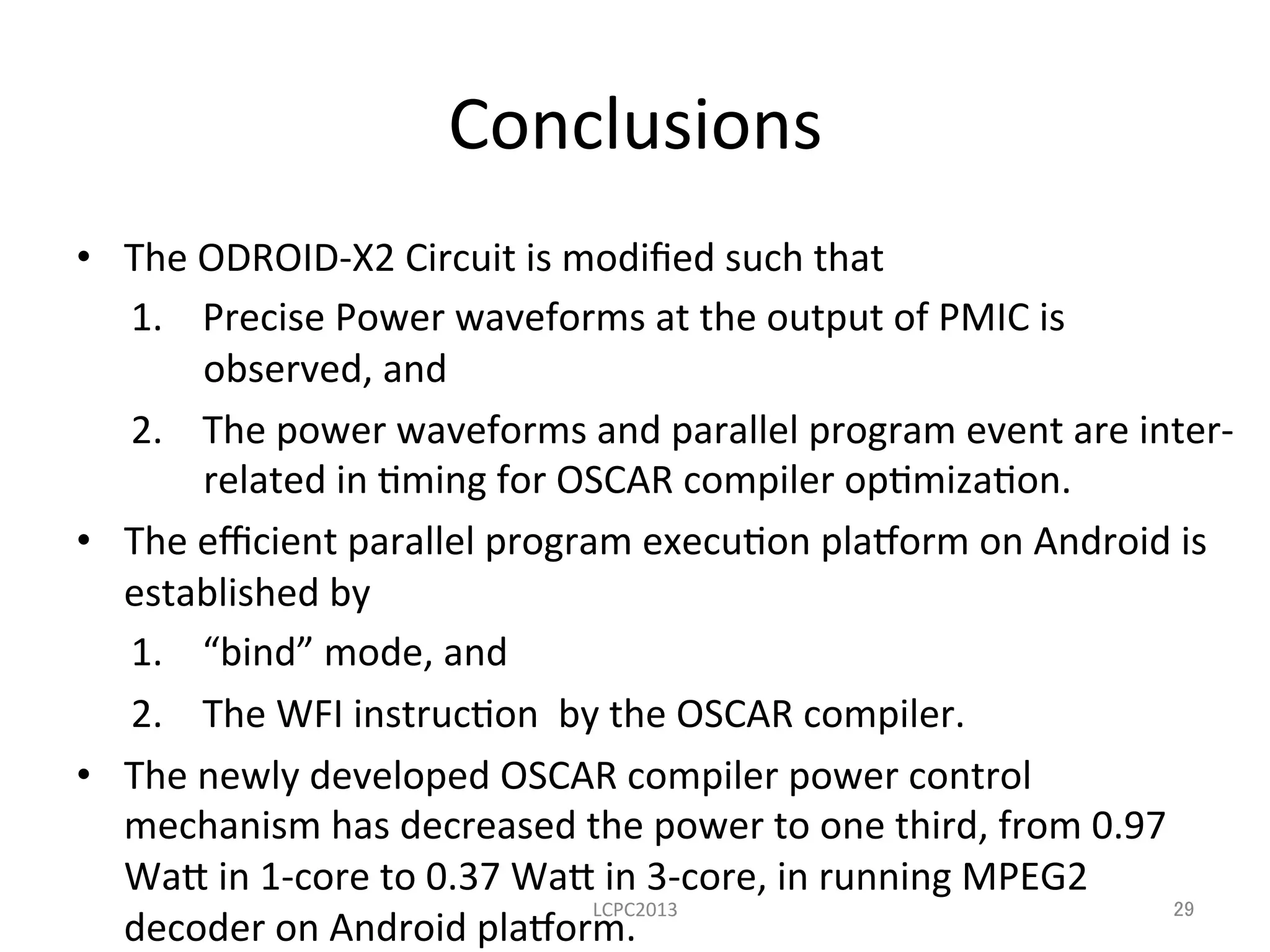

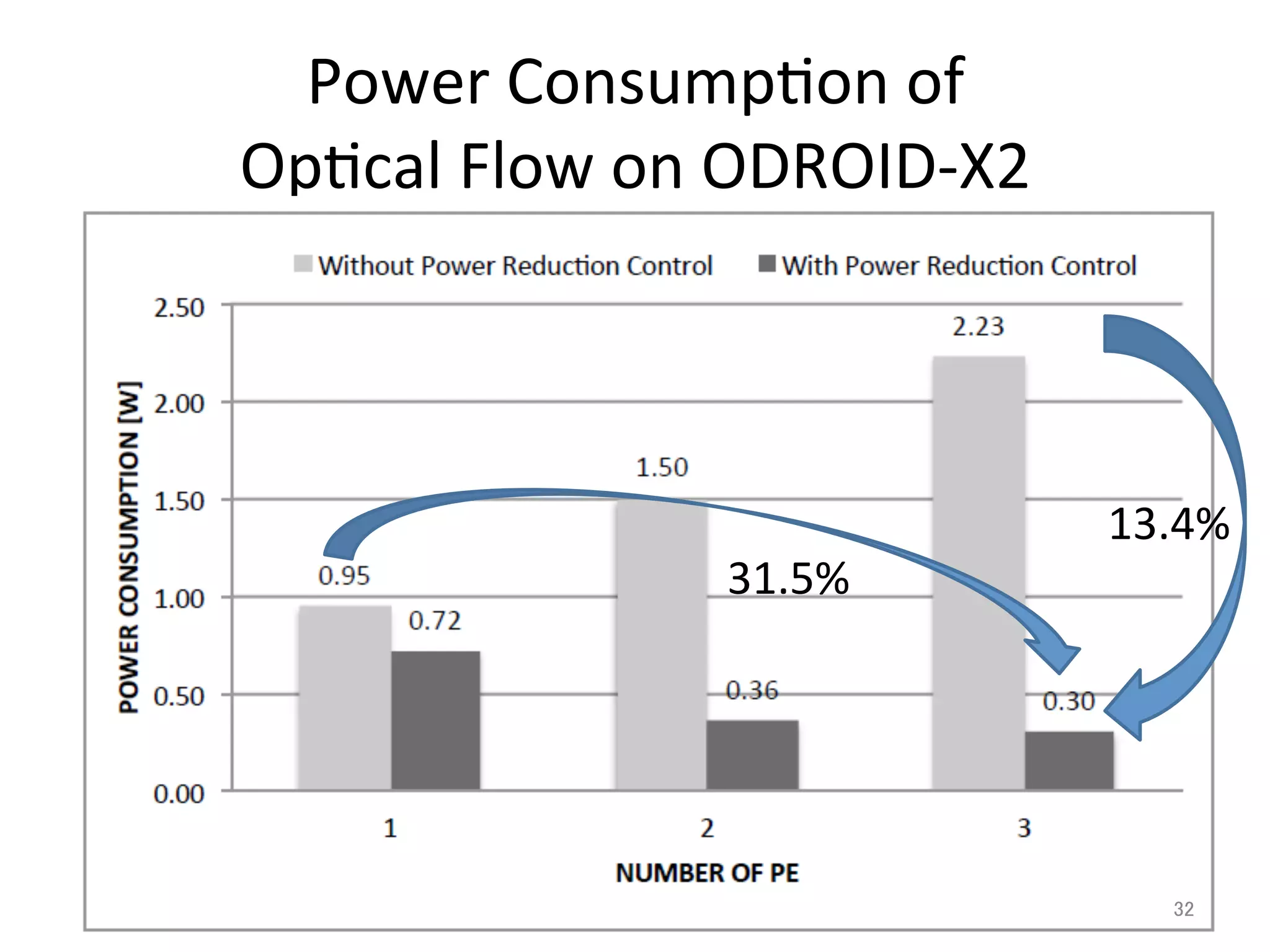

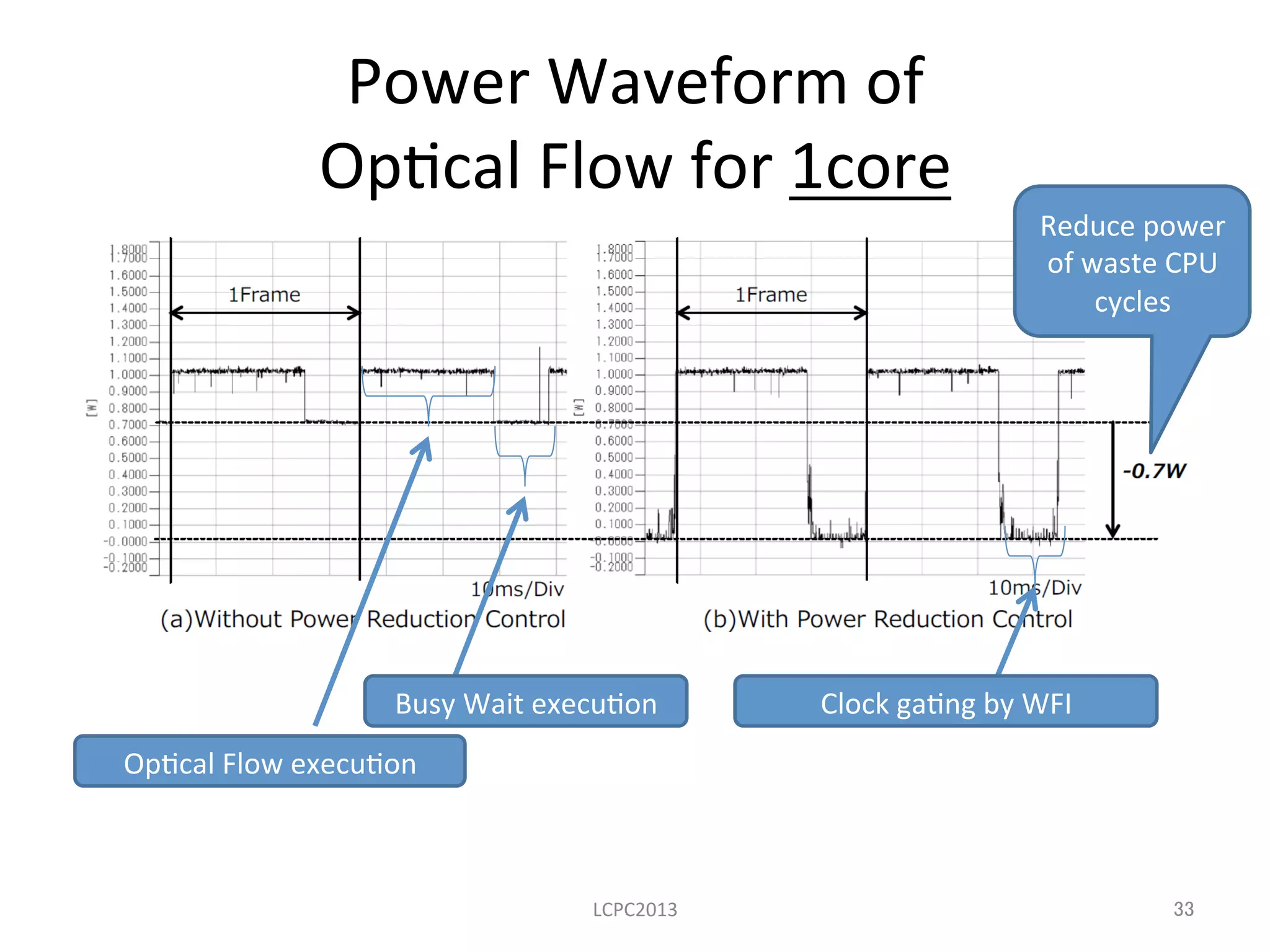

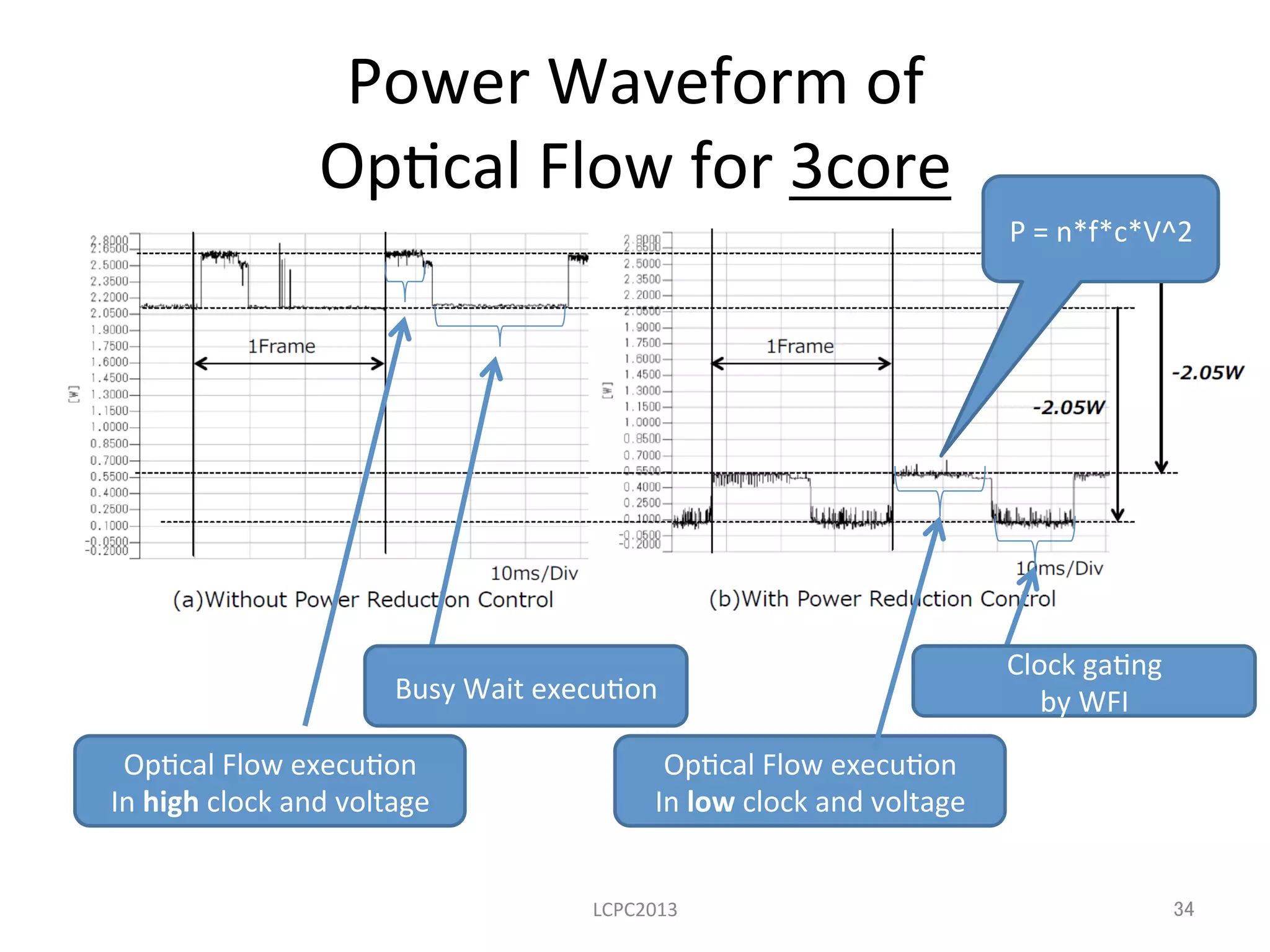

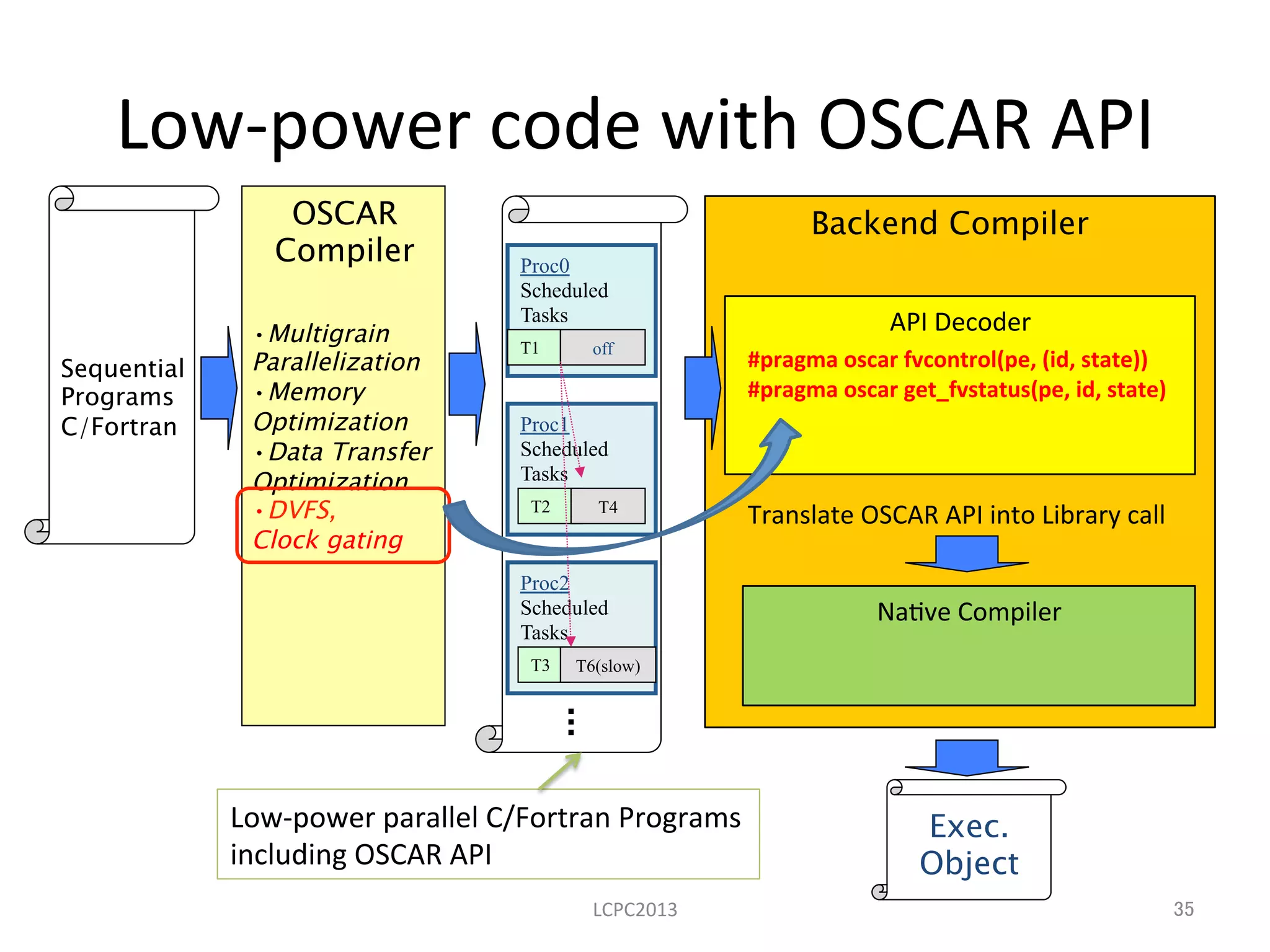

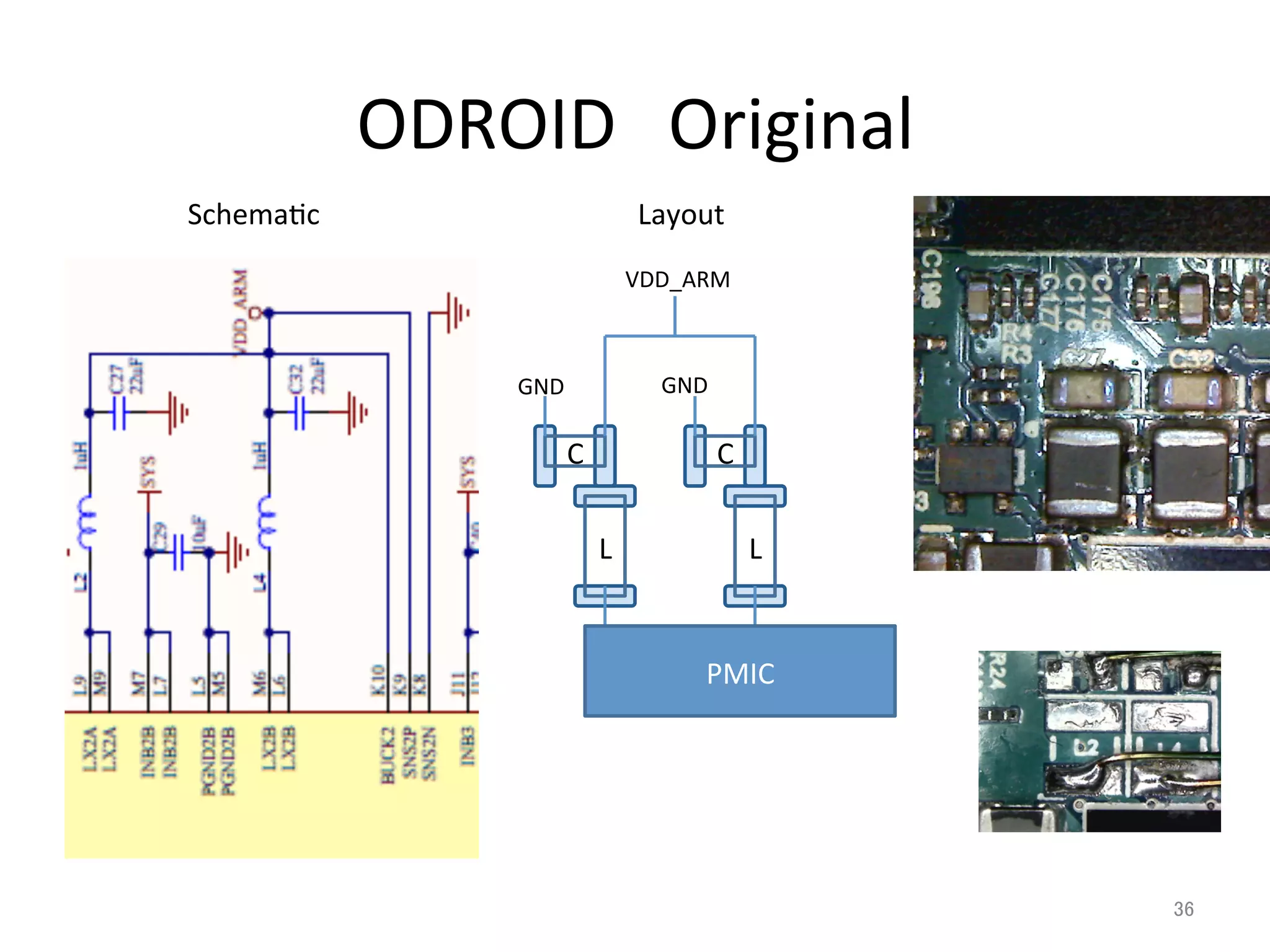

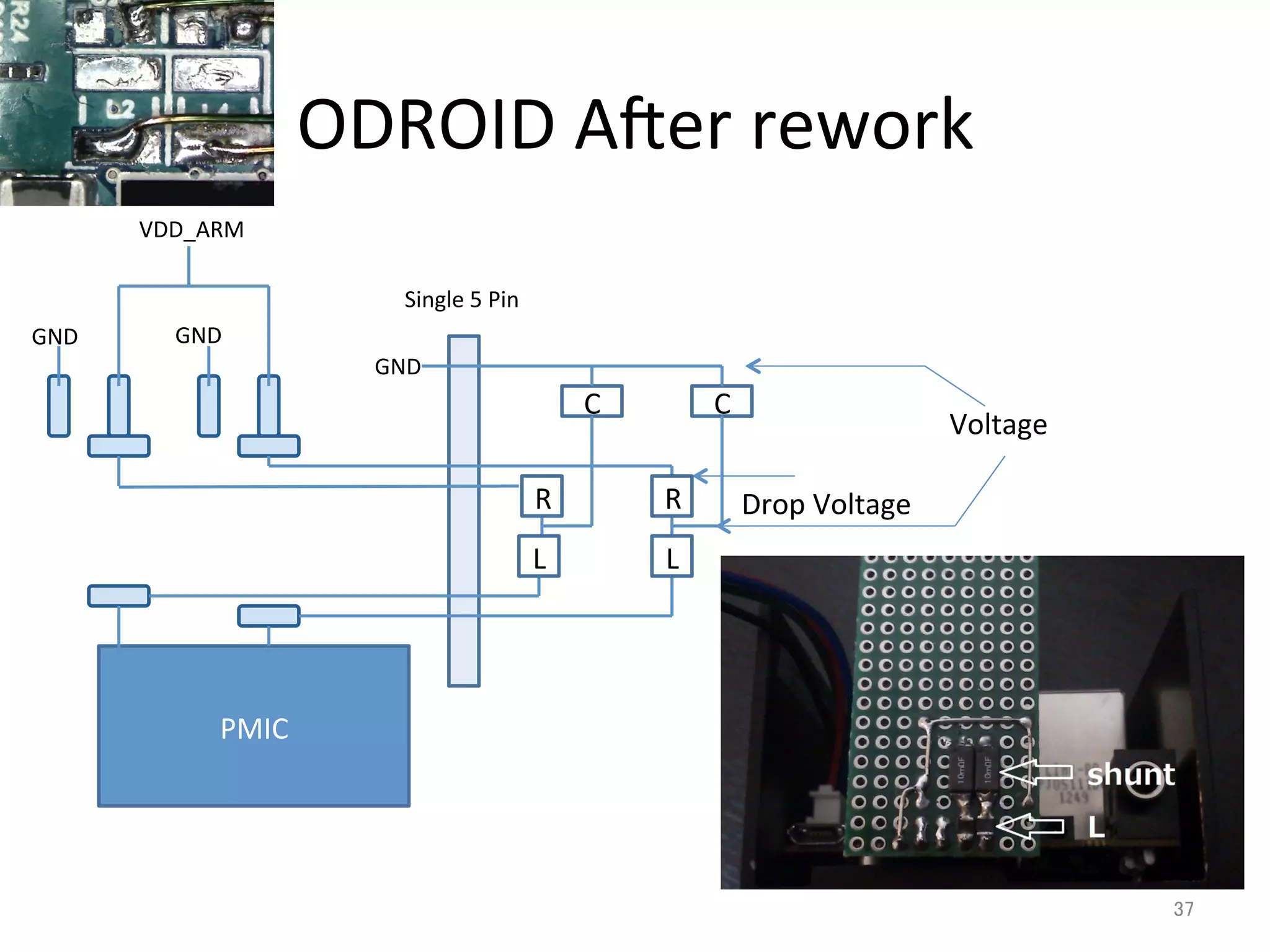

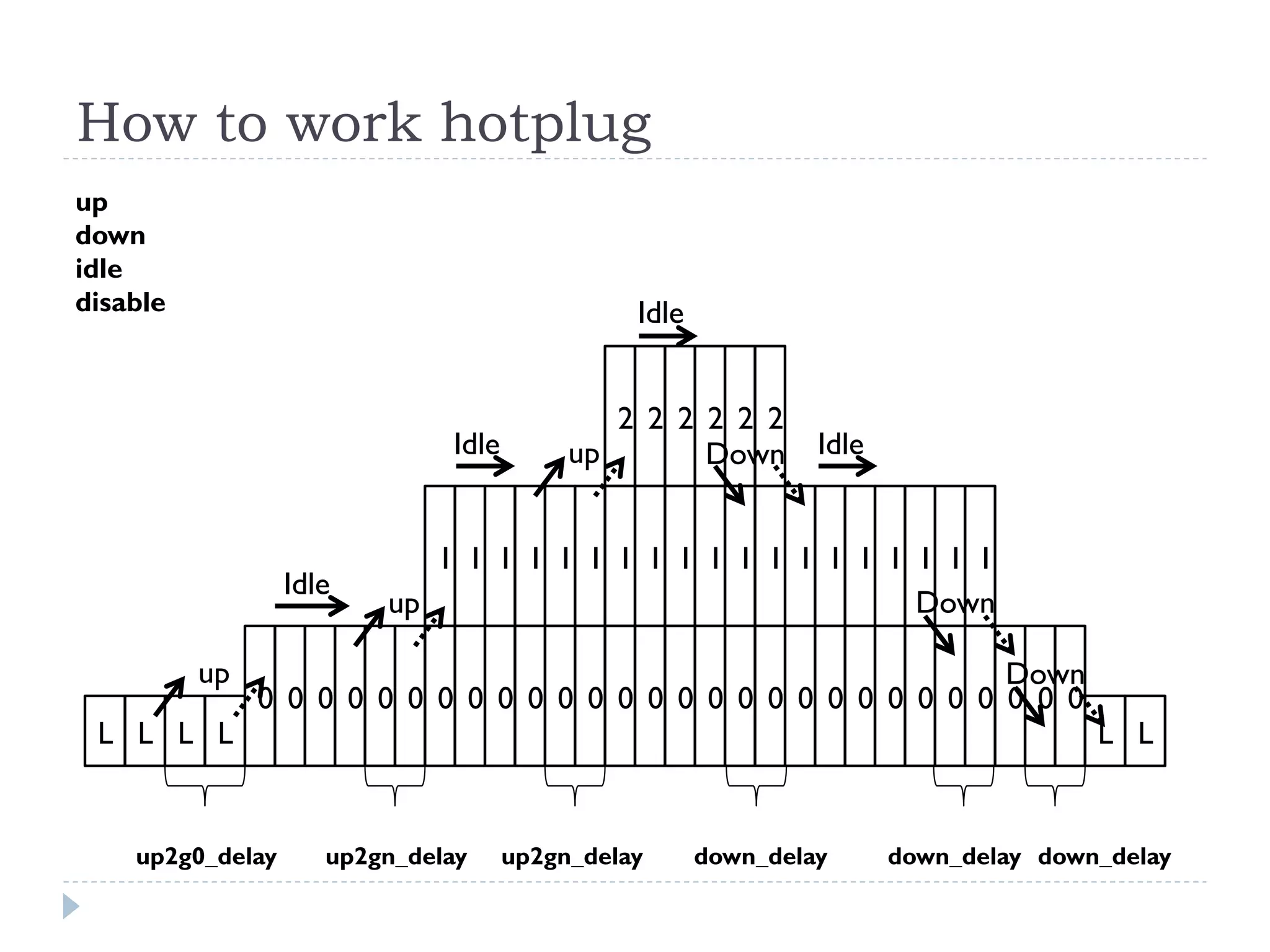

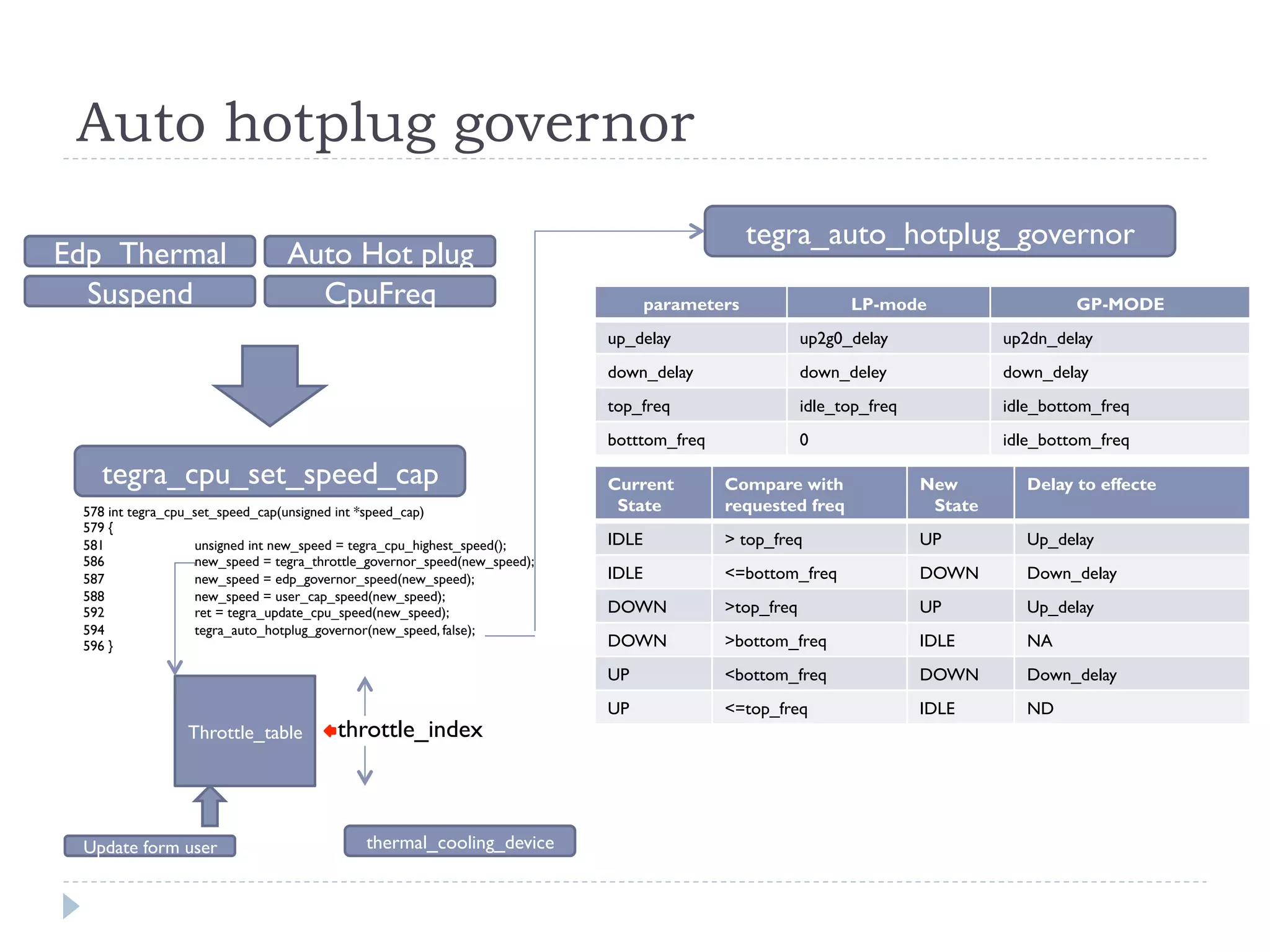

This document presents research on using compiler-controlled power reduction techniques on an Android platform with multiple cores. It discusses how the OSCAR compiler estimates execution times and schedules tasks to cores at different frequencies/voltages to meet deadlines while minimizing power. Experiments were conducted on an ODROID-X2 board with an Exynos4412 quad-core chip to evaluate parallelizing applications and applying dynamic voltage and frequency scaling, clock gating, and power gating through software to reduce power consumption.