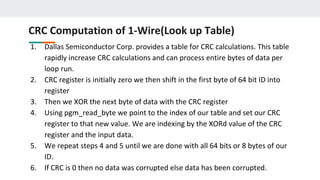

One Wire Serial Communication allows for transmission of data over a single wire between a master and slave device. It uses precise timing of signal levels to delineate bits. The protocol involves the master sending a reset pulse, slaves responding with presence pulses, then the master sending ROM and memory commands. Communication follows a standard sequence of reset, presence, ROM command, and memory command. CRC is used for error checking.