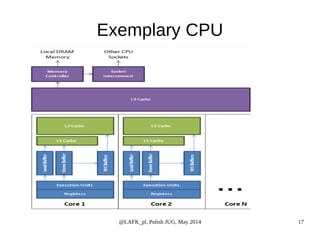

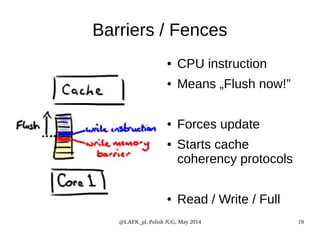

The document discusses the complexities and rules of the Java Memory Model (JMM), addressing issues related to memory consistency, execution behaviors, and optimization strategies for multi-threaded programming. It critiques previous models and outlines the importance of proper usage of constructs like 'final,' 'volatile,' and 'synchronized' to ensure visibility and correctness in concurrent Java applications. The text also touches on the role of CPU architectures in understanding memory barriers and optimization techniques.