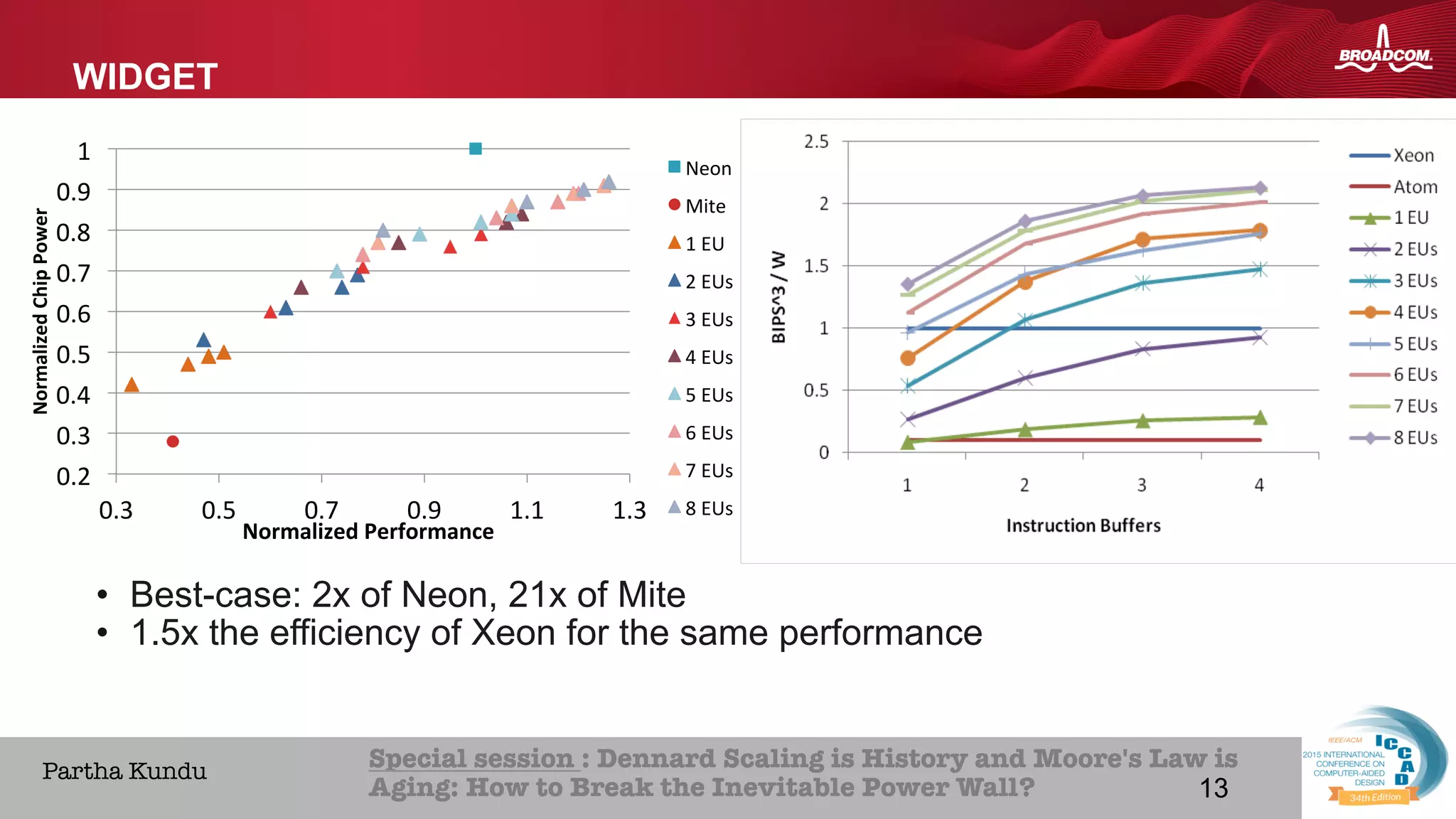

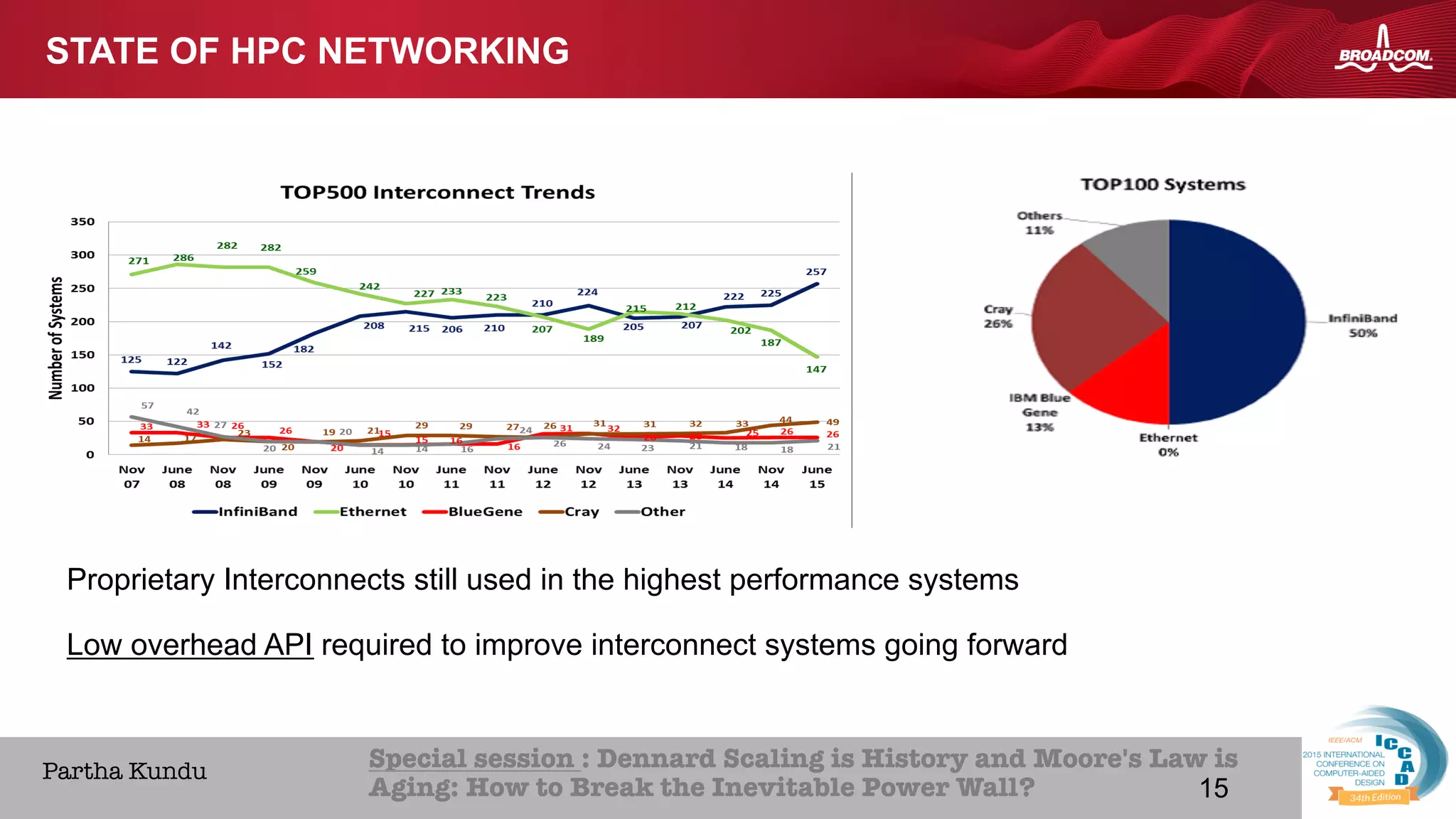

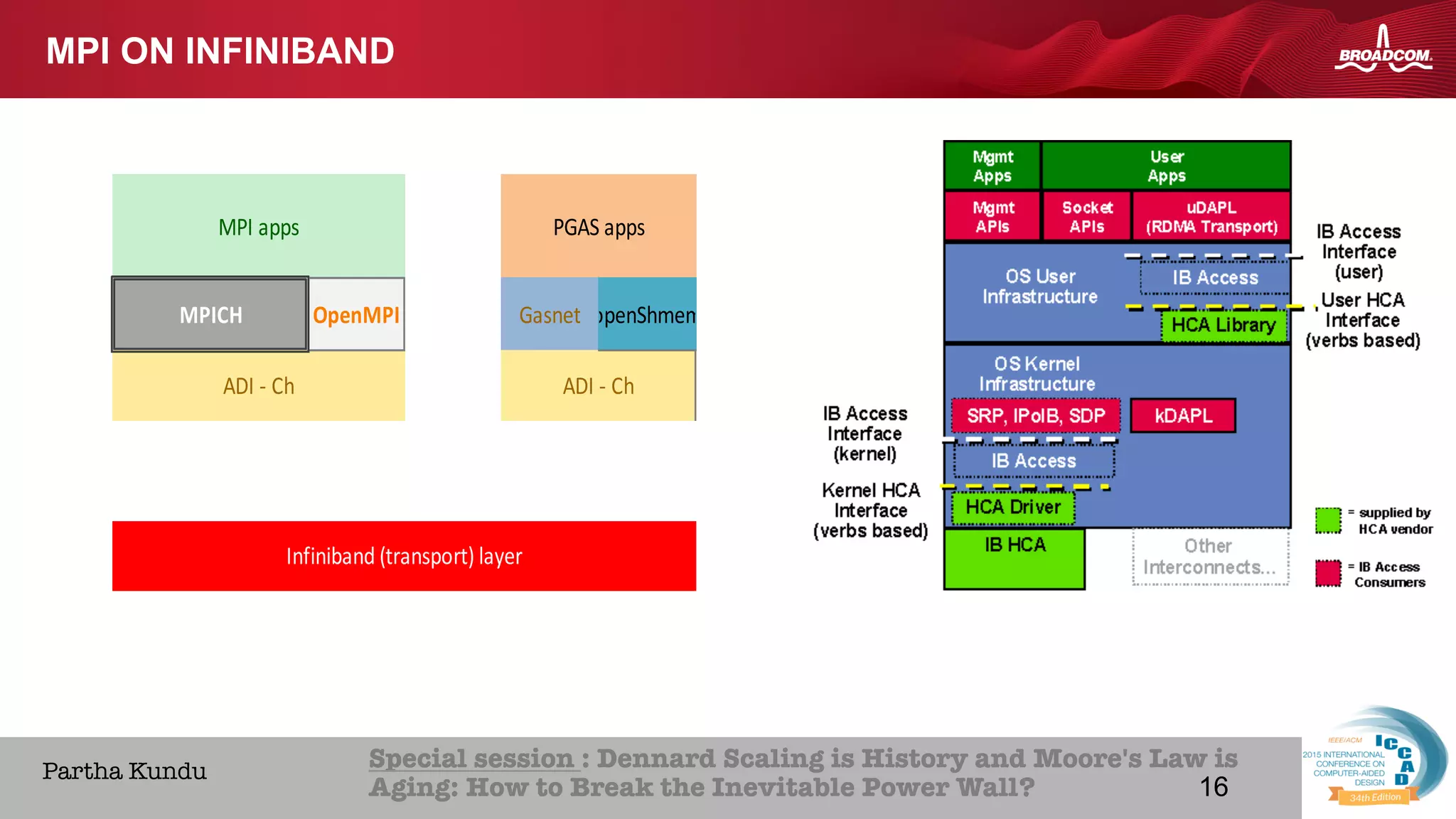

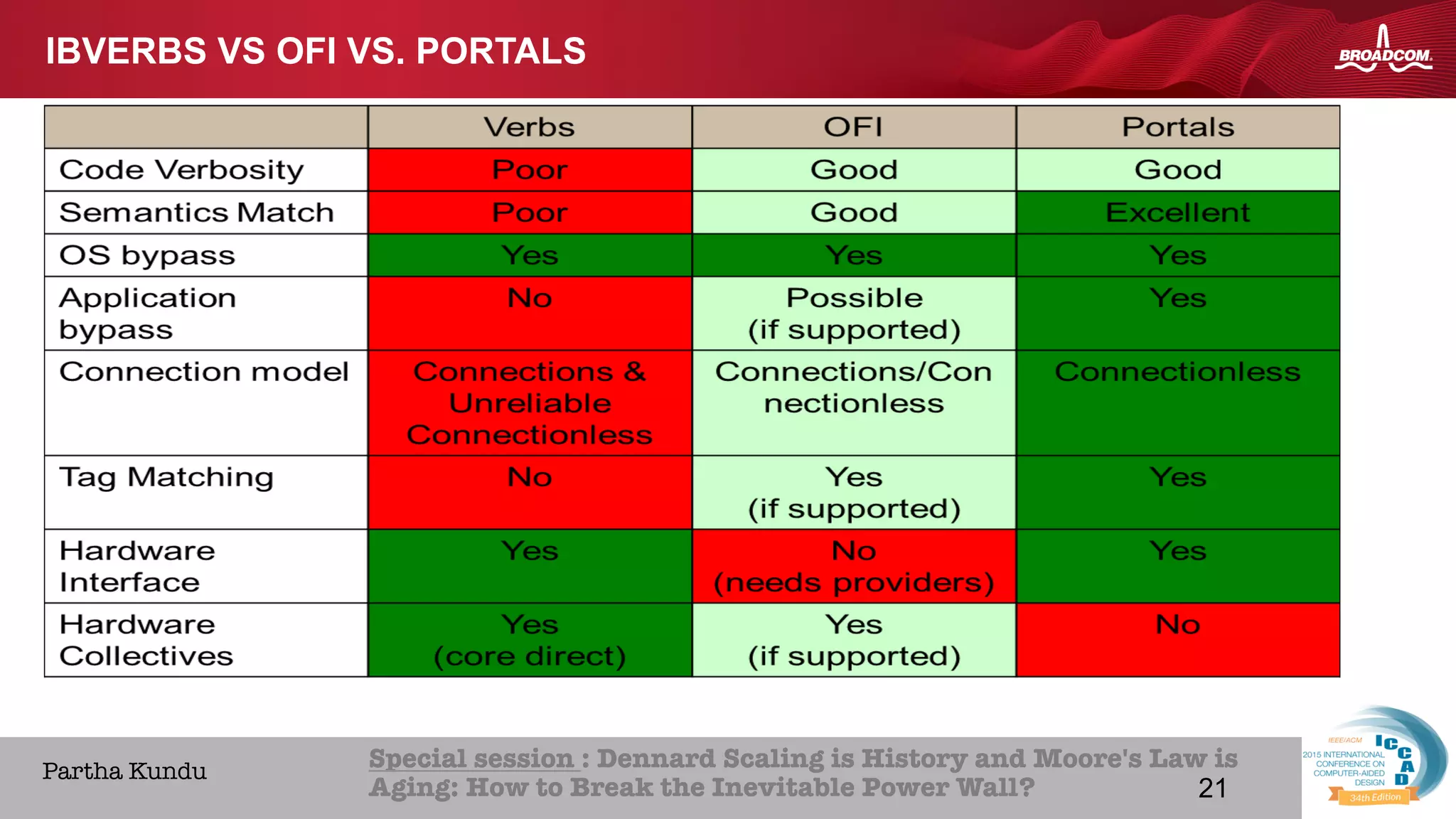

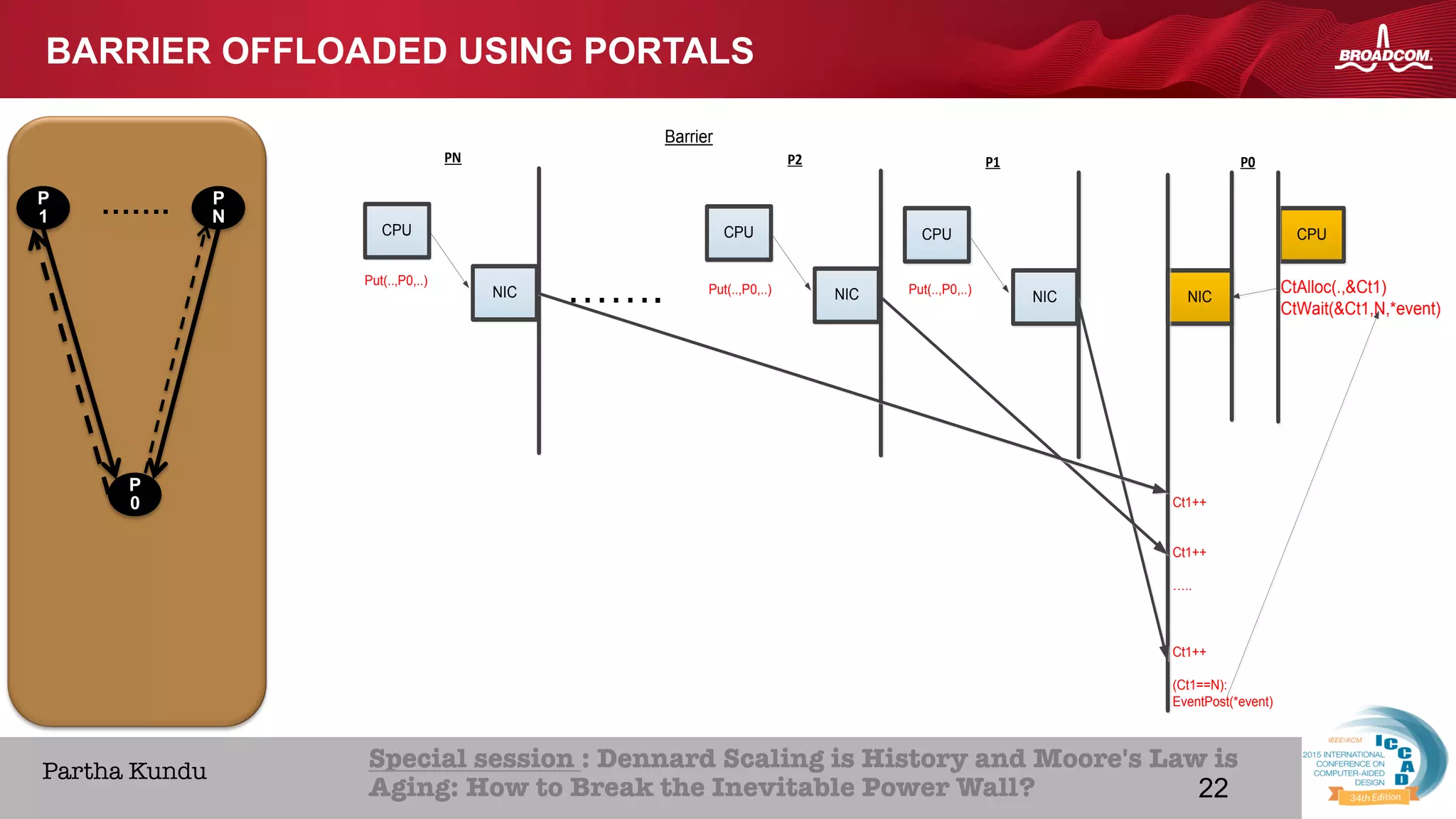

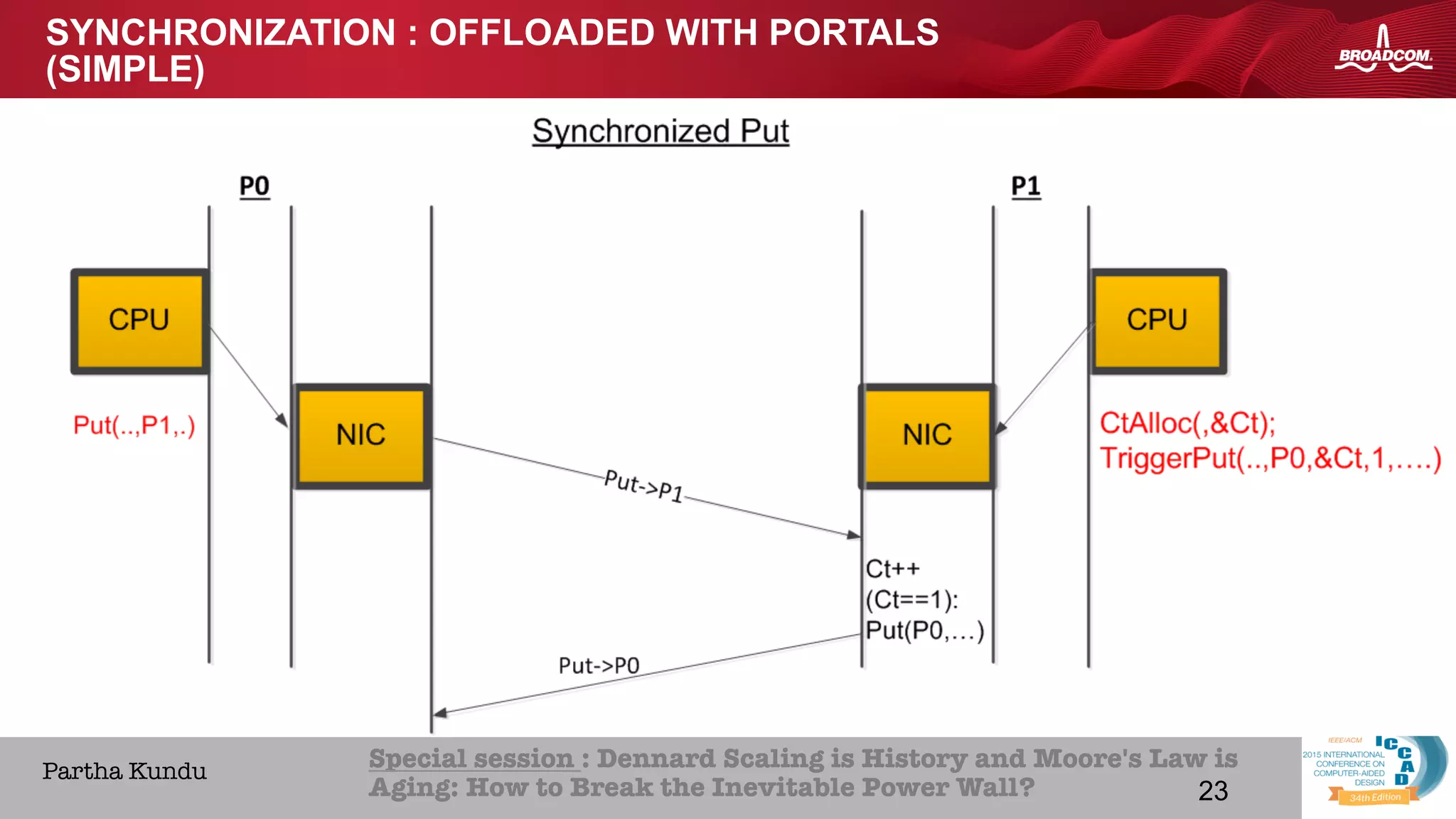

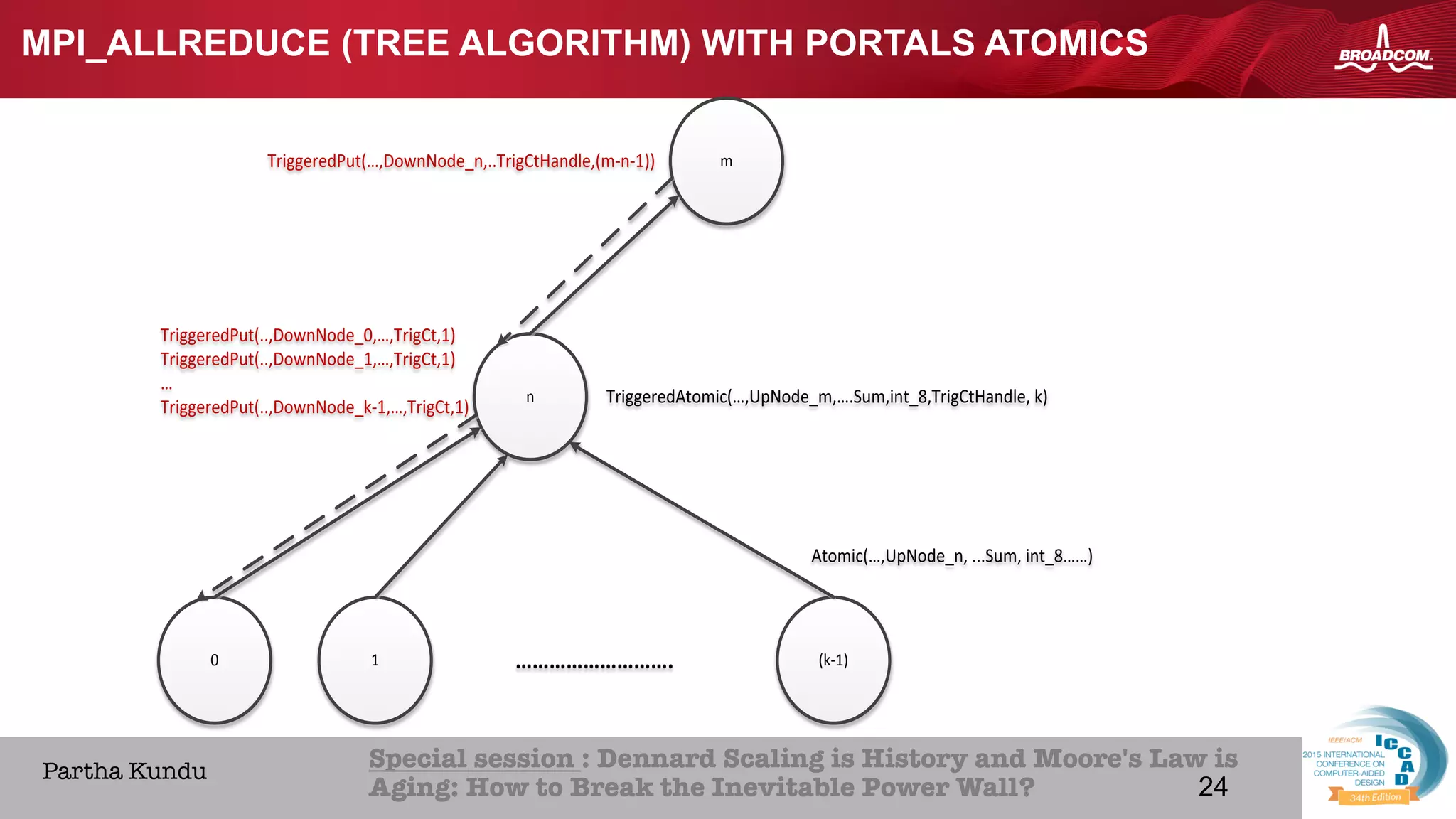

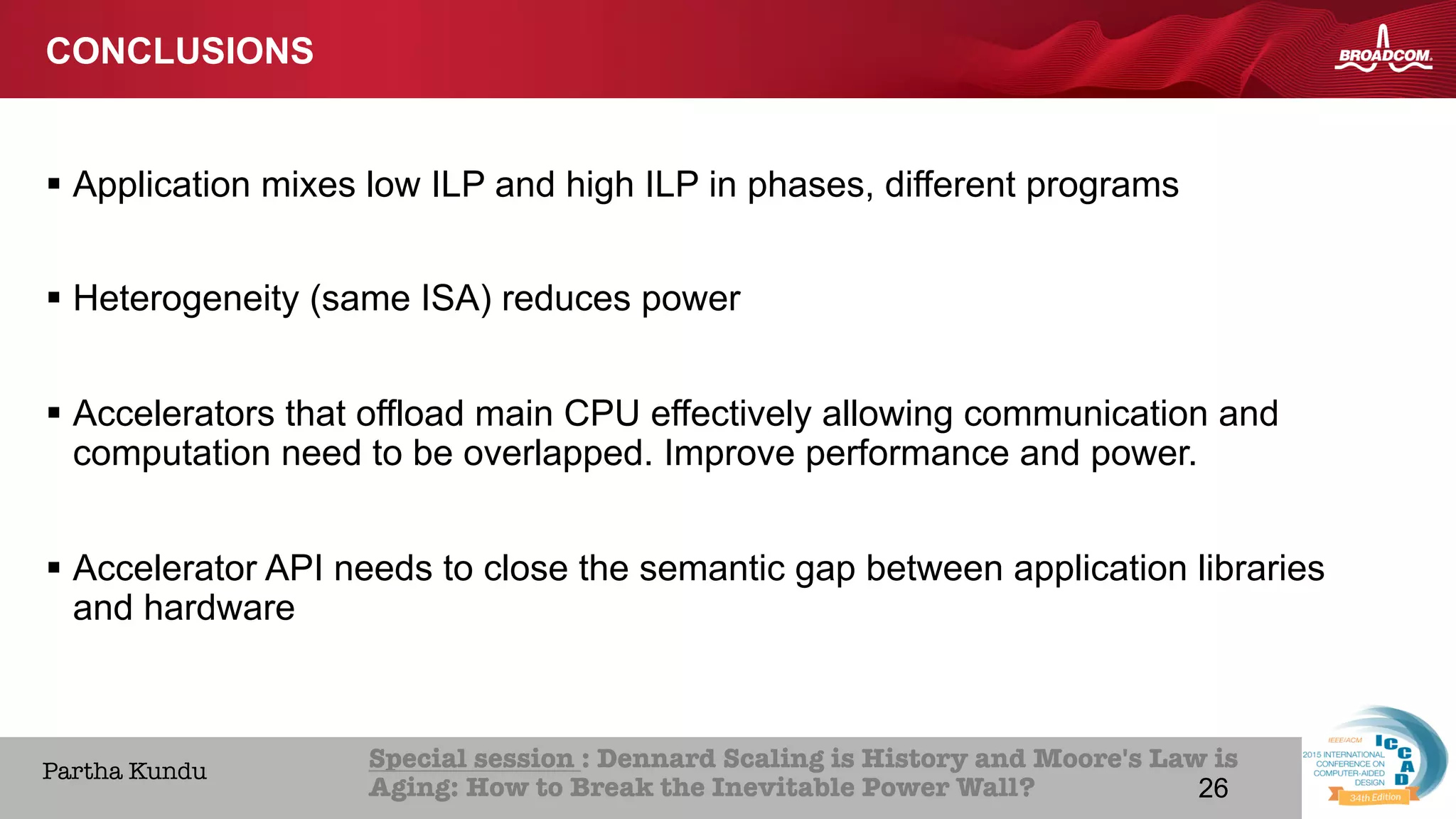

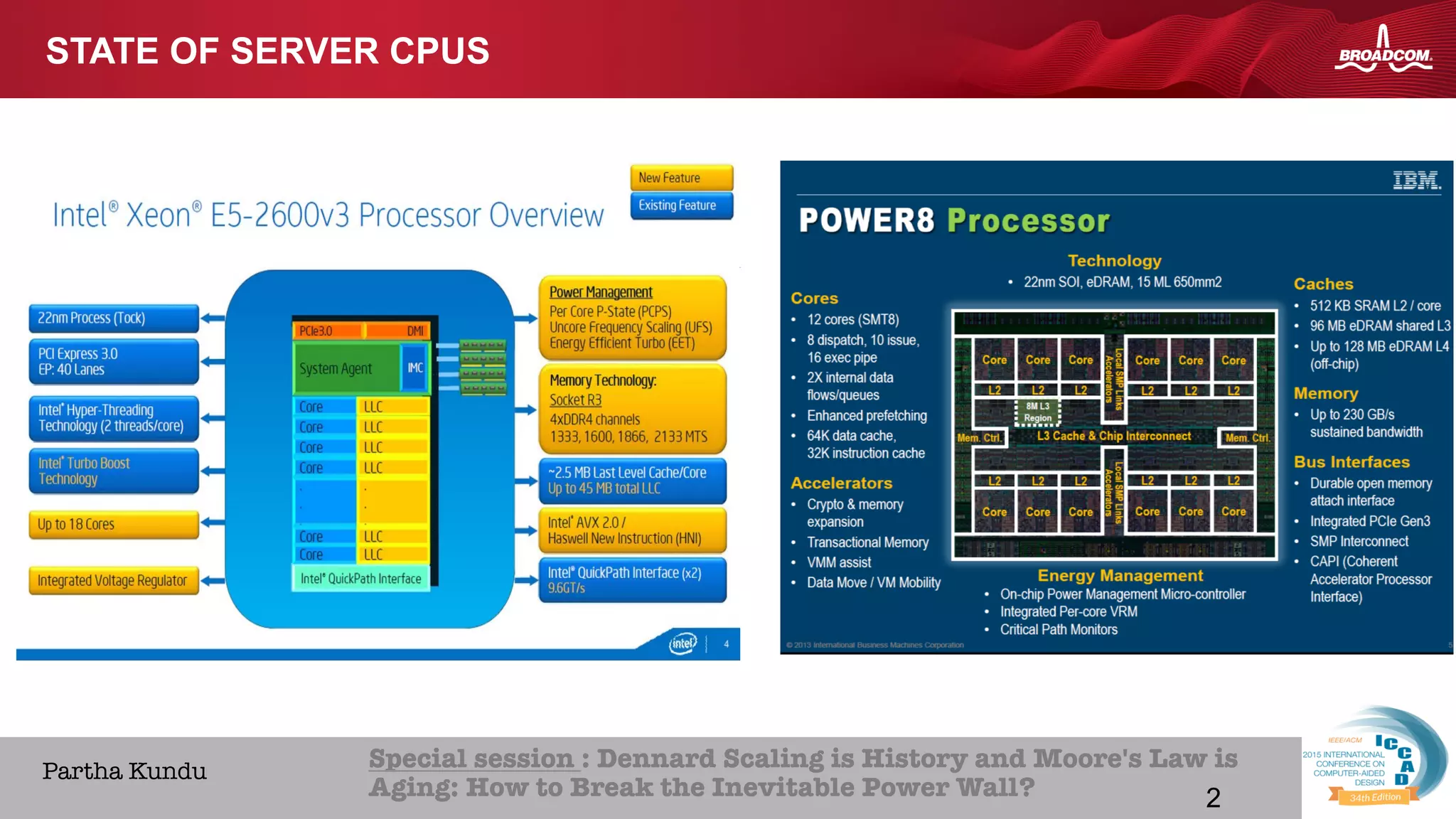

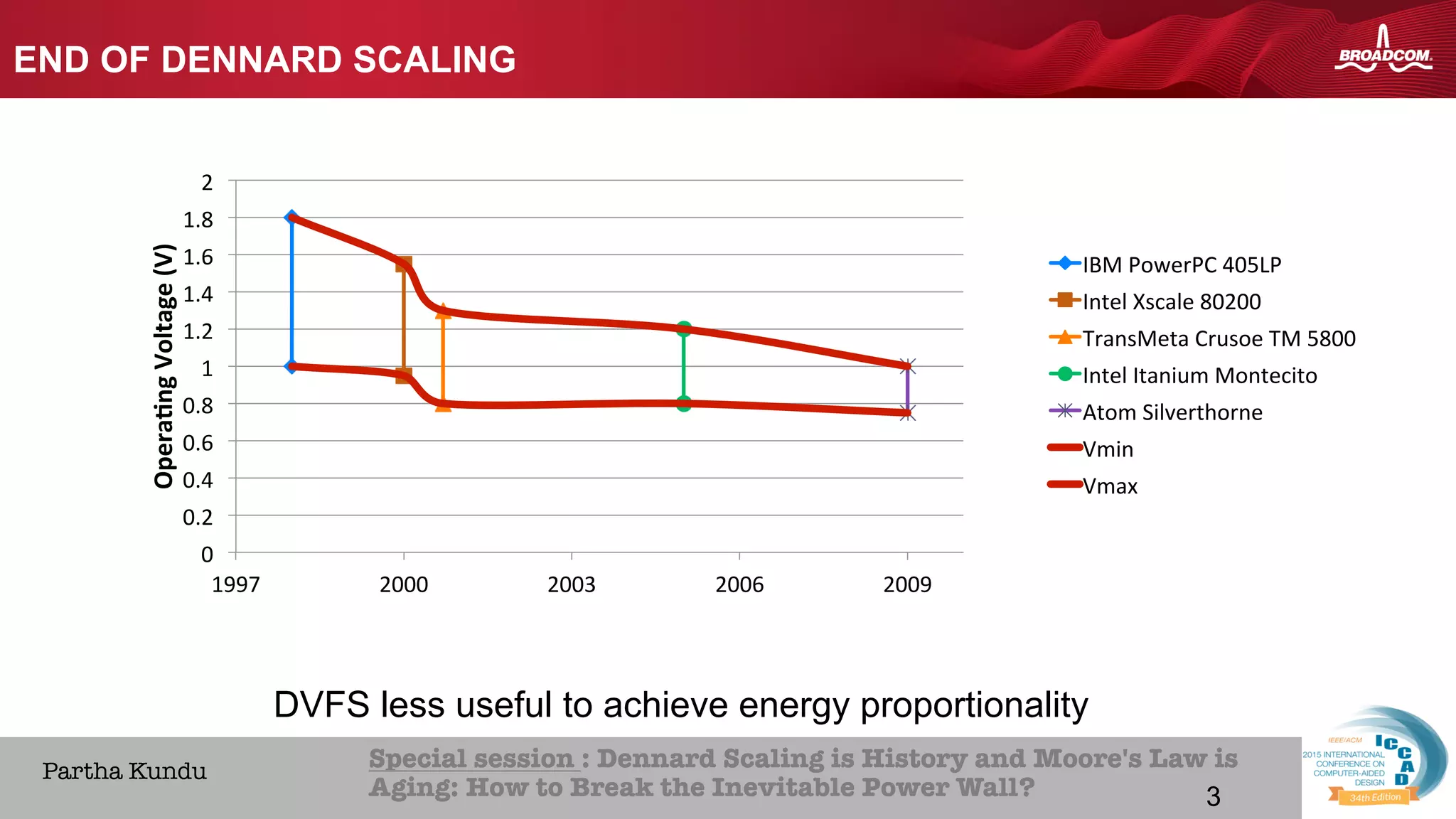

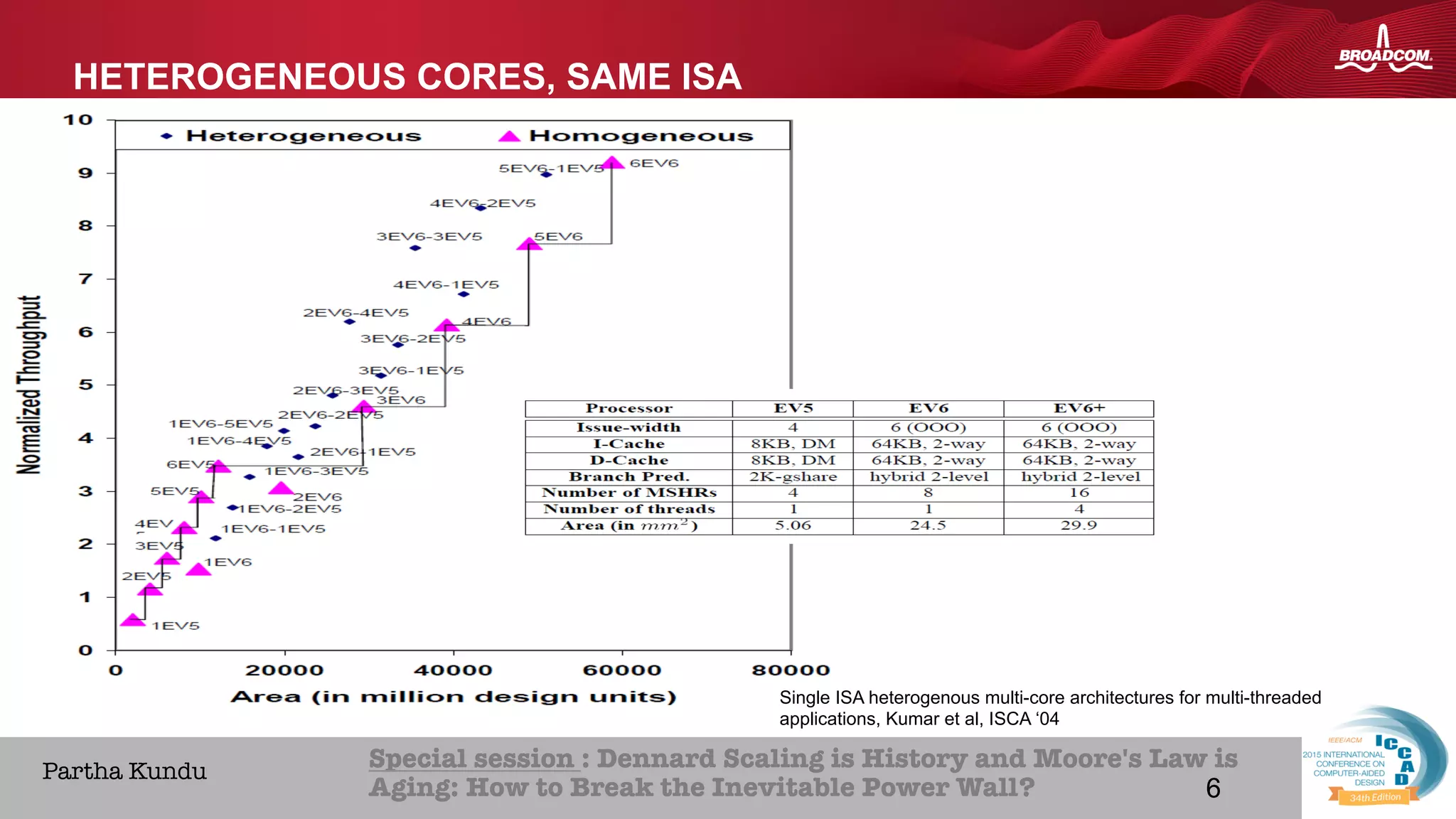

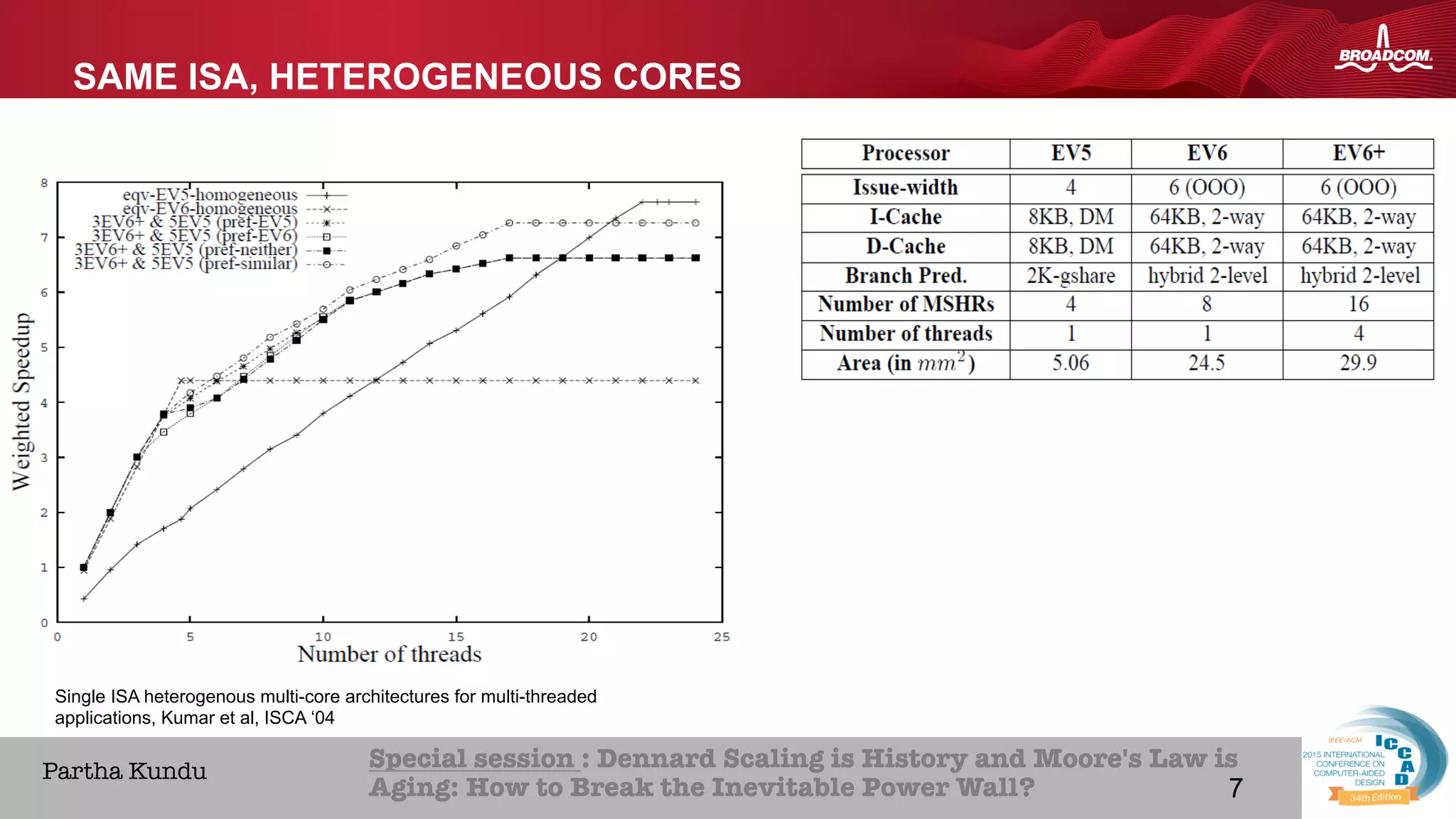

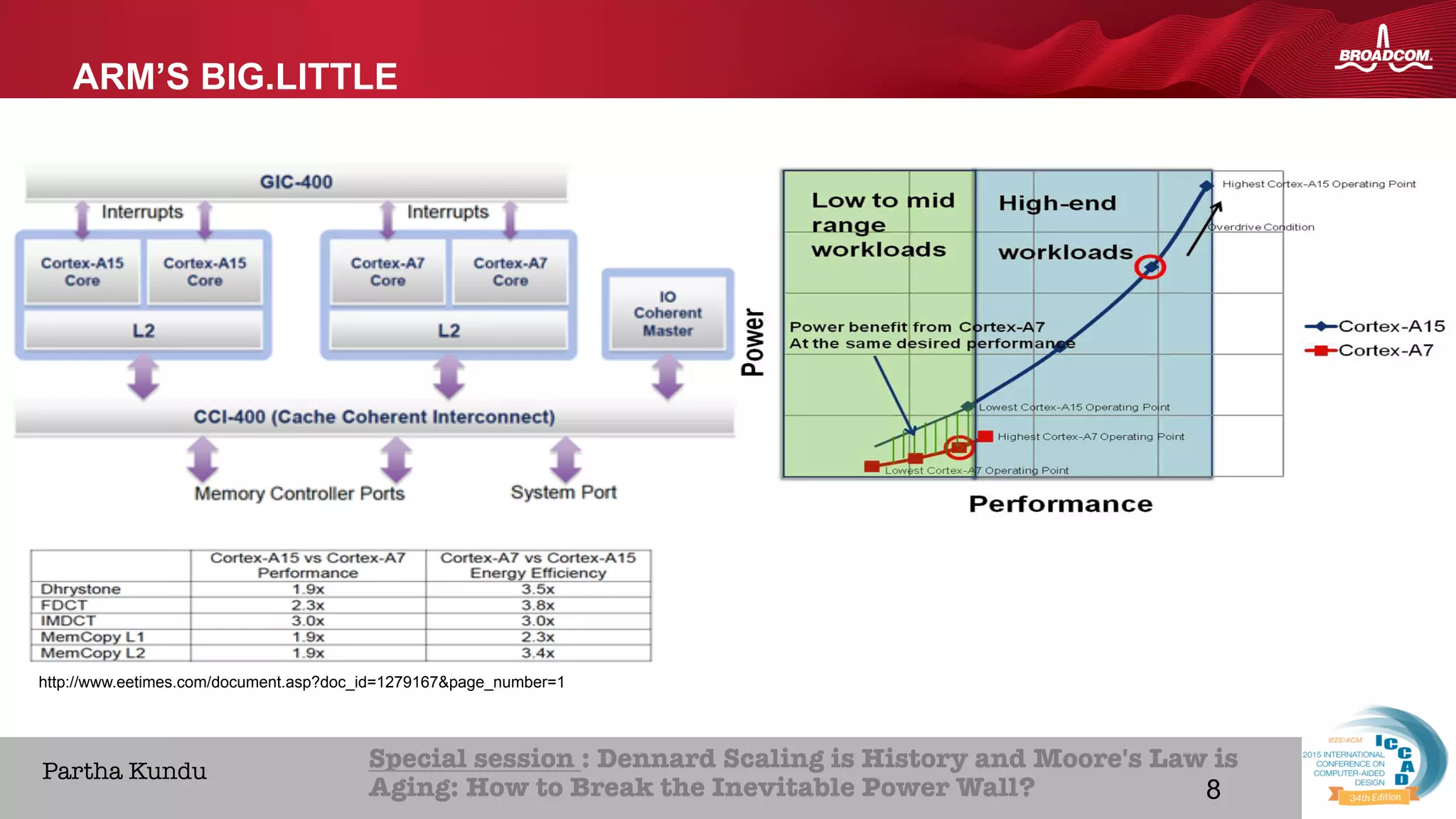

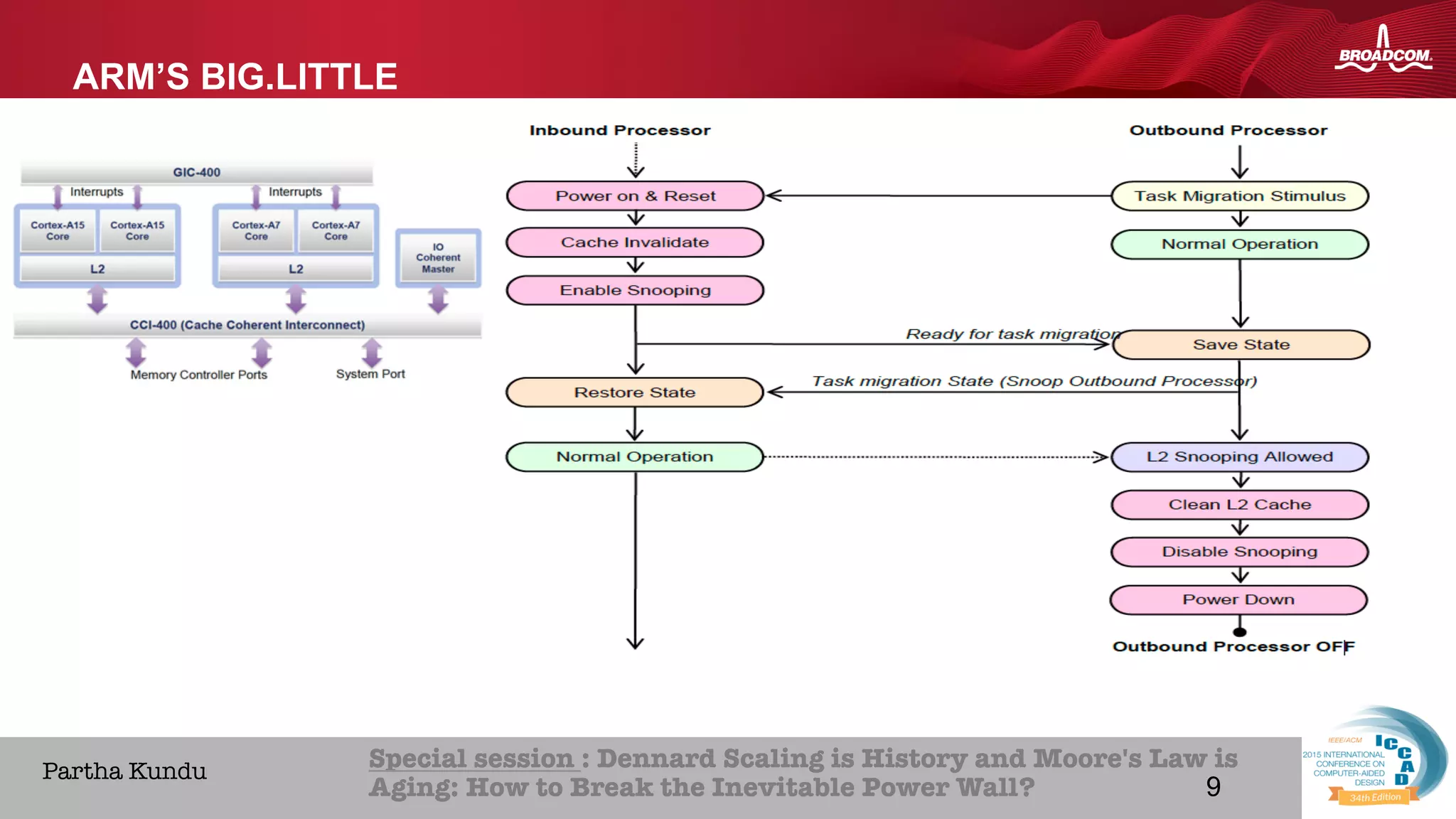

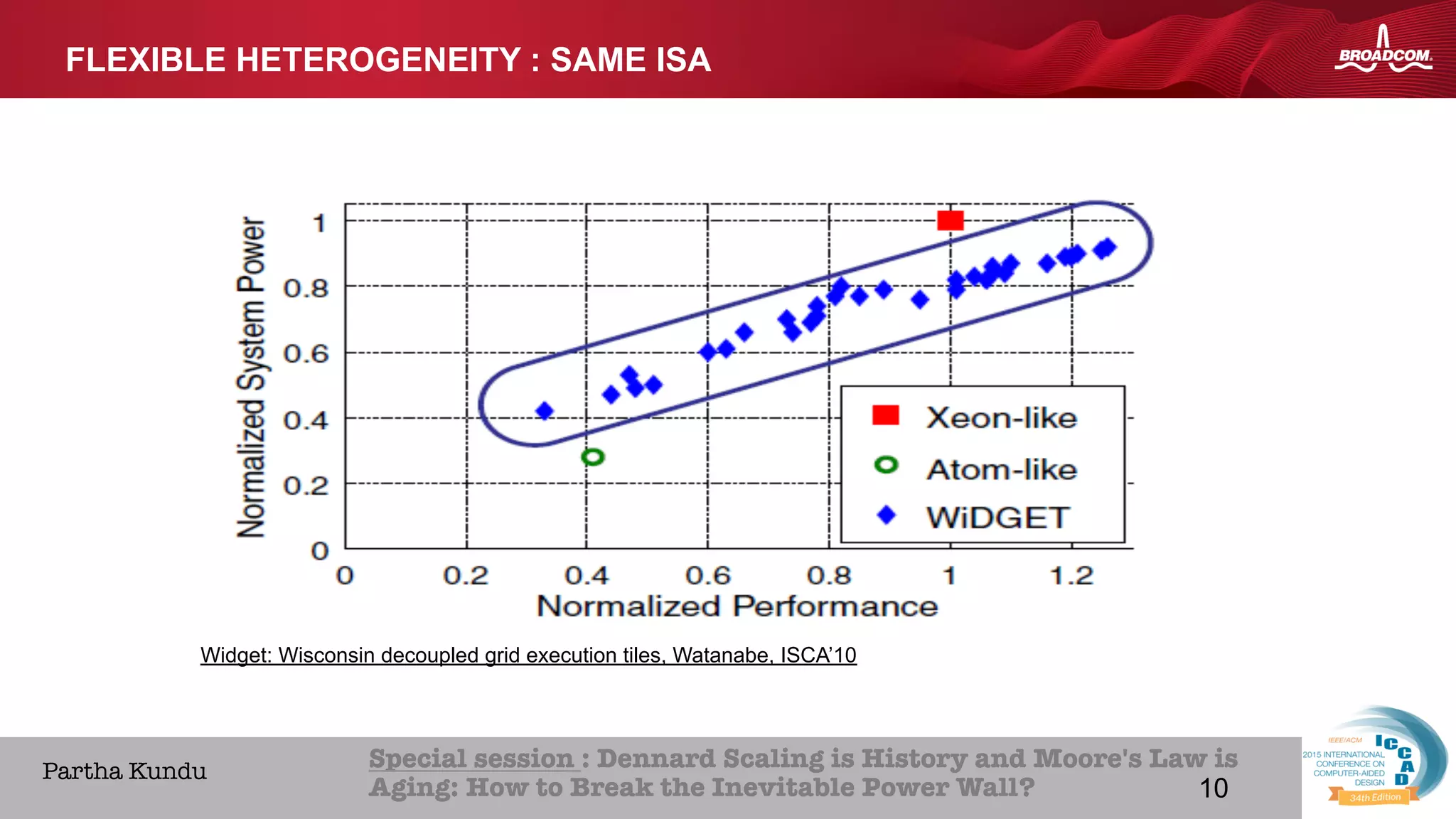

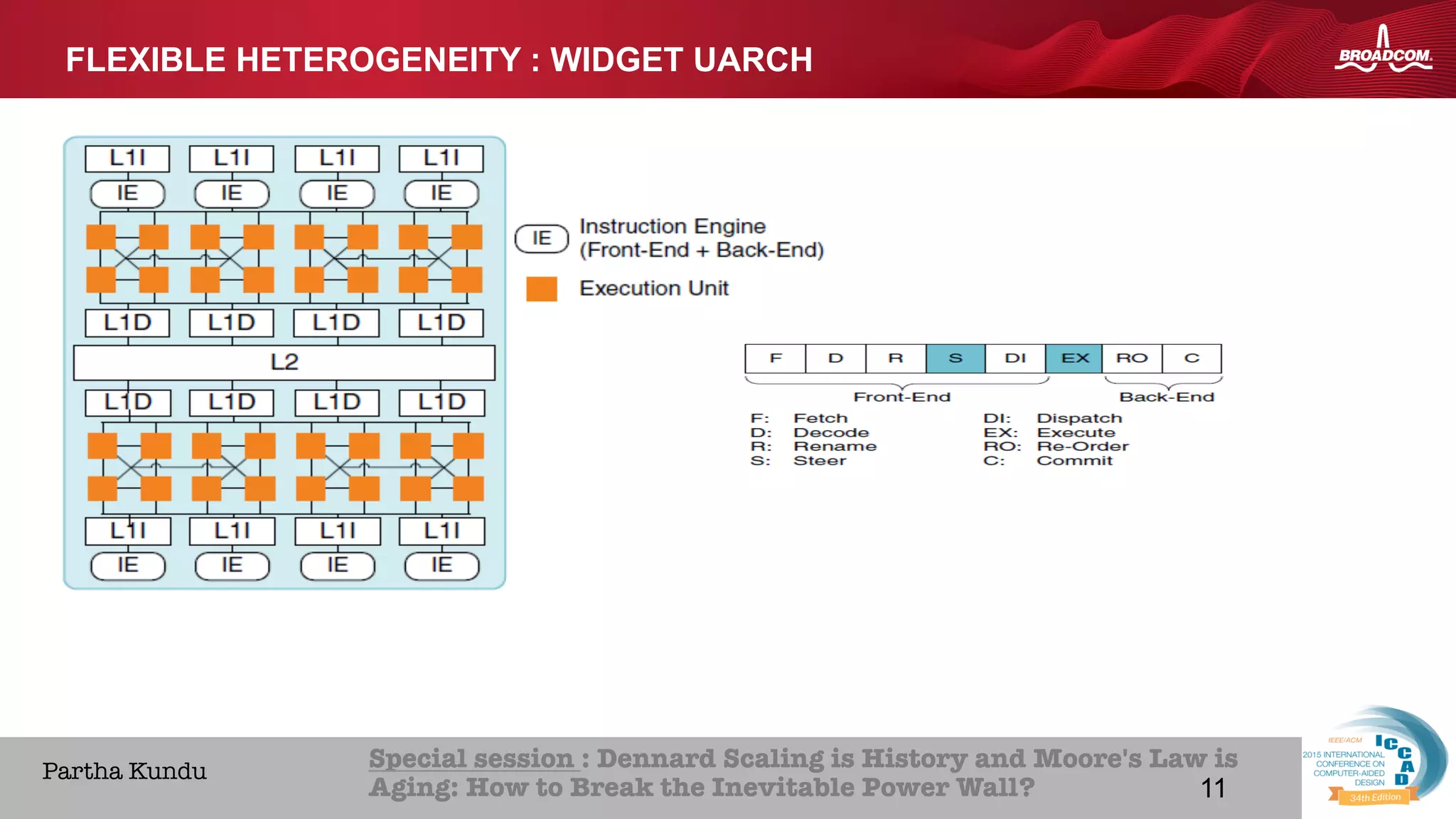

The document discusses strategies for improving processor performance and efficiency as Dennard scaling ends and Moore's law slows. It describes heterogeneous multi-core designs with different core types under a single ISA, as well as adding specialized accelerators to homogeneous cores. It also discusses using heterogeneous cores in systems like ARM's Big.Little design and the Wisconsin Widget architecture. The document notes the continued use of proprietary interconnects in high performance computing and strategies for improving interconnect programming models.

![12Broadcom Proprietary and Confidential. © 2013 Broadcom Corporation. All rights reserved.

HOME ABOUT ICCAD CON

Special session : Dennard Scaling is History and Moore's Law is

Aging: How to Break the Inevitable Power Wall?

Partha Kundu

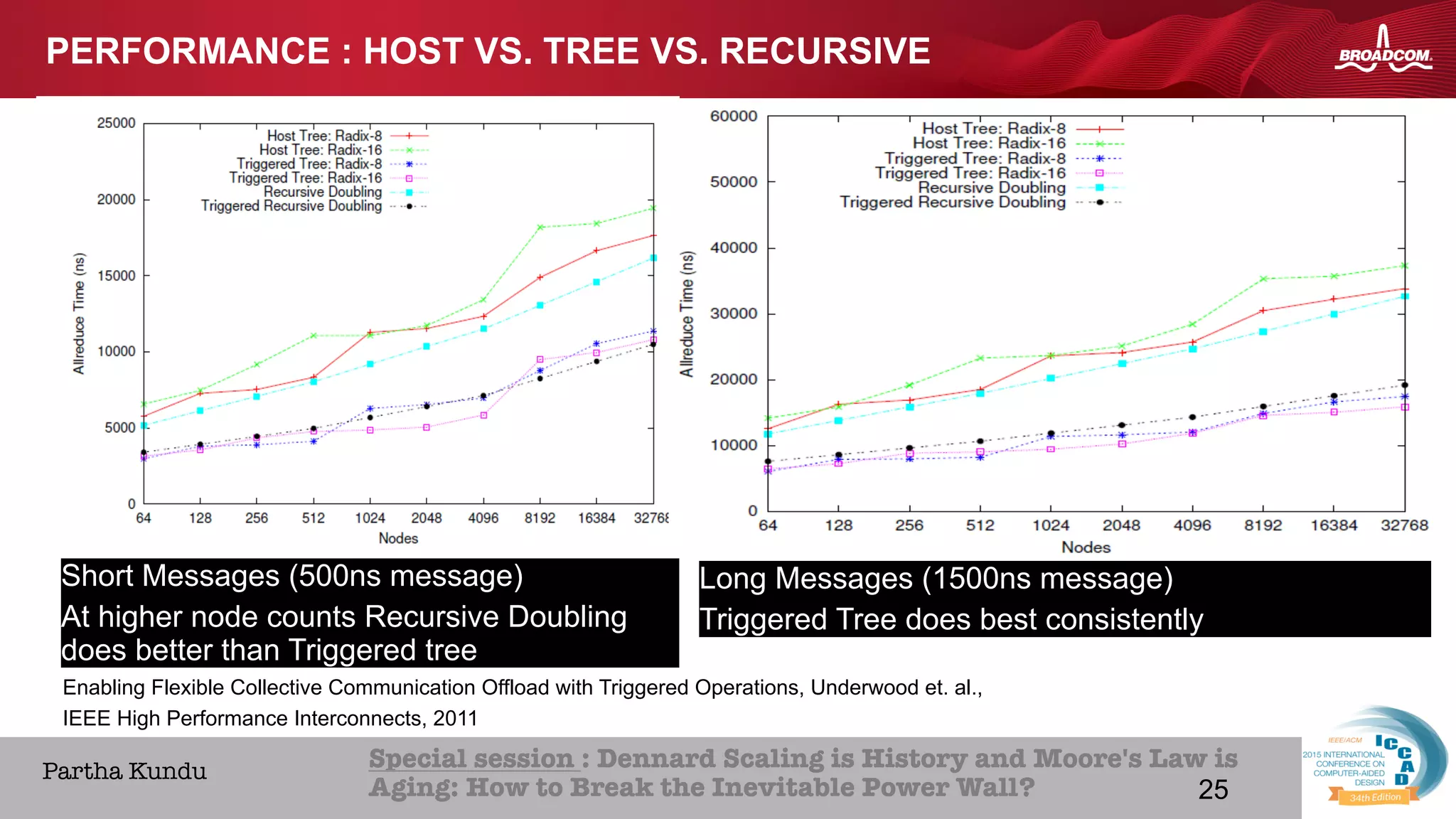

WIDGET: STEERING HEURISTIC

§ Based on dependence-based steering [Palacharla97]

§ Expose independent instr chains

§ Consumer directly behind the producer

§ Stall steering when no empty buffer is found

§ WiDGET: Power-performance goal

§ Emphasize locality & scalability

12

Cluster 0 Cluster 1

Outstanding Ops?

Producer buf

Empty buf

within cluster

Any empty buf Avail behind producer?

Avail behind

either of producers?

Empty buf in

either of clusters

0 1 2

Y Y N N

• Consumer-push operand transfers

– Send steered EU ID to the producer EU

– MulV-cast result to all consumers](https://image.slidesharecdn.com/7ae9cbe2-1f69-44b6-a40f-de9627d3c6e3-160802041643/75/ICCD-talk-12-2048.jpg)