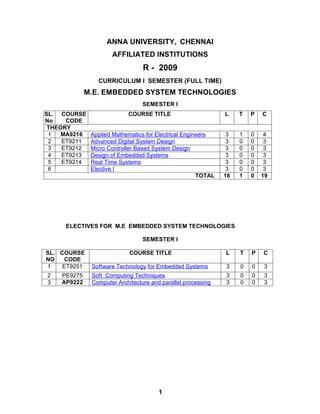

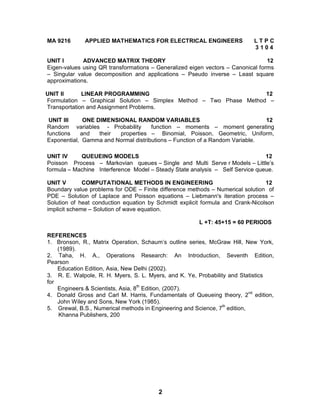

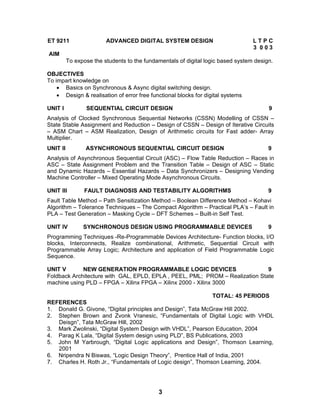

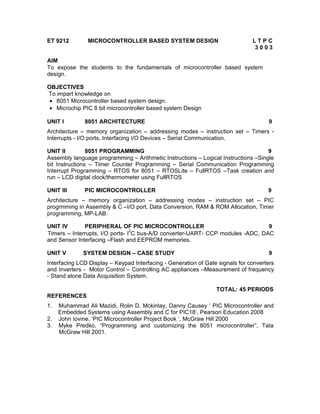

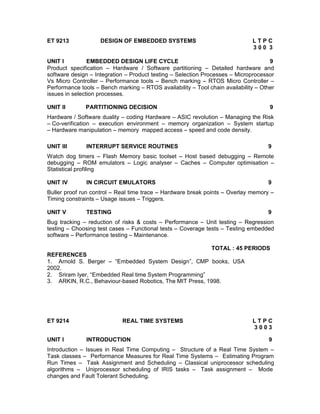

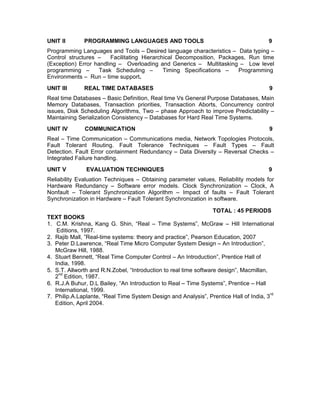

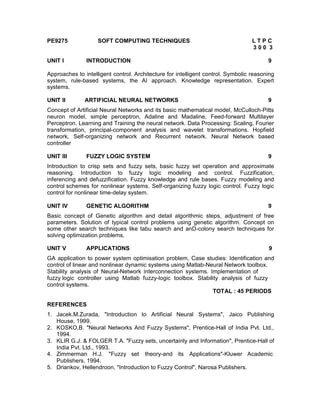

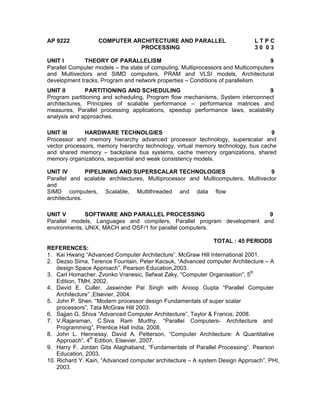

This document provides the curriculum details for the first semester of the M.E. Embedded System Technologies program at Anna University, Chennai. It lists 5 theory courses, including Applied Mathematics for Electrical Engineers, Advanced Digital System Design, Micro Controller Based System Design, Design of Embedded Systems, and Real Time Systems. It also lists 1 elective course that can be chosen from options like Software Technology for Embedded Systems and Soft Computing Techniques. The document then provides course details for the Applied Mathematics course, including topics covered, number of lecture/tutorial hours and references.