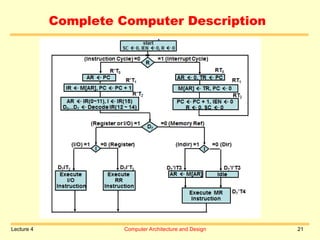

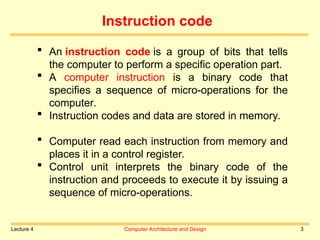

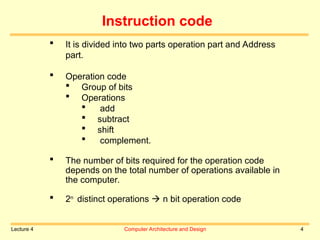

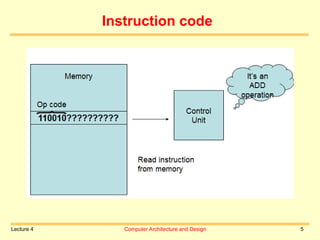

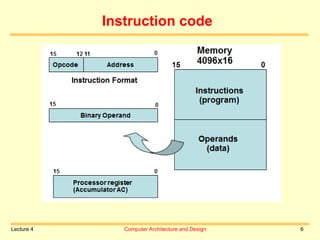

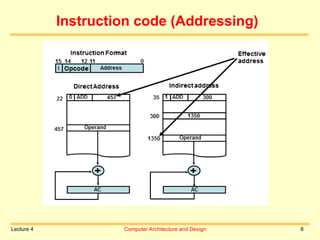

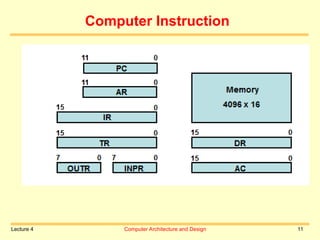

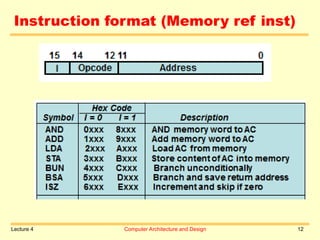

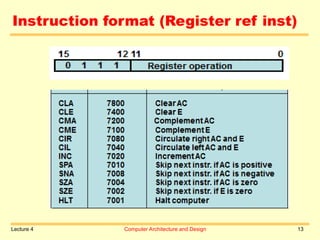

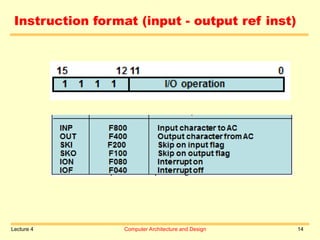

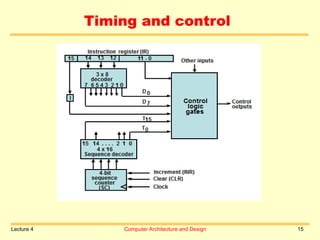

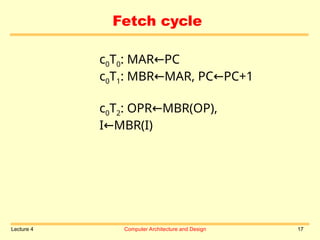

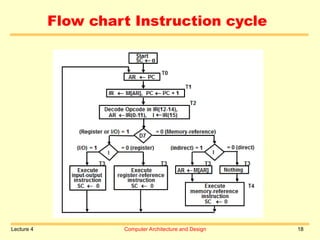

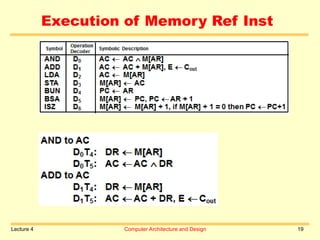

The document discusses computer architecture, focusing on instruction codes and their components, which include the operation part and address part. It explains different addressing modes (immediate, direct, indirect) and details the instruction cycle phases: fetch, execute, indirect, and interrupt. Additionally, it highlights the importance of the control unit, instruction register, and processor registers in executing instructions stored in memory.

![Lecture 4 Computer Architecture and Design 20

Execution of Branch and save return

Address (BSA)

M[AR] PC, PC

AR+1](https://image.slidesharecdn.com/lecture4-241030150148-8c6aaefb/85/Computer-Architecture-notes-by-Beenish-Lecture-4-ppt-20-320.jpg)