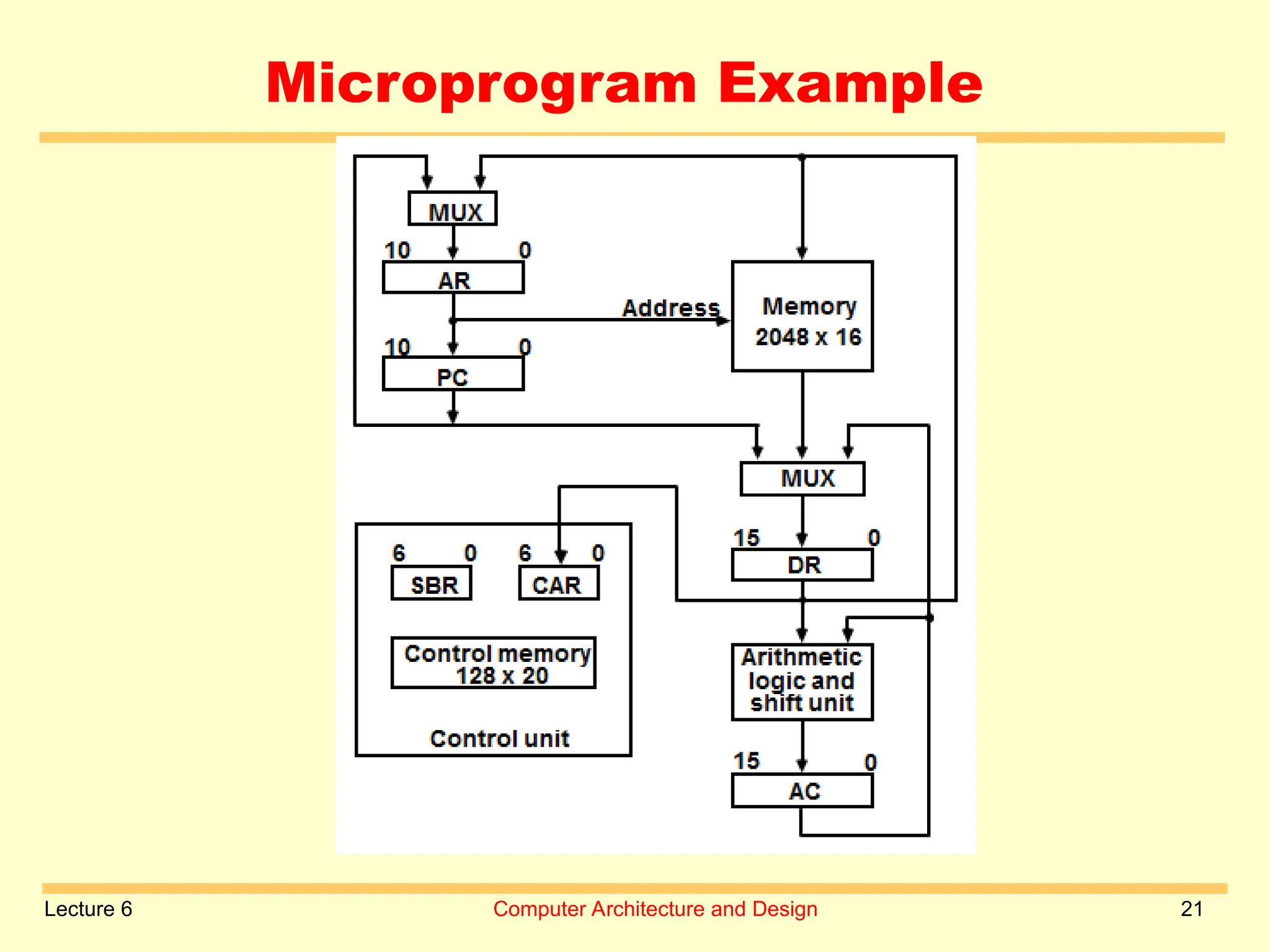

The document outlines the differences between hardwired and microprogrammed control units in computer architecture. Hardwired control units are faster but less flexible and more complex in design, whereas microprogrammed control units are slower but more flexible, allowing for complex instruction handling. It also covers key components like control memory, instruction registers, and the process of mapping instructions to microprogram routines.