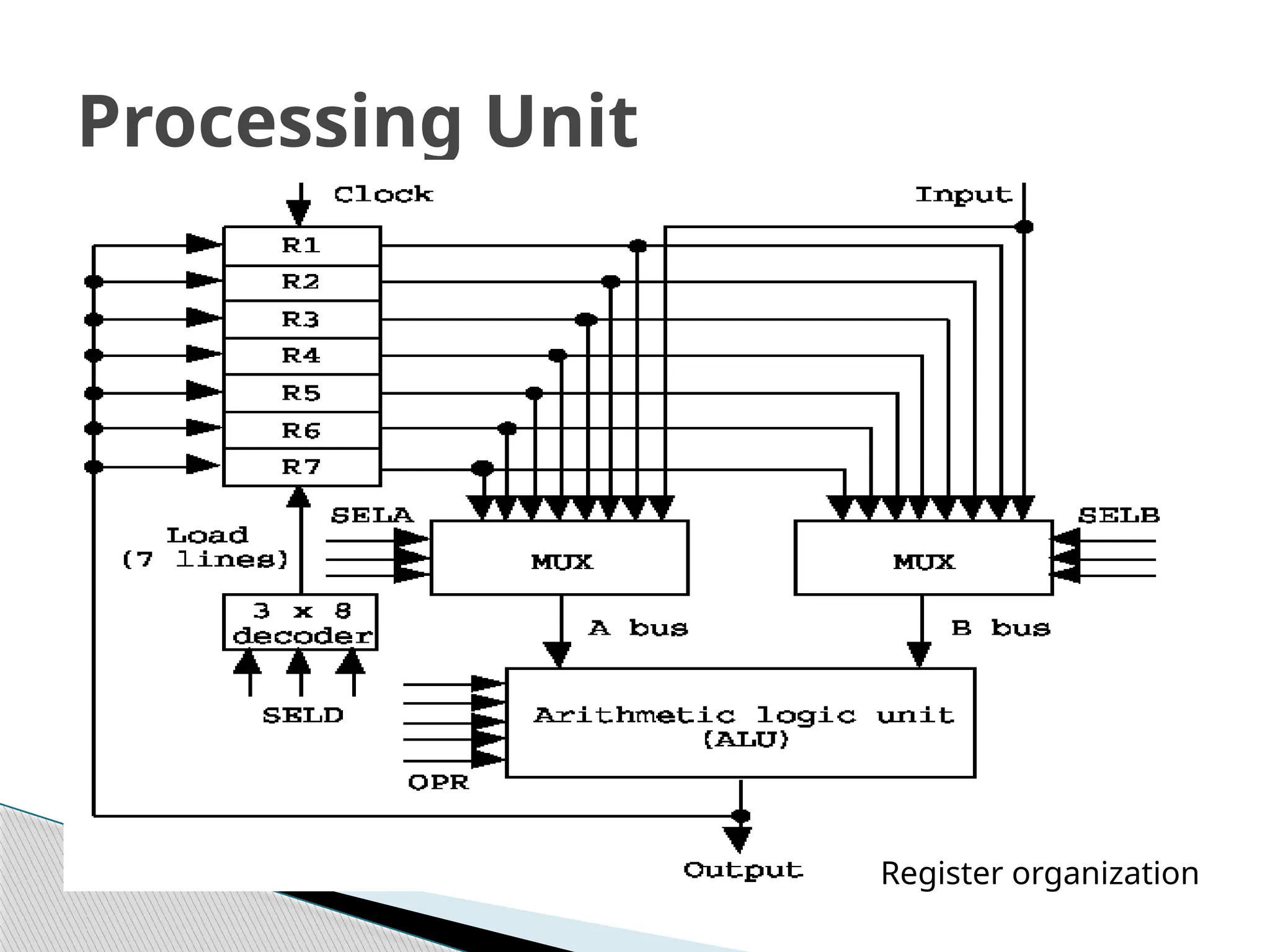

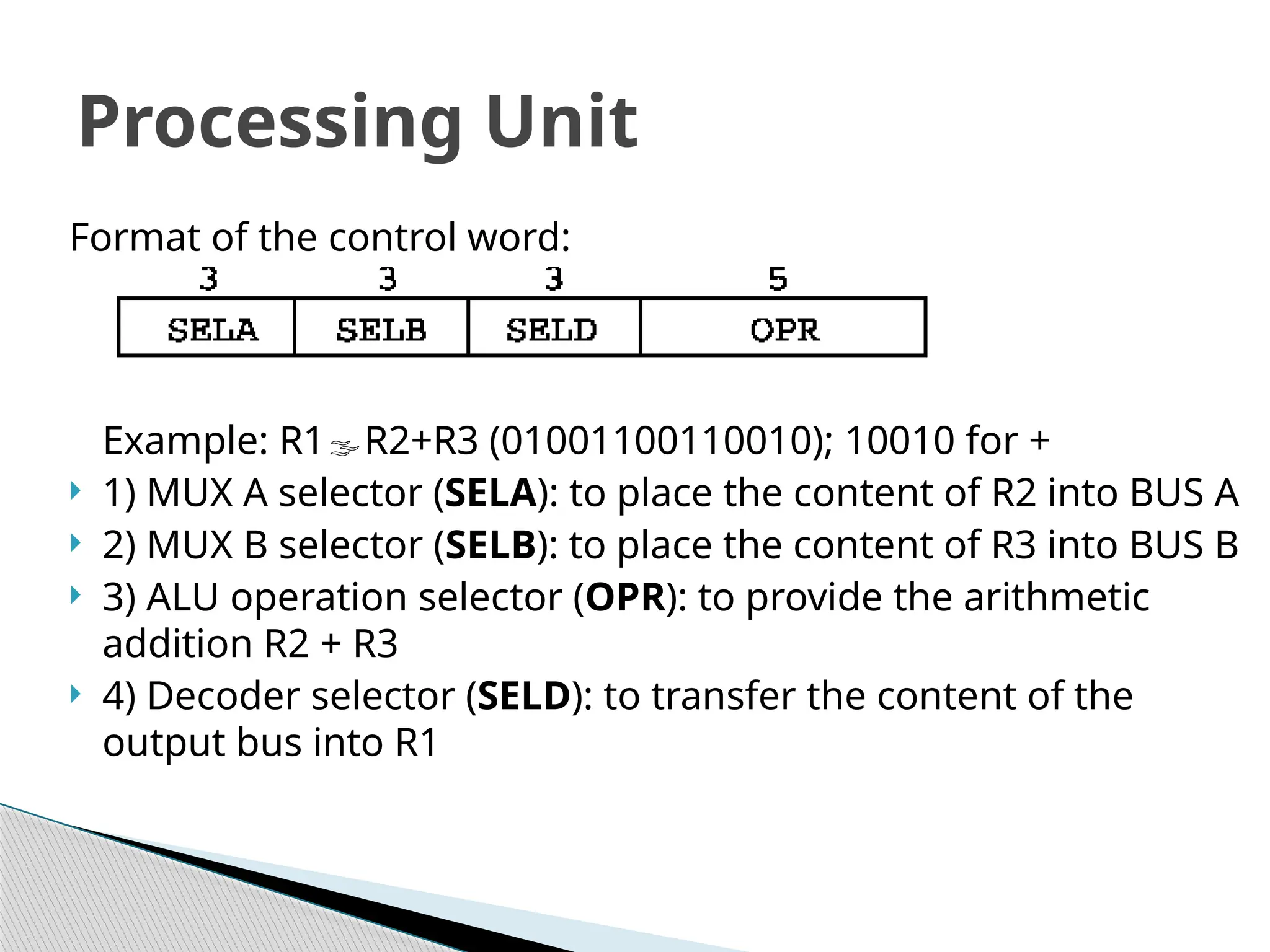

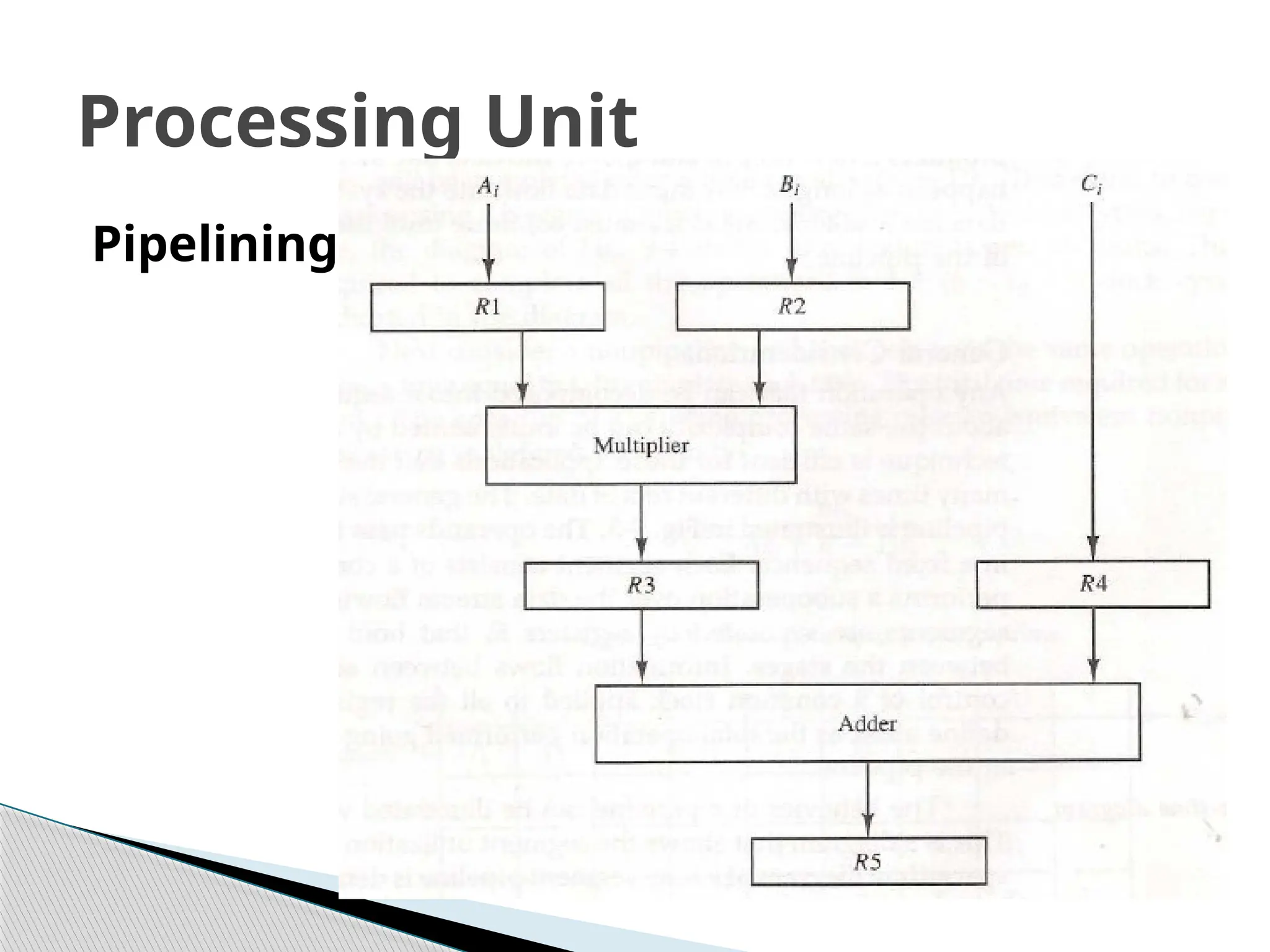

The document details the functions and organization of the central processing unit (CPU) in computer architecture, describing its components like the arithmetic logic unit (ALU), control unit, and register set. It explains how the CPU executes instructions through fetching, decoding, and executing operations, as well as discussing pipelining techniques for improved efficiency. Additionally, it includes an example of multi-step instruction processing and highlights the benefits of using a pipeline with segmented task execution.