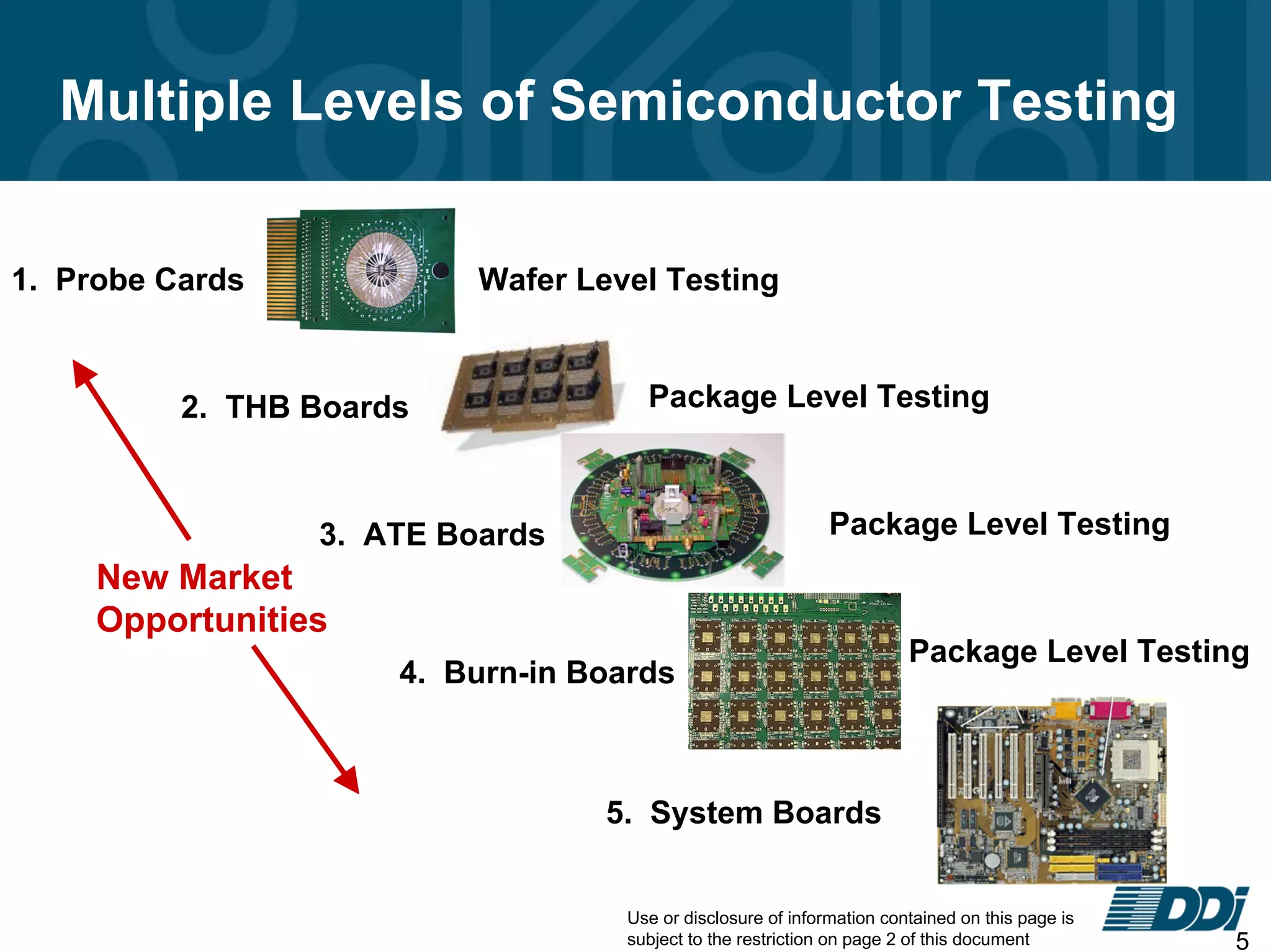

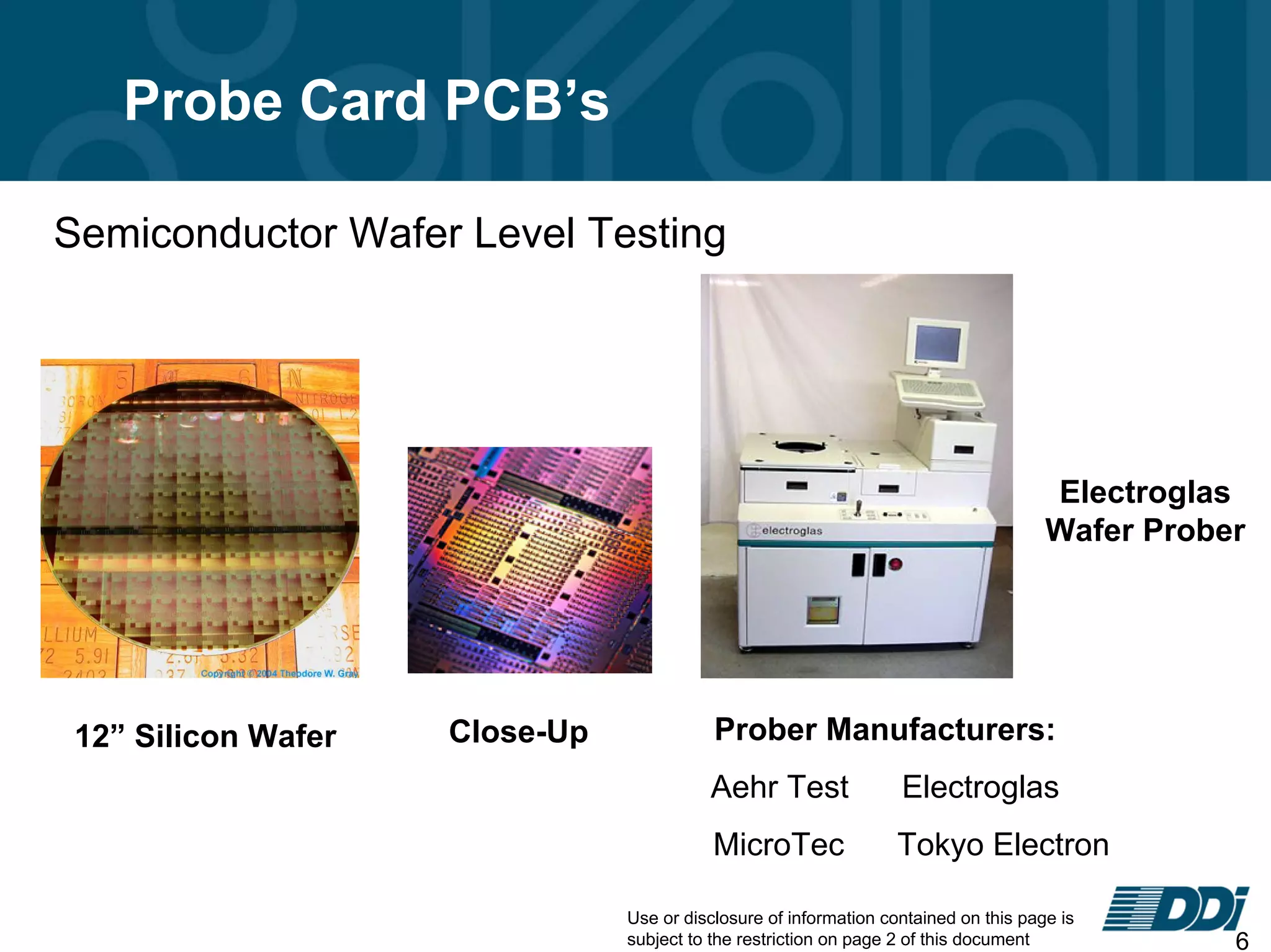

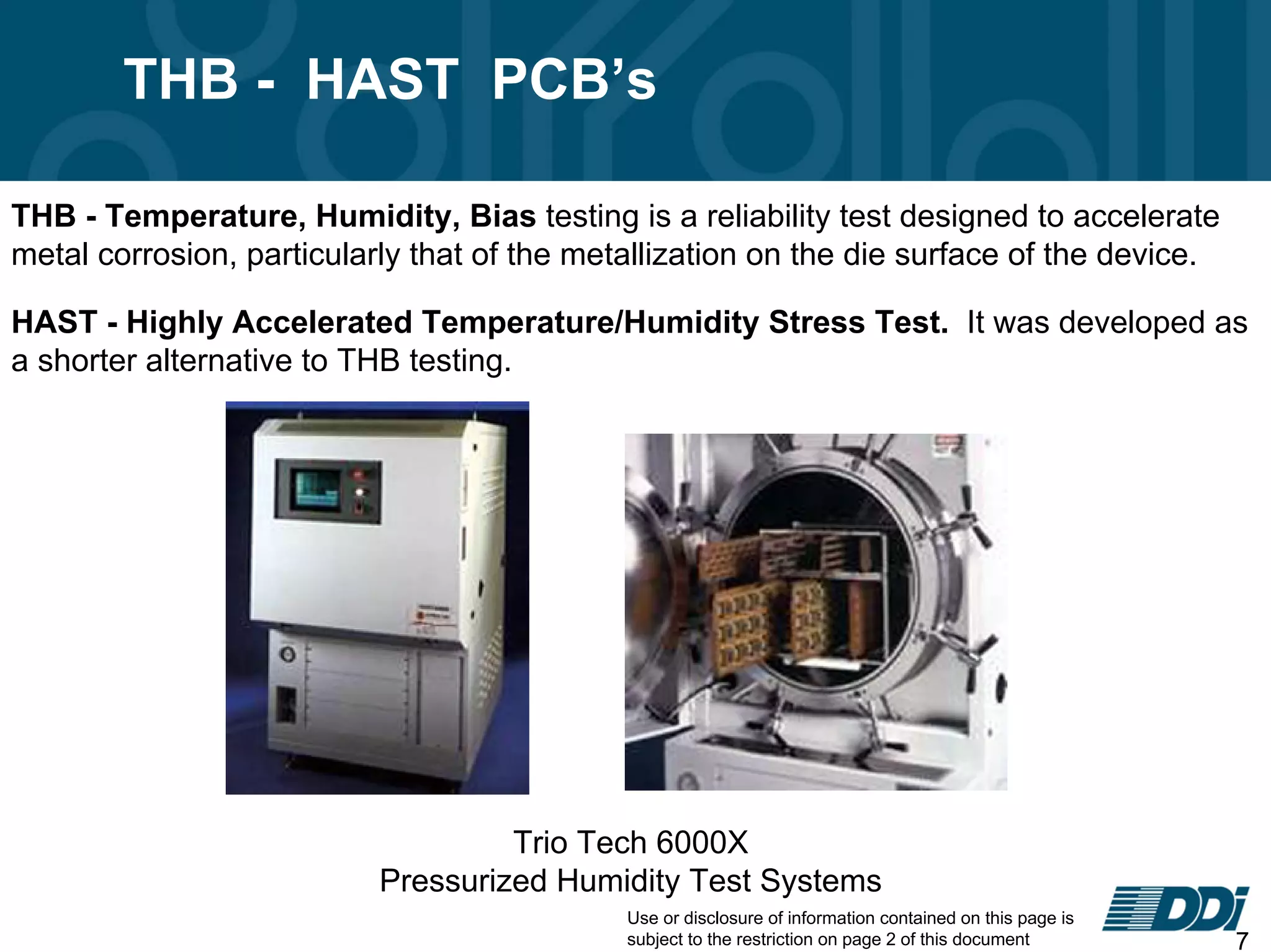

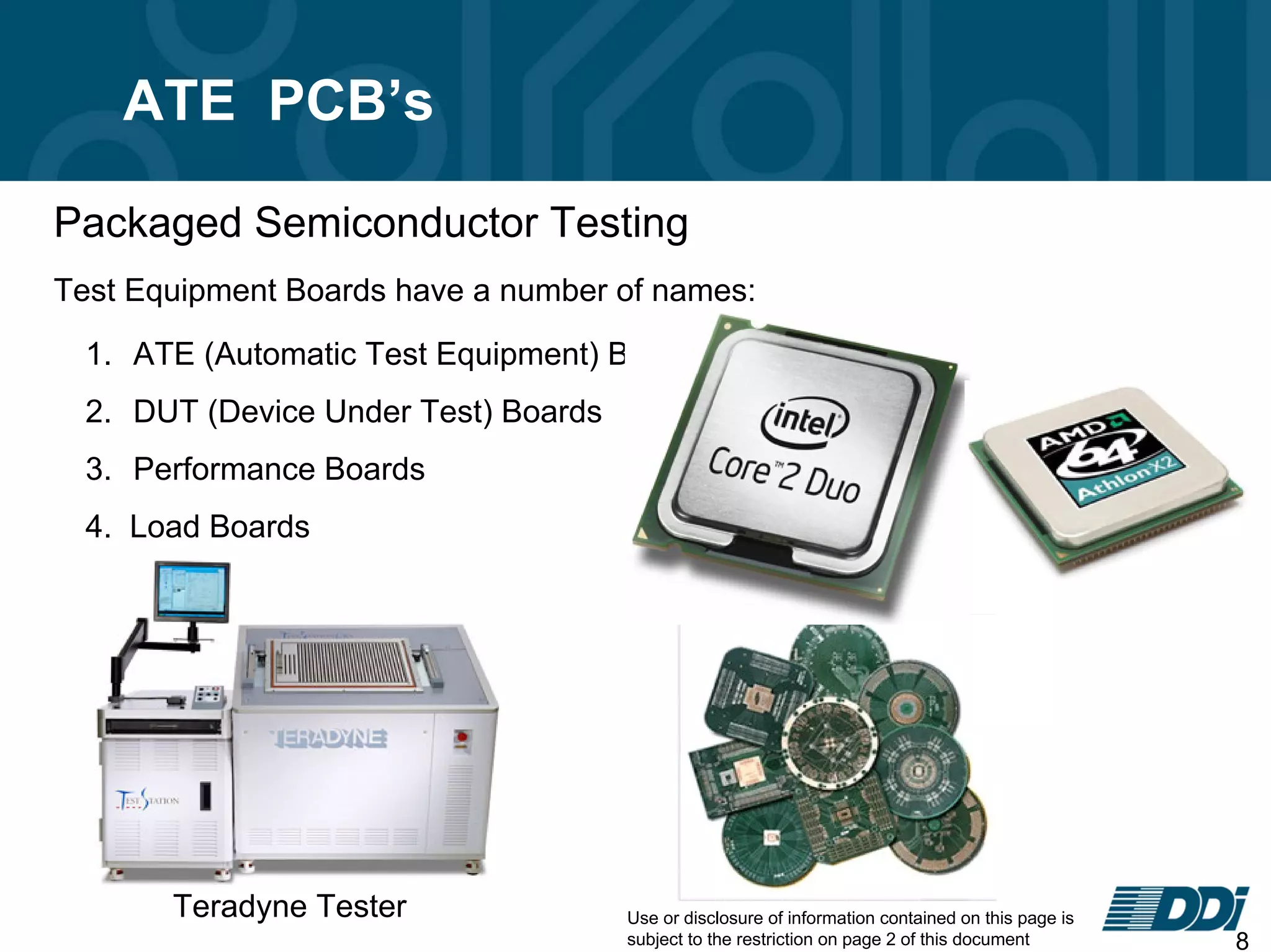

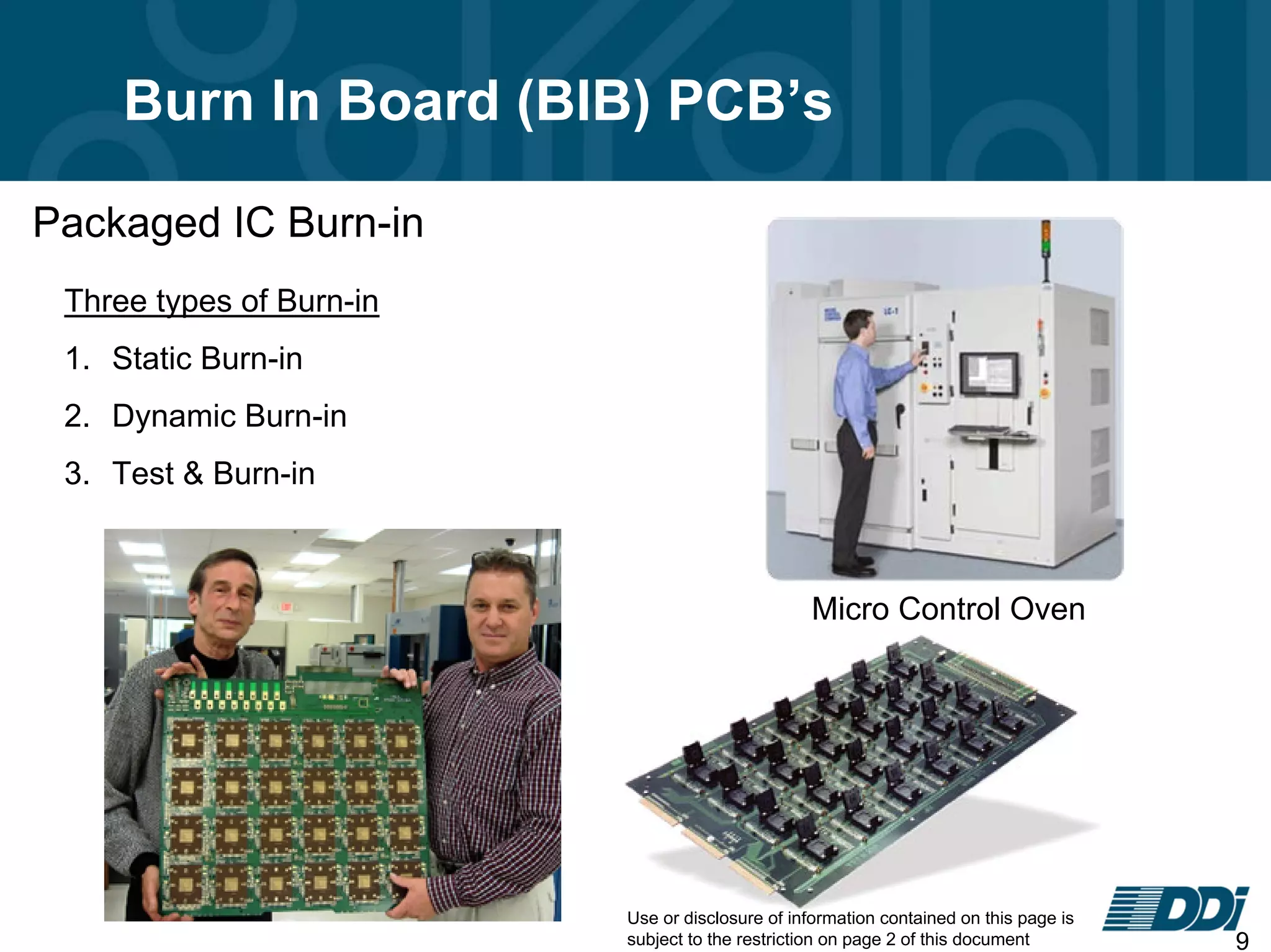

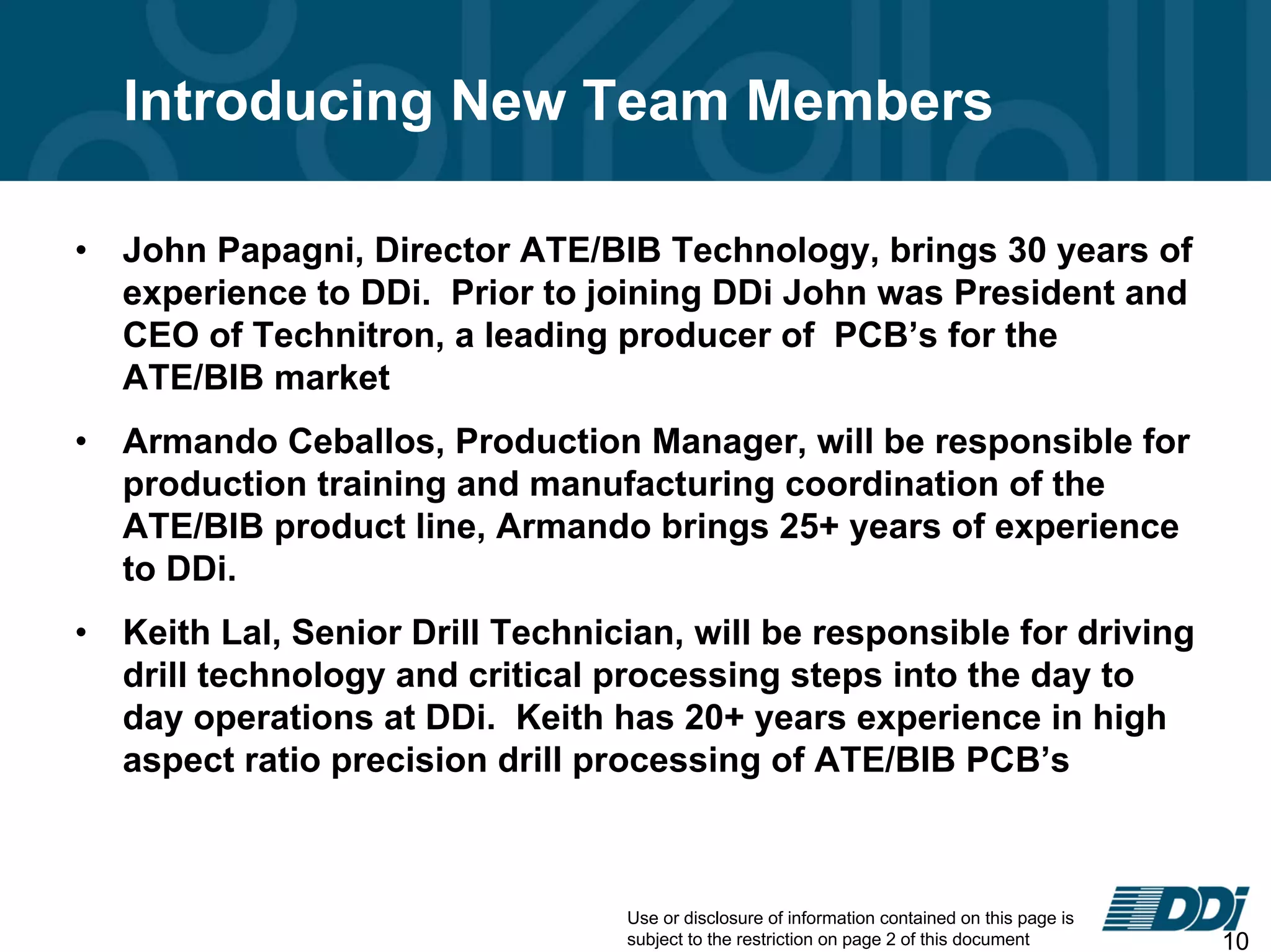

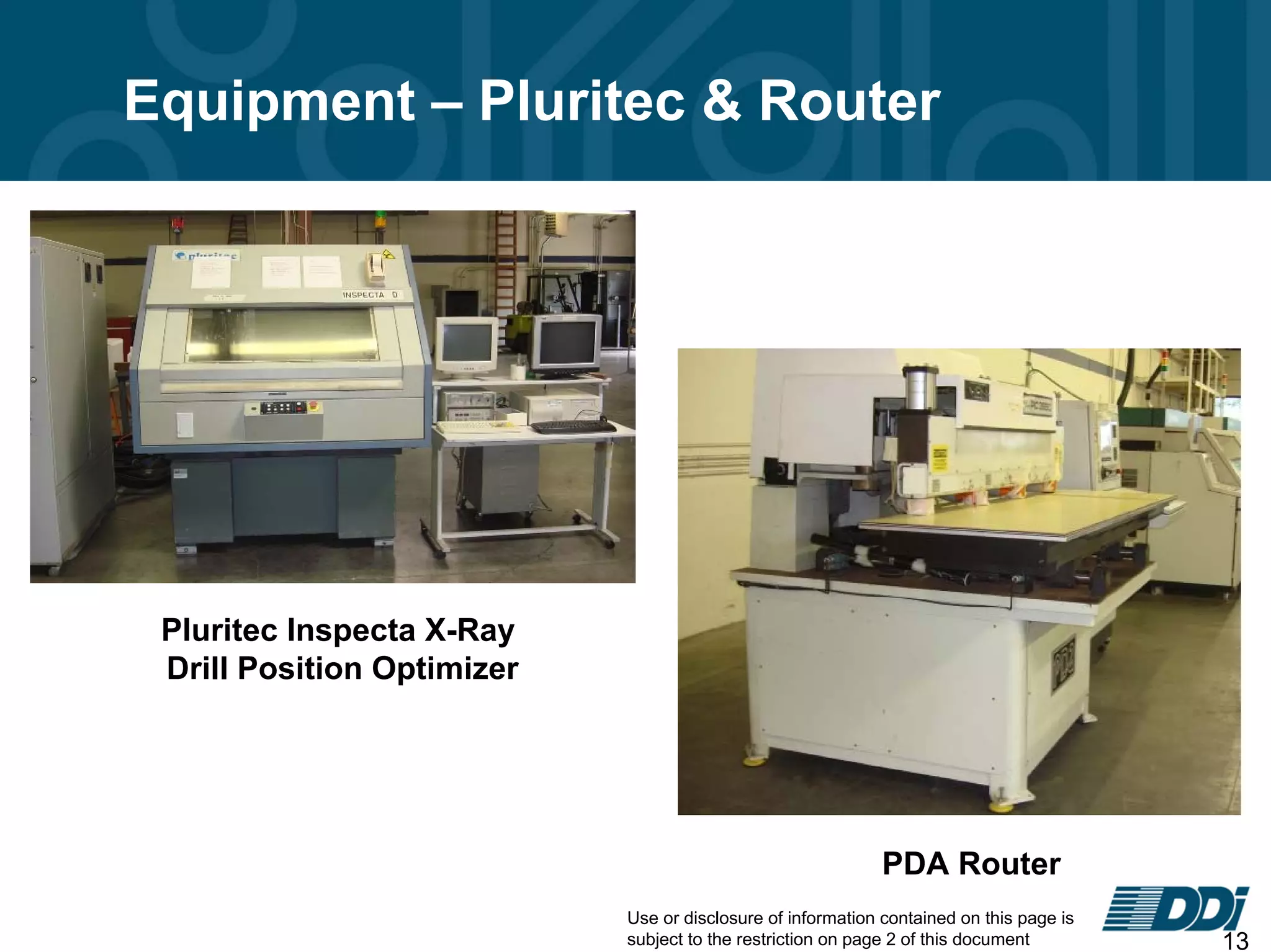

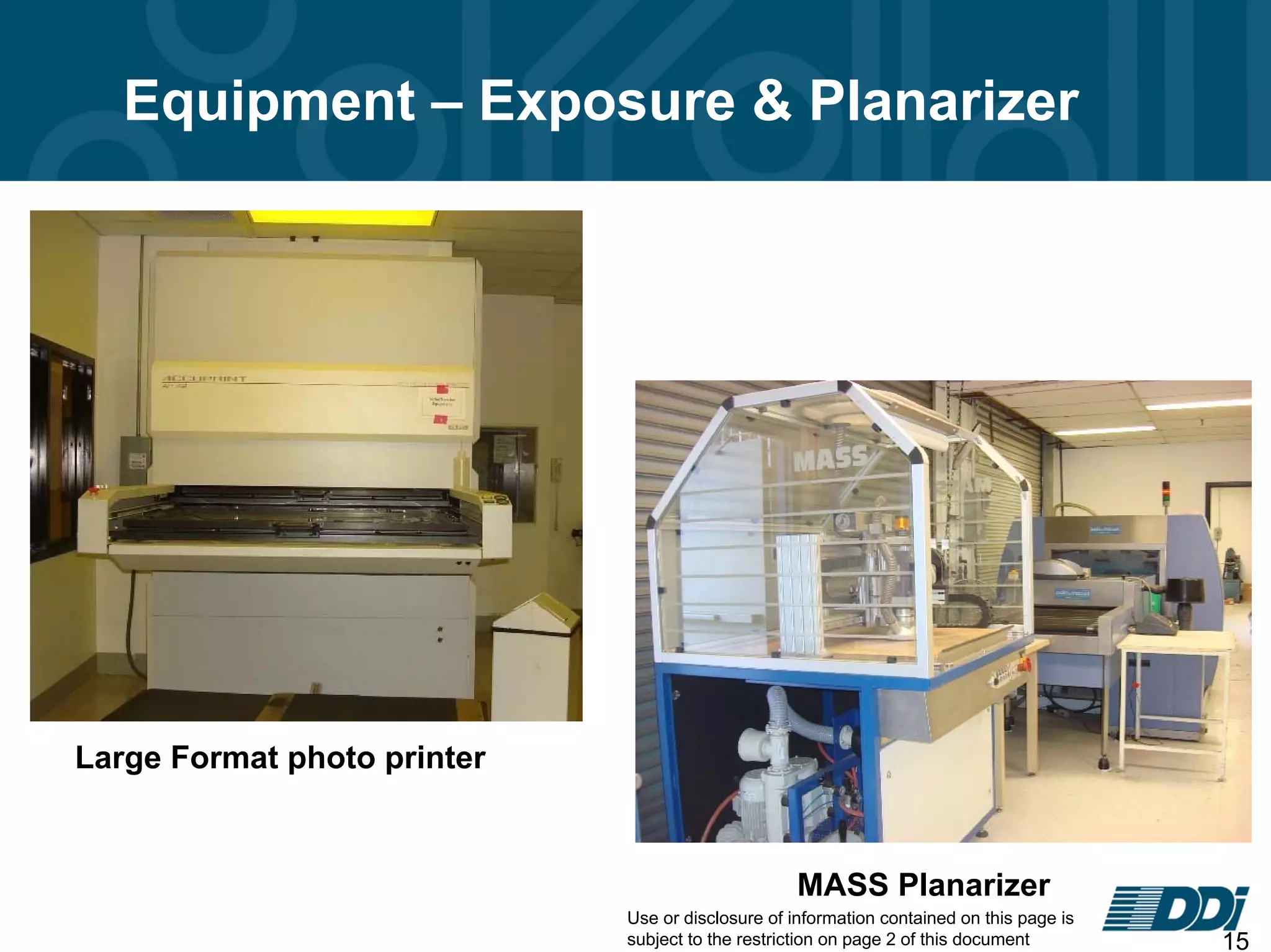

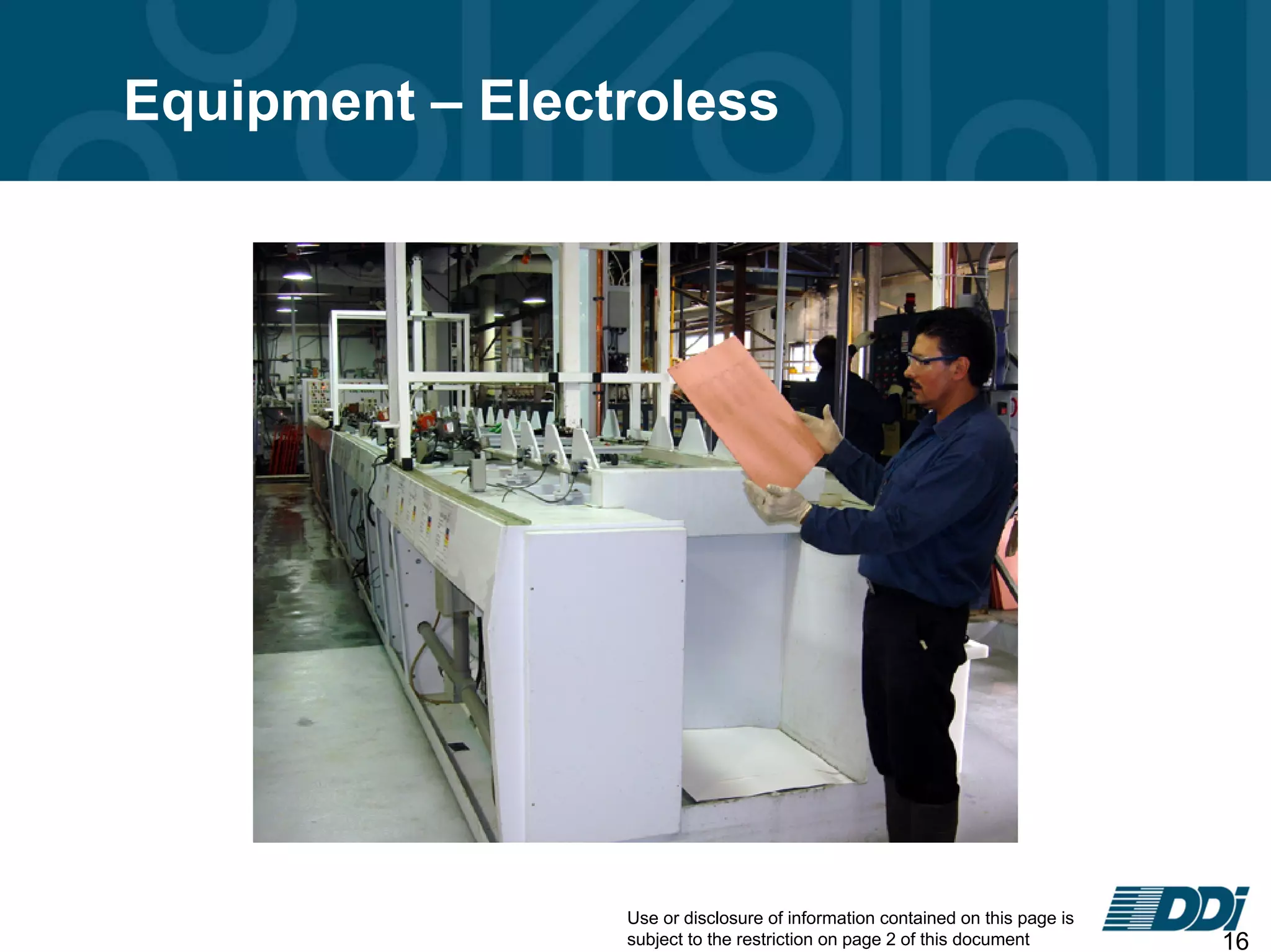

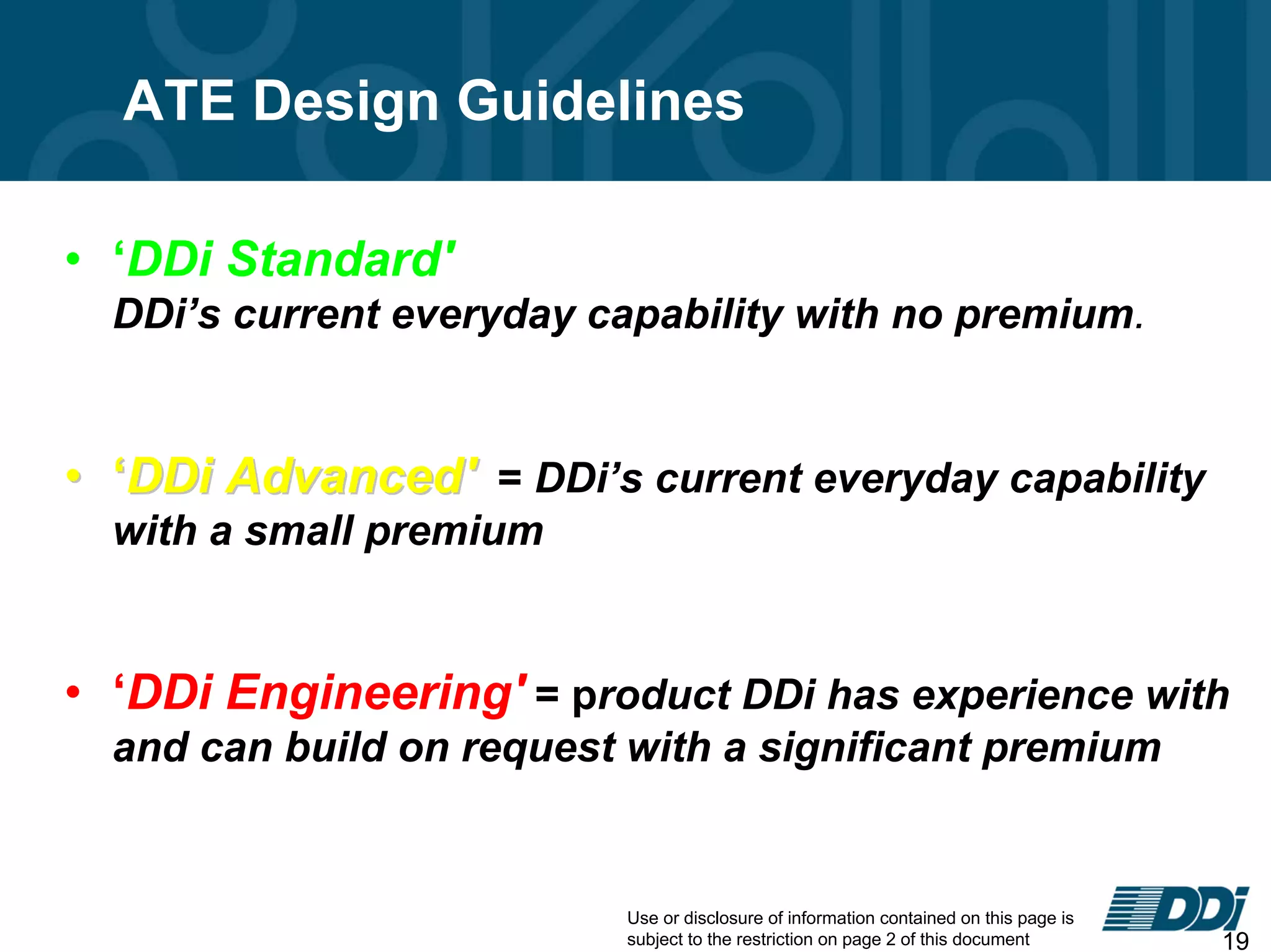

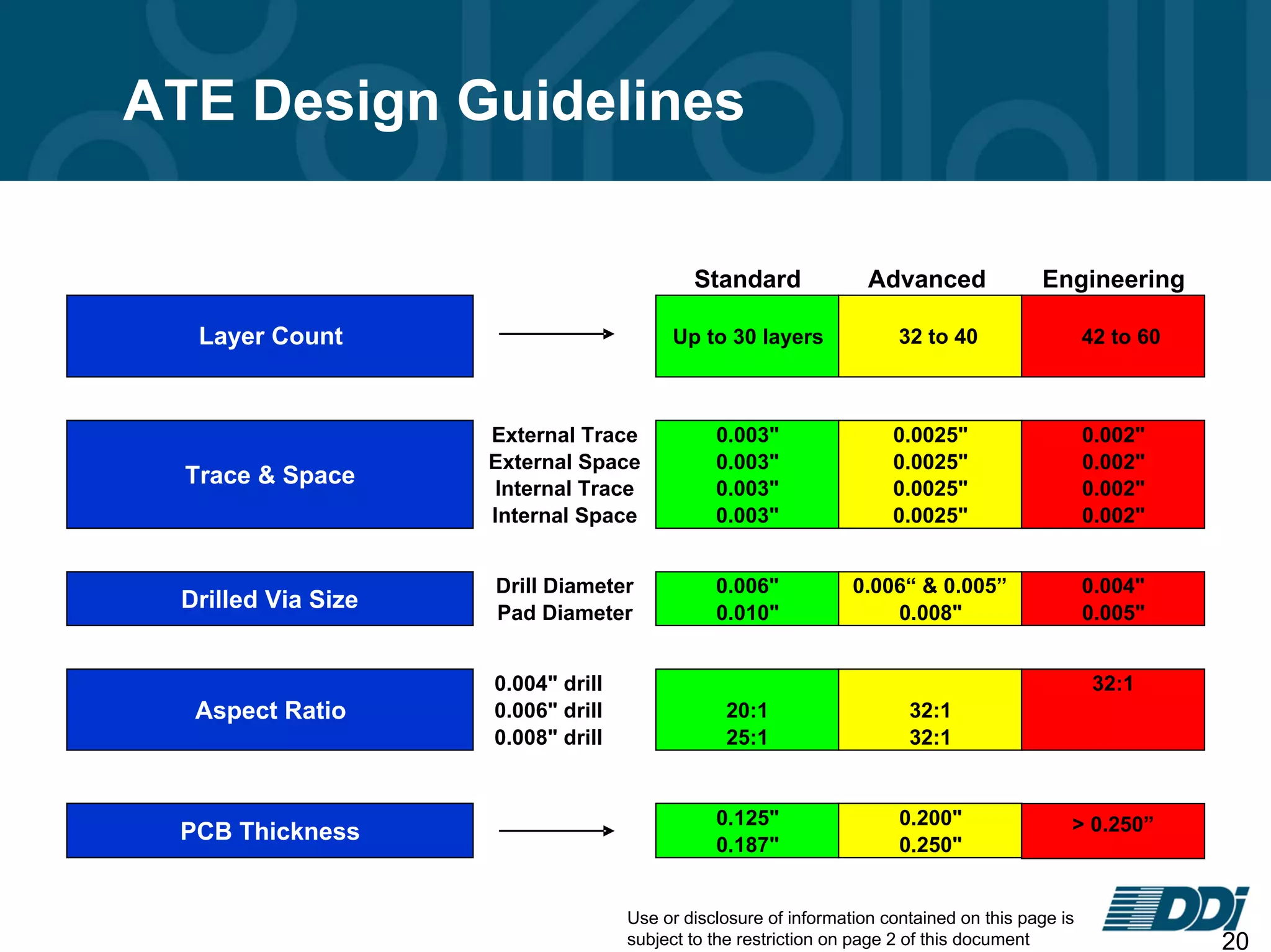

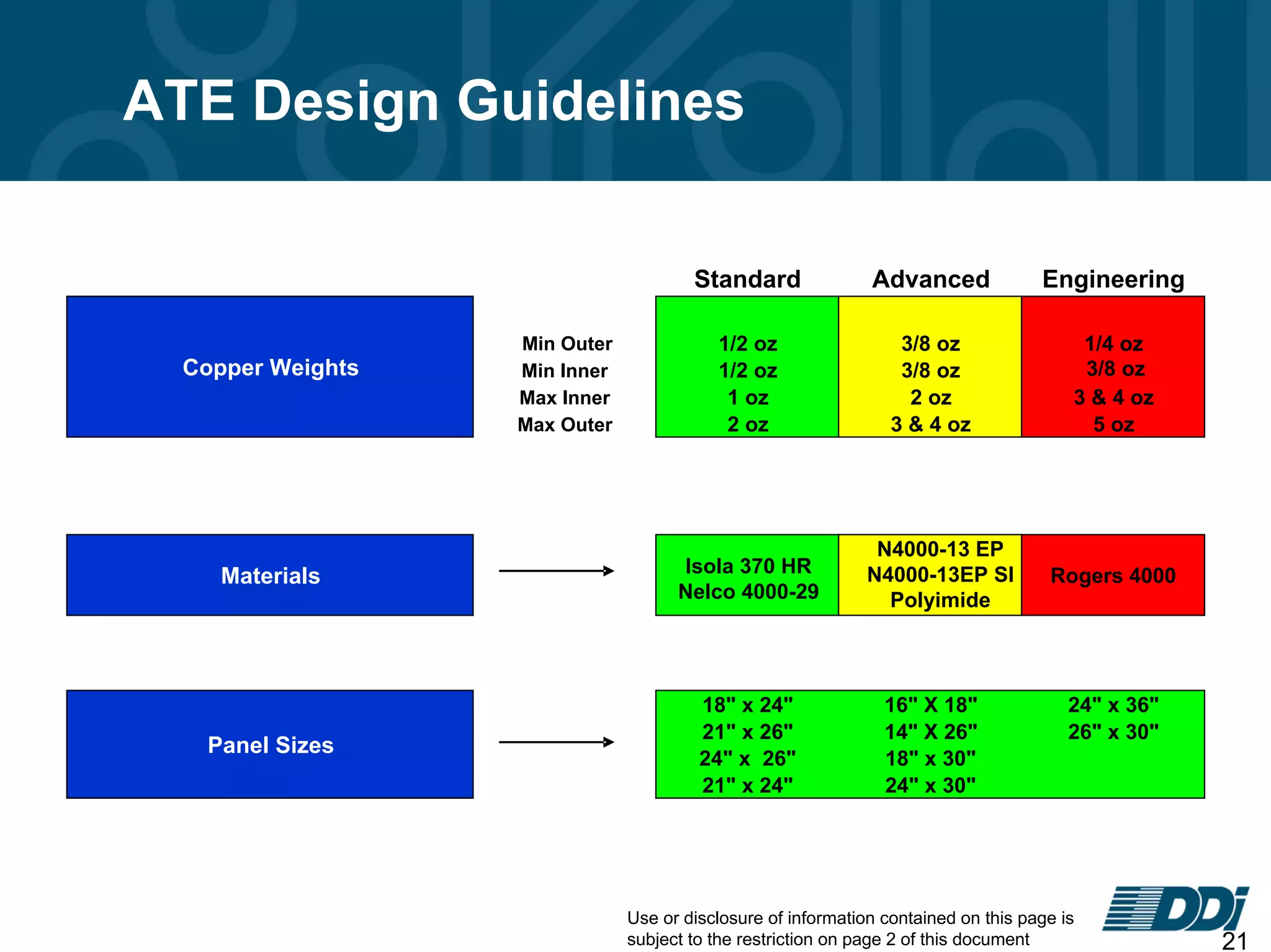

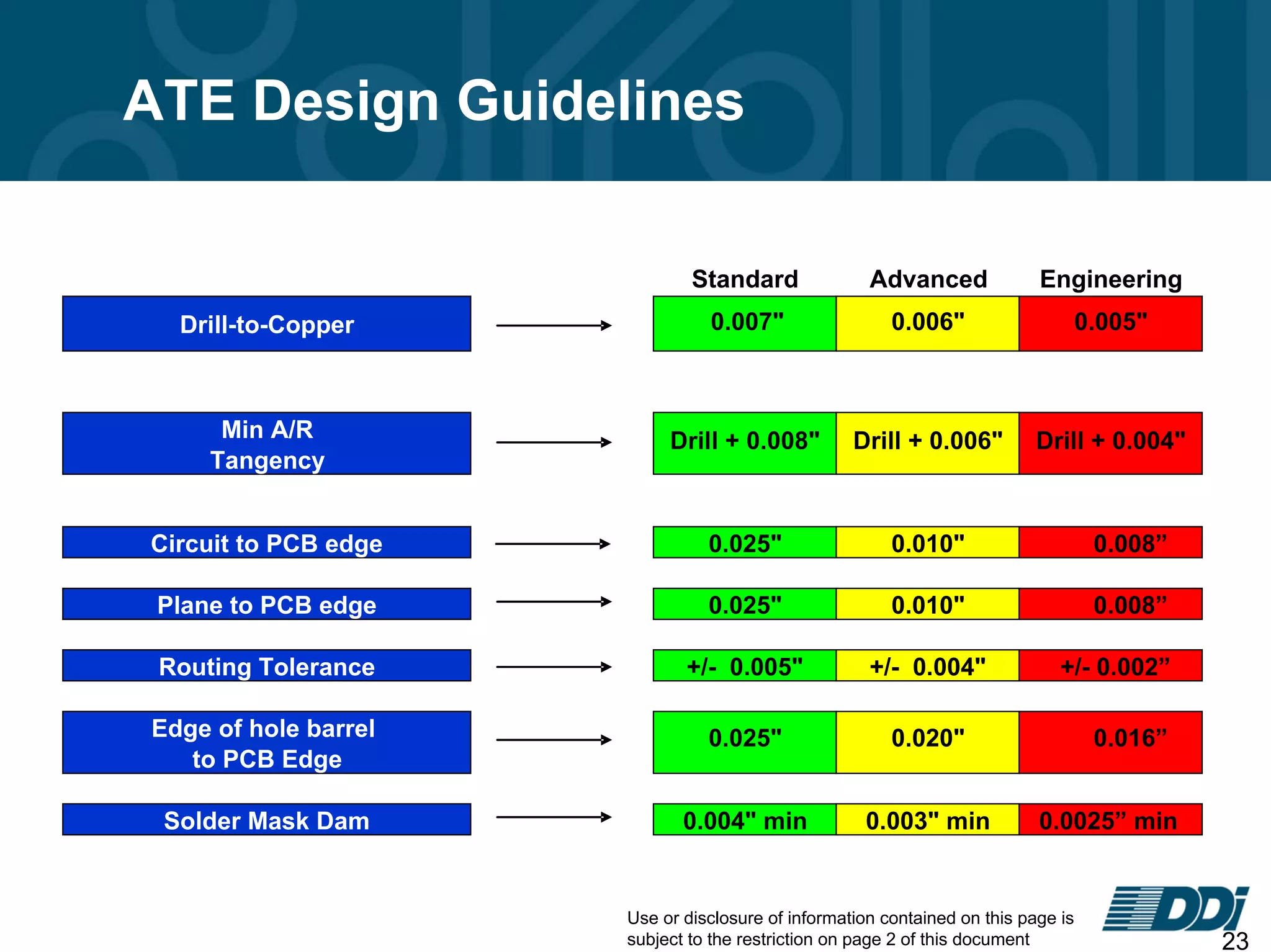

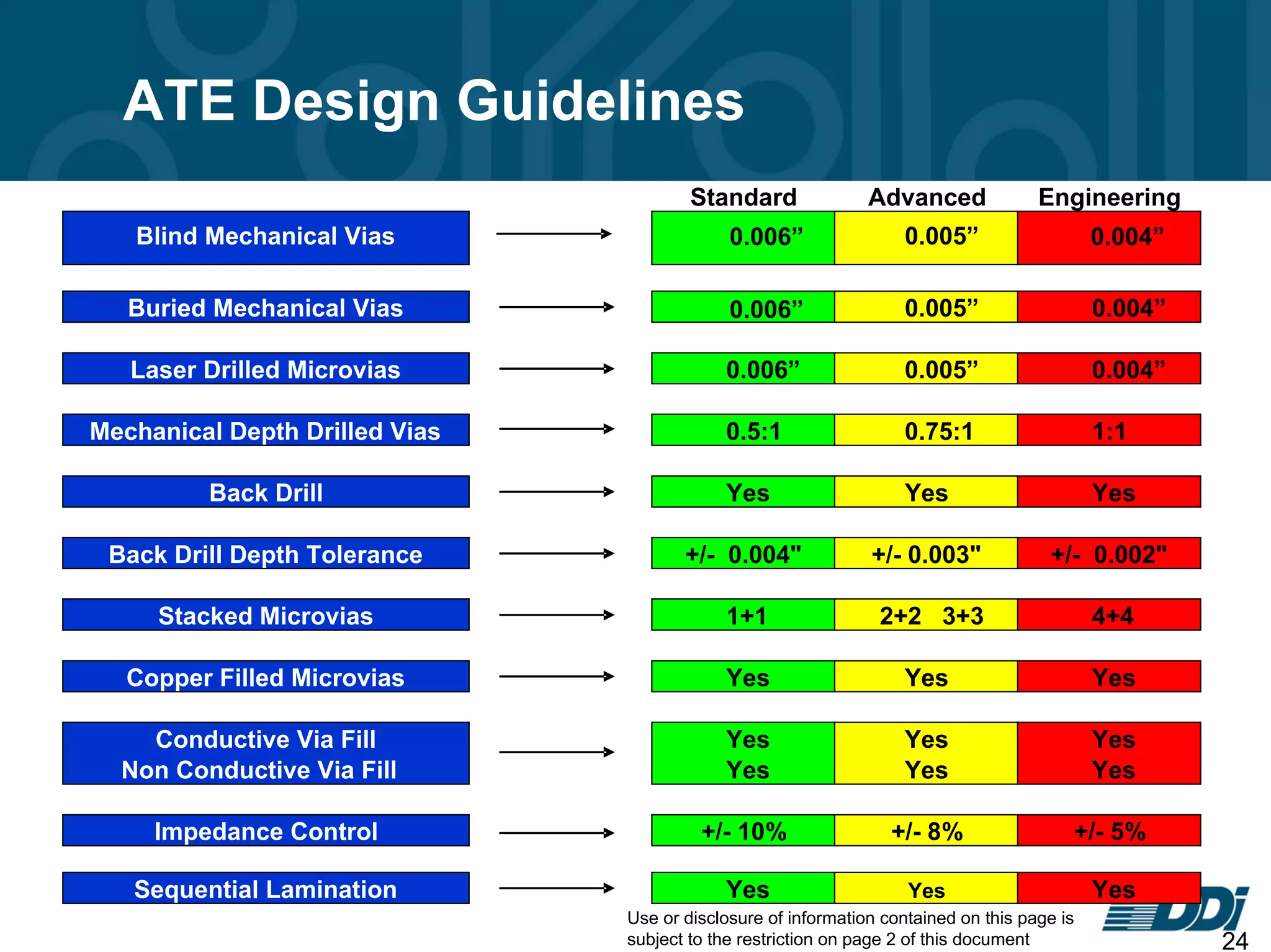

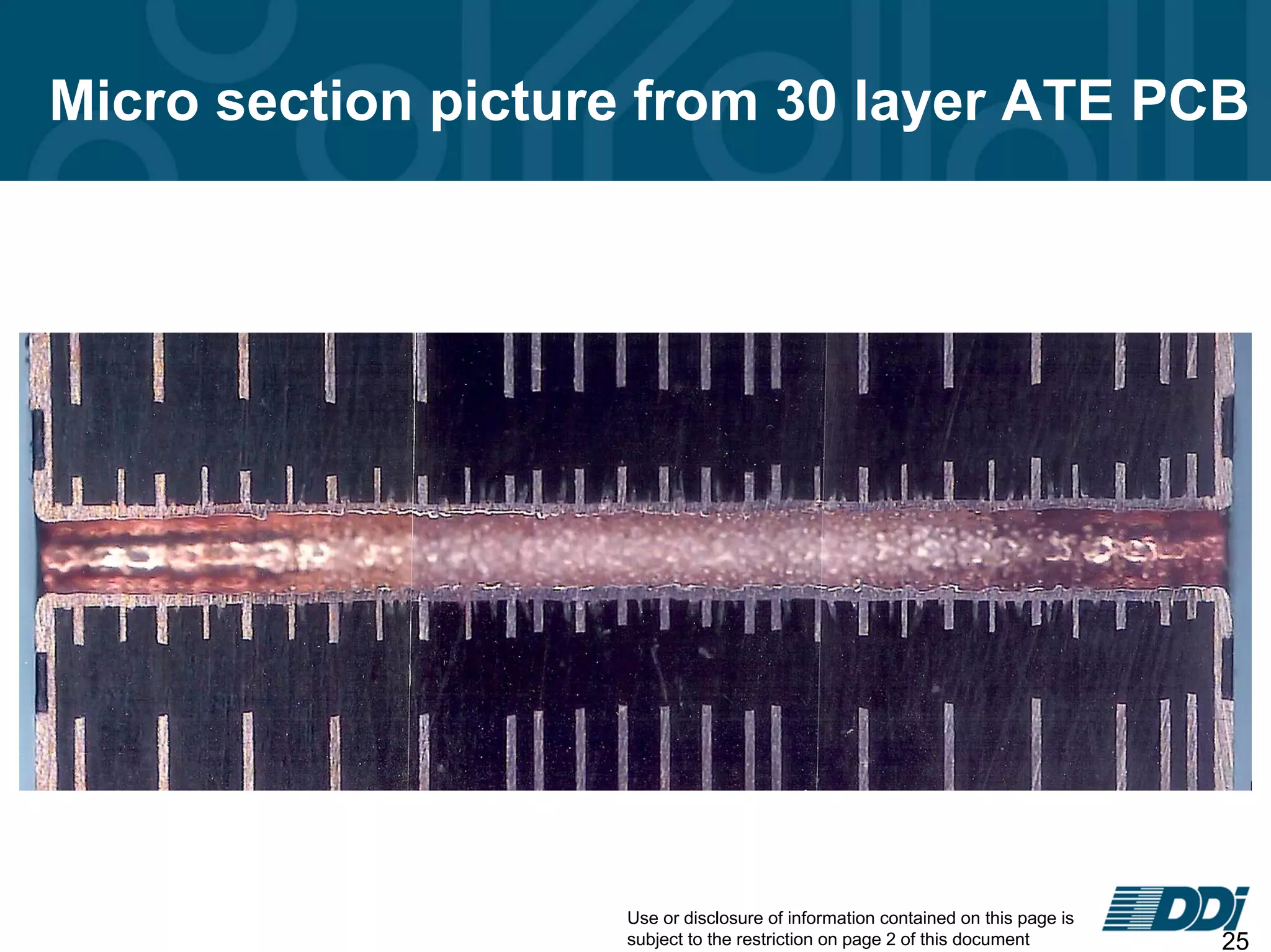

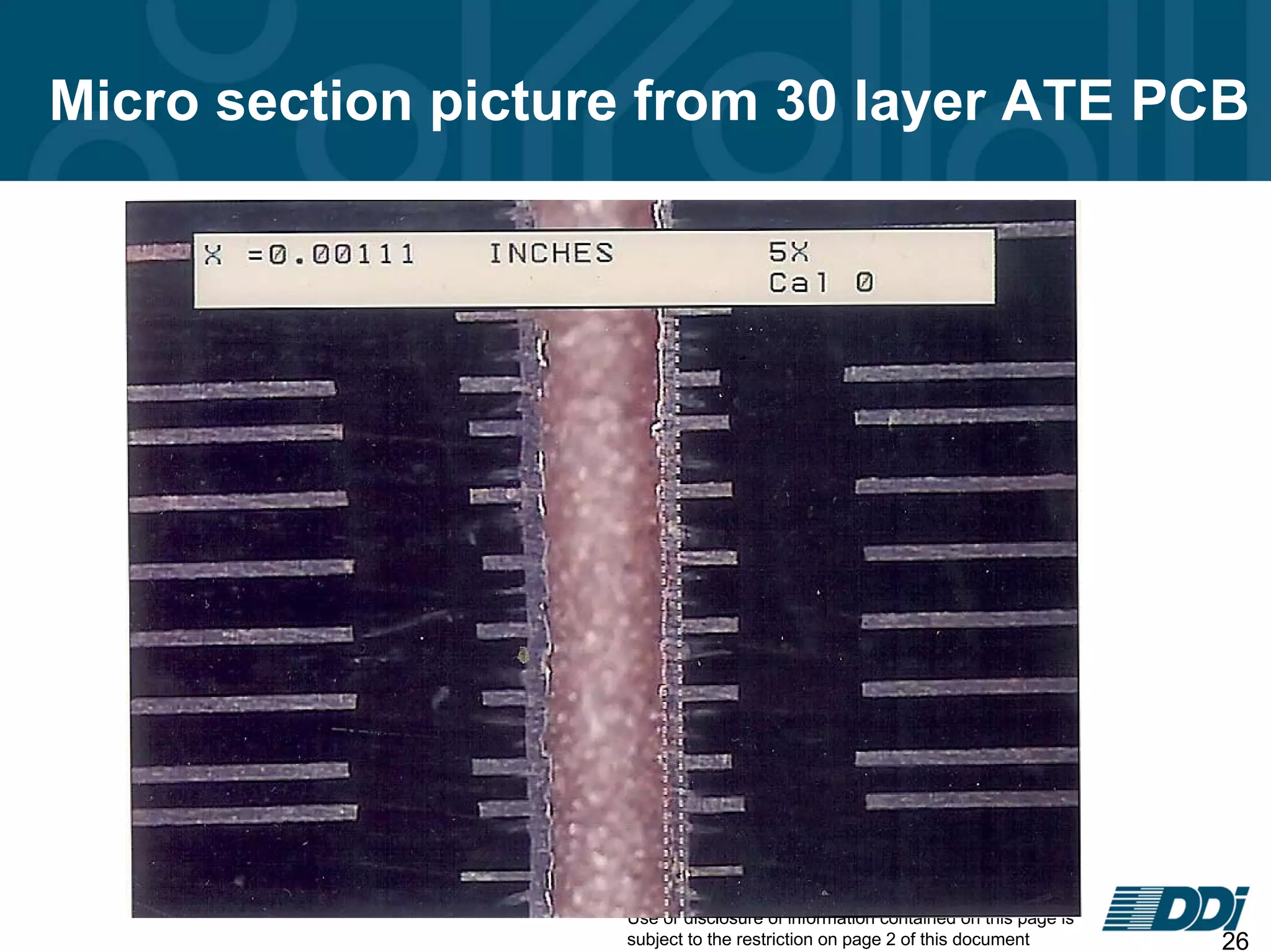

The document discusses DDi's expansion into the ATE/BIB market through acquiring new equipment, talent, and capabilities. This will allow them to produce specialized printed circuit boards for applications like semiconductor testing that require tight tolerances and processing controls. The new resources are described along with design guidelines for standard, advanced, and engineering-level boards to address various customer needs in this market.