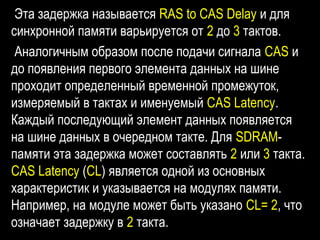

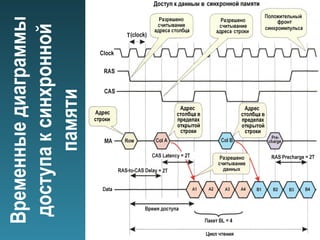

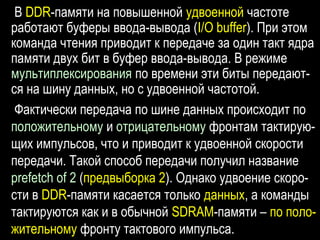

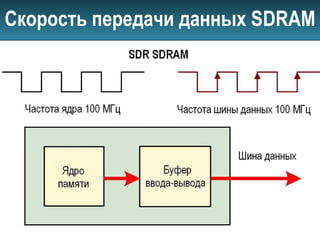

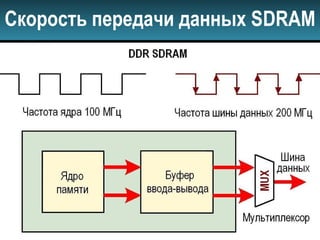

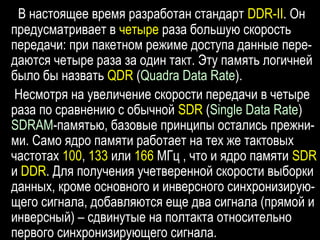

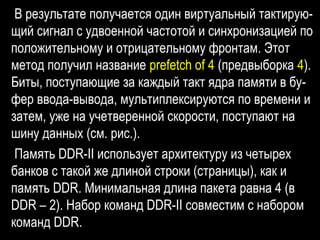

Документ описывает различные типы динамической памяти, включая FPM, EDO, SDRAM и DDR-память, а также их характеристики и преимущества. Основное внимание уделяется режиму быстрого страничного обмена, который позволяет улучшить производительность памяти за счет сокращения времени доступа. Также рассматриваются различные технологии передачи данных и их влияние на пропускную способность памяти.