⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2021 PAO1) C5-C6

Registro Universal: PROBLEMA # 1 (30%). Dada la siguiente configuración del registro universal #74194. ASM: Problema #2 (30%). El siguiente Sistema Digital funciona como una maquina secuencial modelo moore. Este sistema Digital tiene como entrada las señales: X0, X1, X2 y X3; y como salidas las señales: Q0 y Q1; tal como se presenta a continuación. Conversión de Flip-Flops: Problema #3 (20%) La siguiente tabla característica describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión exitosa de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K”. ⭐ For more information visit our blog: https://vasanza.blogspot.com/

Recommended

Recommended

More Related Content

More from Victor Asanza

More from Victor Asanza (20)

Recently uploaded

Recently uploaded (20)

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2021 PAO1) C5-C6

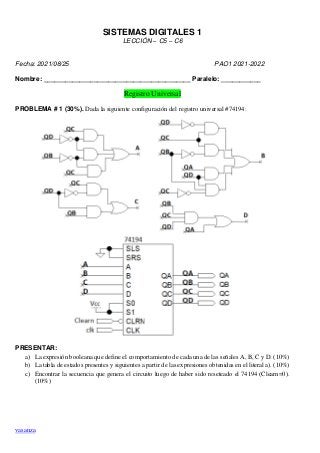

- 1. vasanza SISTEMAS DIGITALES 1 LECCIÓN – C5 – C6 Fecha: 2021/08/25 PAO1 2021-2022 Nombre: _________________________________________ Paralelo: ___________ Registro Universal PROBLEMA # 1 (30%). Dada la siguiente configuración del registro universal #74194: PRESENTAR: a) La expresión booleana que define el comportamiento de cada una de las señales A, B, C y D. (10%) b) La tabla de estados presentes y siguientes a partir de las expresiones obtenidas en el literal a). (10%) c) Encontrar la secuencia que genera el circuito luego de haber sido reseteado el 74194 (Clearn=0). (10%)

- 2. vasanza ASM Problema #2 (30%). El siguiente Sistema Digital funciona como una maquina secuencial modelo moore. Este sistema Digital tiene como entrada las señales: X0, X1, X2 y X3; y como salidas las señales: Q0 y Q1; tal como se presenta a continuación: Hay que recordar que las maquinas secuenciales sincrónicas están conformadas por tres bloques principales: Decodificador de estados siguientes, memoria de estados y decodificador de salidas. El decodificador de estados siguientes se describe en el siguiente mapa de karnaugh: La asignación de códigos de estado que deberá emplear es el siguiente: El circuito decodificador de salidas se describe con el siguiente código VHDL:

- 3. vasanza Se le pide: a) Realizar el diagrama de estados reducido que representa el funcionamiento de la maquina secuencial sincrónica, utilizar el siguiente formato: X3,X2,X1,X0/Q1,Q0 (10p). b) Completar las instrucciones en VHDL que describen el funcionamiento del decodificador de estados siguientes (10p). Resolución:

- 4. vasanza Conversión de Flip-Flops Problema #3 (20%) La siguiente tabla característica describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión exitosa de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K”: Tabla de característica del Flip-Flop “XY” Input Output x y Actual (𝑸𝒏) Siguiente (𝑸𝒏+𝟏) 0 0 0 1 1 1 1 0 1 1 0 1 0 0 1 1 0 1 0 0 1 0 Código VHDL de Flip-Flop: https://github.com/vasanza/MSI-VHDL/tree/2021PAE/LeccionC5 a) j <= ‘0’ when (x&y = “11”) else ‘1’; b) j <= ‘0’ when (x&y = “10”) else ‘1’; c) j <= ‘0’ when (x&y = “01”) else ‘1’; d) j <= ‘0’ when (x&y = “00”) else ‘1’; e) k <= ‘0’ when (x&y = “11”) else ‘1’; f) k <= ‘0’ when (x&y = “10”) else ‘1’; g) k <= ‘0’ when (x&y = “01”) else ‘1’; h) k <= ‘0’ when (x&y = “00”) else ‘1’; Resolución: j <= not(x) or not (y); entonces, j <= ‘0’ when (x&y = “11”) else ‘1’; k <= x or y; entonces, k <= ‘0’ when (x&y = “00”) else ‘1’;

- 5. vasanza Problema #4 (20%) La siguiente tabla característica describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión exitosa de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K”: Tabla de característica del Flip-Flop “XY” Input Output x y Actual (𝑸𝒏) Siguiente (𝑸𝒏+𝟏) 0 0 0 1 1 0 1 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 Código VHDL de Flip-Flop: https://github.com/vasanza/MSI-VHDL/tree/2021PAE/LeccionC5 a) j <= ‘0’ when (x&y = “11”) else ‘1’; b) j <= ‘0’ when (x&y = “10”) else ‘1’; c) j <= ‘0’ when (x&y = “01”) else ‘1’; d) j <= ‘0’ when (x&y = “00”) else ‘1’; e) k <= ‘0’ when (x&y = “11”) else ‘1’; f) k <= ‘0’ when (x&y = “10”) else ‘1’; g) k <= ‘0’ when (x&y = “01”) else ‘1’; h) k <= ‘0’ when (x&y = “00”) else ‘1’; Resolución: j <= not(x) or y; entonces, j <= ‘0’ when (x&y = “10”) else ‘1’; k <= x or not(y); entonces, k <= ‘0’ when (x&y = “01”) else ‘1’;

- 6. vasanza Problema #5 (20%) La siguiente tabla característica describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión exitosa de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K”: Tabla de característica del Flip-Flop “XY” Input Output x y Actual (𝑸𝒏) Siguiente (𝑸𝒏+𝟏) 0 0 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 1 0 0 1 0 Código VHDL de Flip-Flop: https://github.com/vasanza/MSI-VHDL/tree/2021PAE/LeccionC5 a) j <= ‘0’ when (x&y = “11”) else ‘1’; b) j <= ‘0’ when (x&y = “10”) else ‘1’; c) j <= ‘0’ when (x&y = “01”) else ‘1’; d) j <= ‘0’ when (x&y = “00”) else ‘1’; e) k <= ‘0’ when (x&y = “11”) else ‘1’; f) k <= ‘0’ when (x&y = “10”) else ‘1’; g) k <= ‘0’ when (x&y = “01”) else ‘1’; h) k <= ‘0’ when (x&y = “00”) else ‘1’; Resolución: j <= not(x) or not (y); entonces, j <= ‘0’ when (x&y = “11”) else ‘1’; k <= x or not(y); entonces, k <= ‘0’ when (x&y = “01”) else ‘1’;

- 7. vasanza Problema #6 (20%) La siguiente tabla característica describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión exitosa de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K”: Tabla de característica del Flip-Flop “XY” Input Output x y Actual (𝑸𝒏) Siguiente (𝑸𝒏+𝟏) 0 0 0 1 1 1 1 0 0 1 0 1 0 0 1 1 0 1 0 1 1 0 Código VHDL de Flip-Flop: https://github.com/vasanza/MSI-VHDL/tree/2021PAE/LeccionC5 a) j <= ‘0’ when (x&y = “11”) else ‘1’; b) j <= ‘0’ when (x&y = “10”) else ‘1’; c) j <= ‘0’ when (x&y = “01”) else ‘1’; d) j <= ‘0’ when (x&y = “00”) else ‘1’; e) k <= ‘0’ when (x&y = “11”) else ‘1’; f) k <= ‘0’ when (x&y = “10”) else ‘1’; g) k <= ‘0’ when (x&y = “01”) else ‘1’; h) k <= ‘0’ when (x&y = “00”) else ‘1’; Resolución: j <= x or not(y); entonces, j <= ‘0’ when (x&y = “01”) else ‘1’; k <= x or y; entonces, k <= ‘0’ when (x&y = “00”) else ‘1’;