Embed presentation

Downloaded 112 times

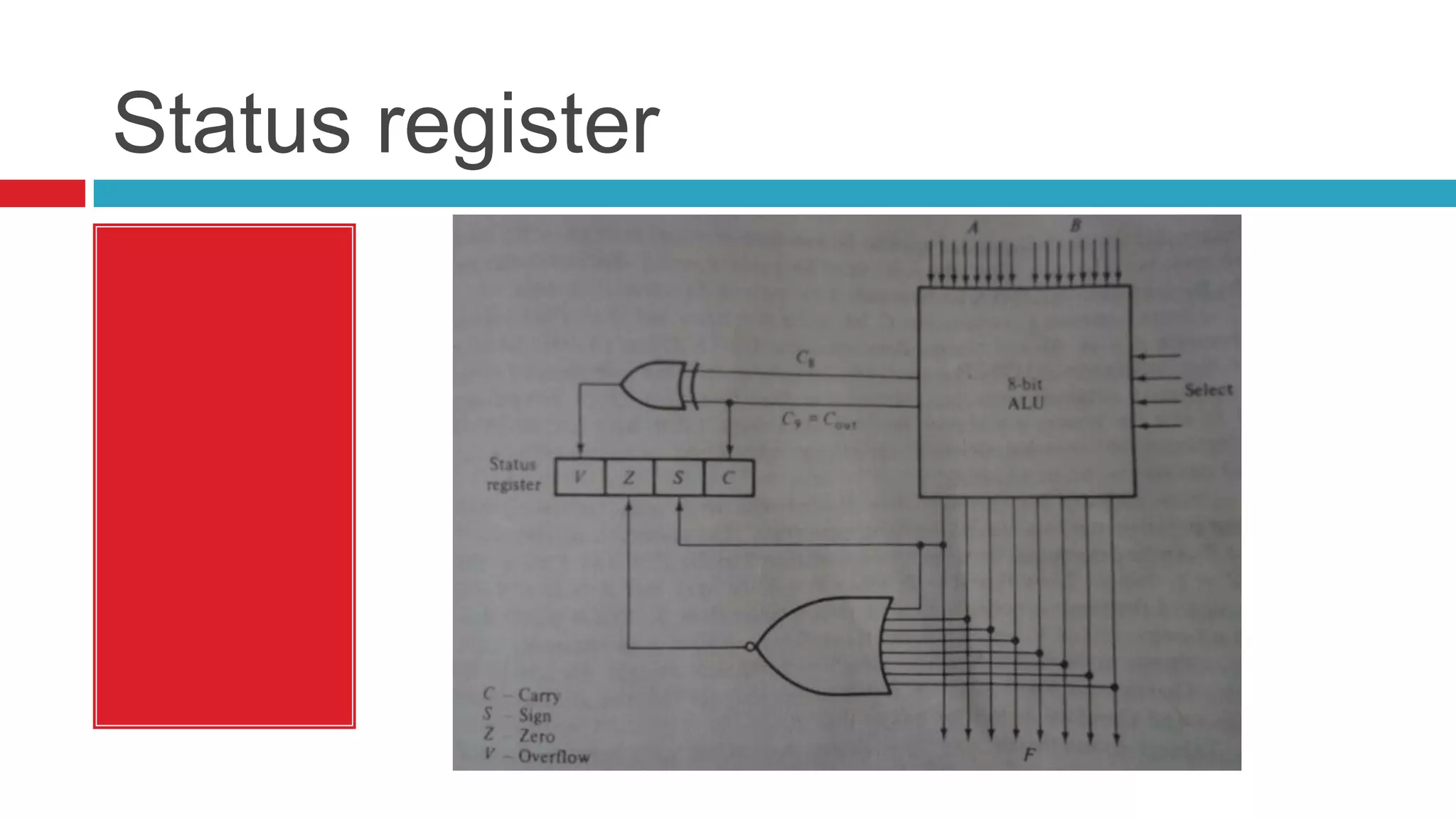

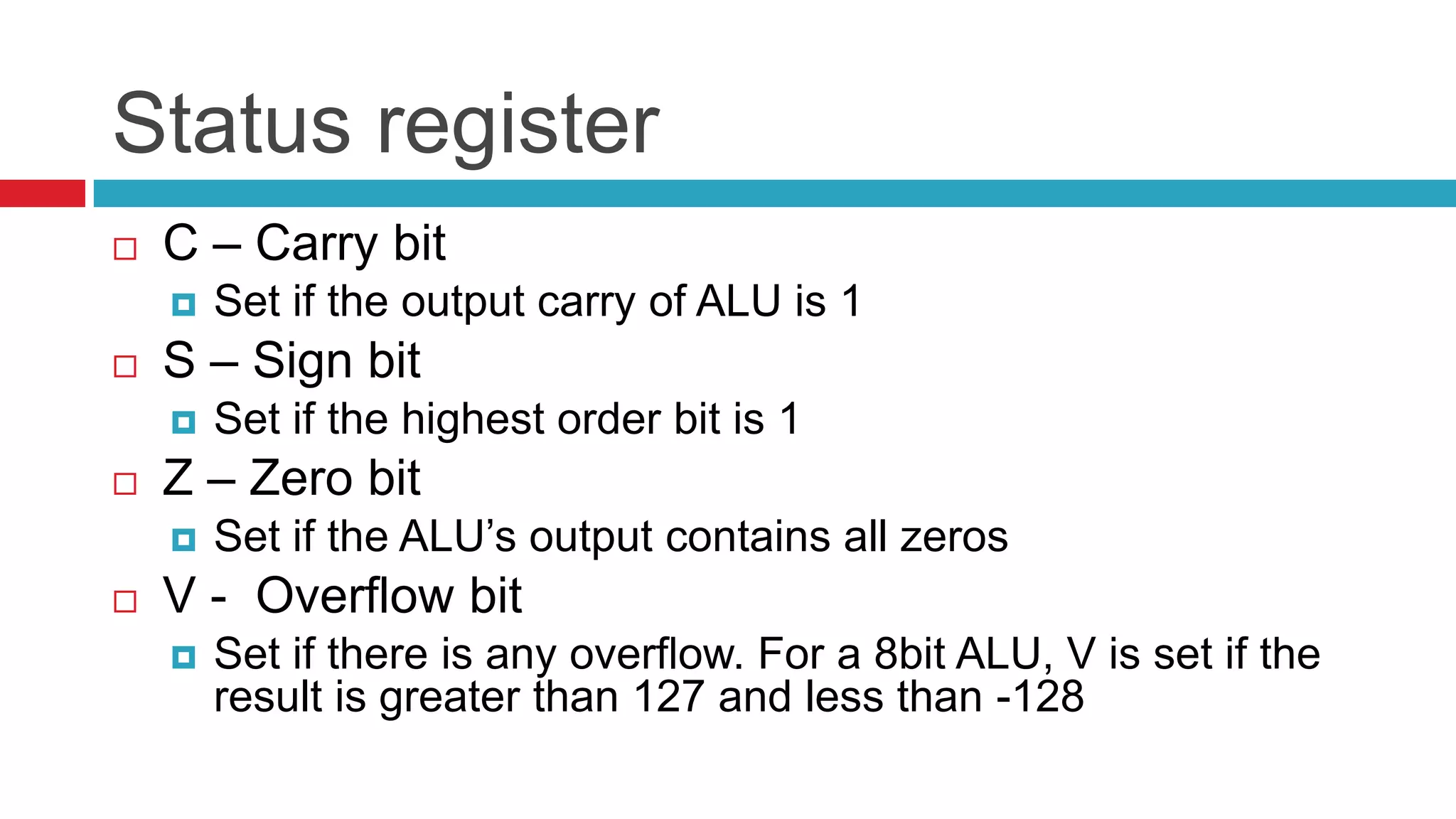

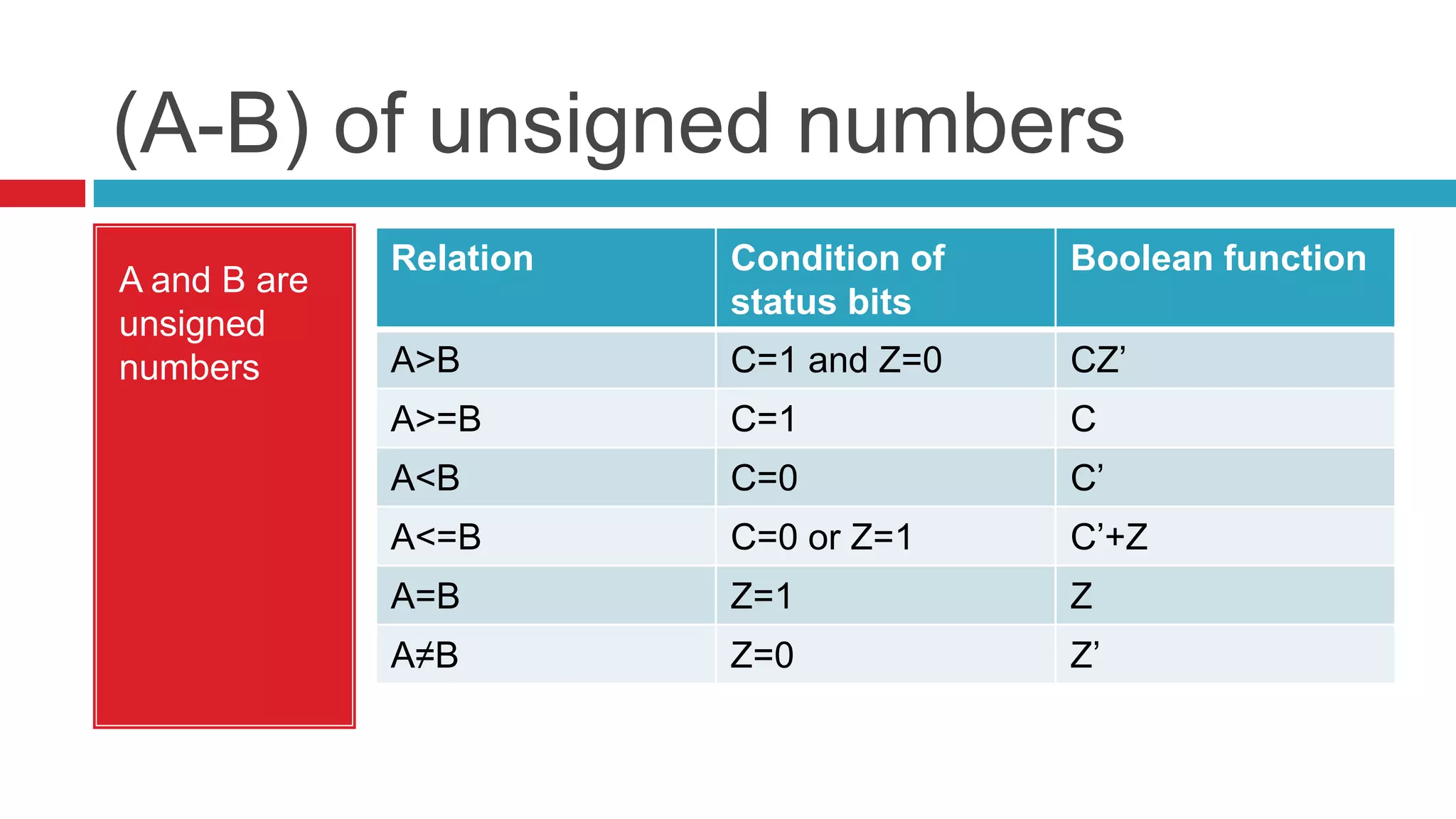

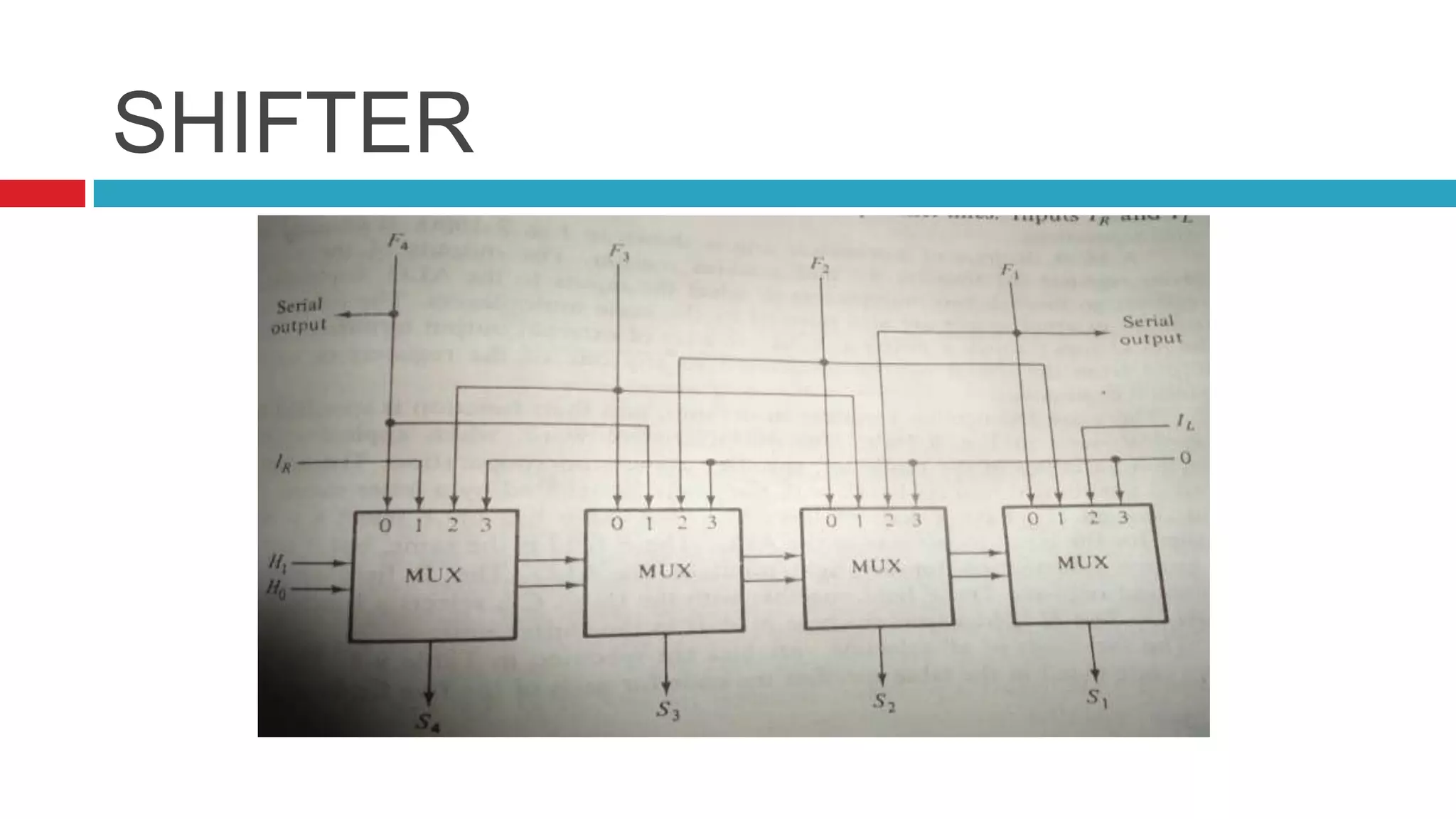

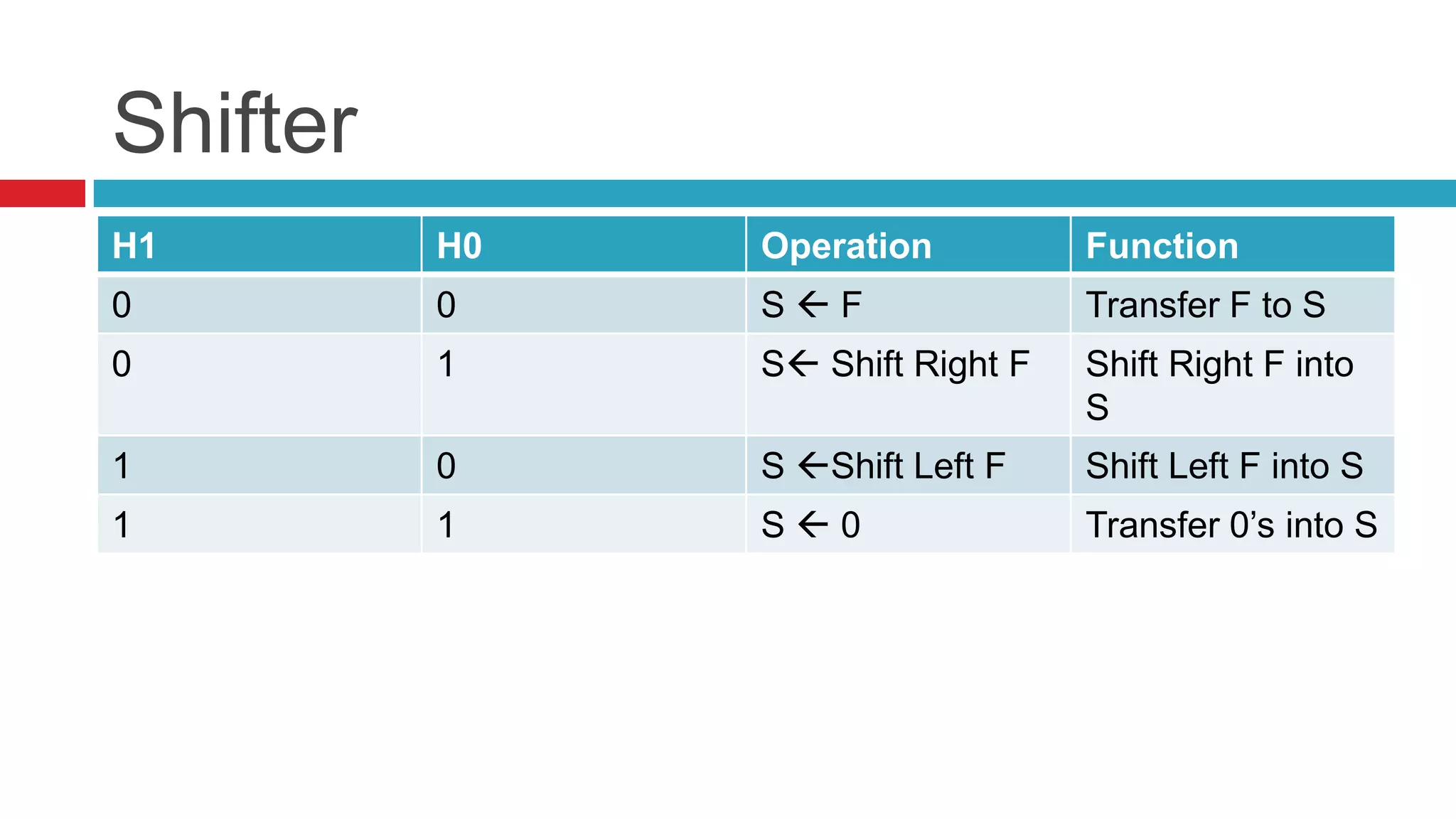

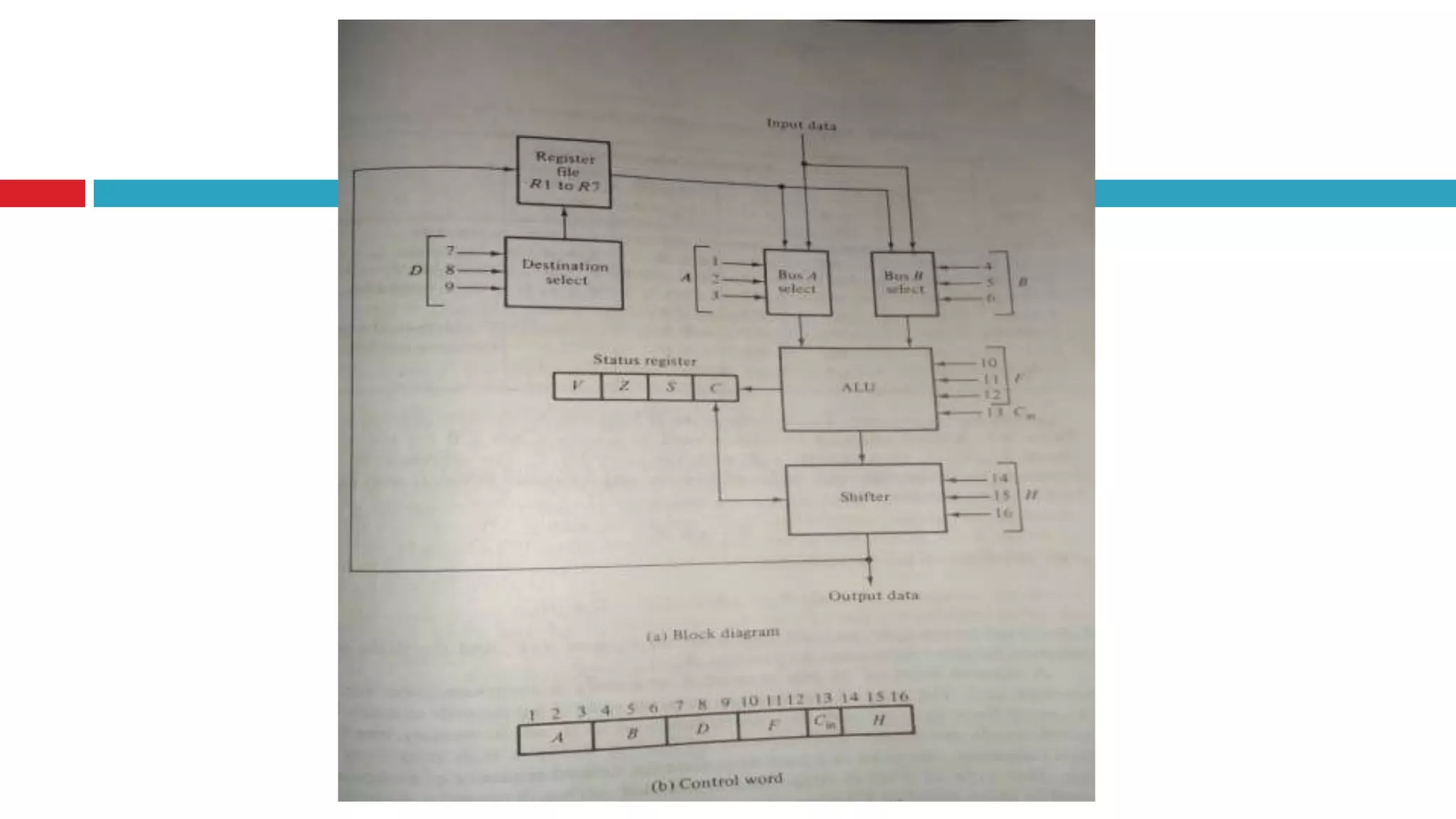

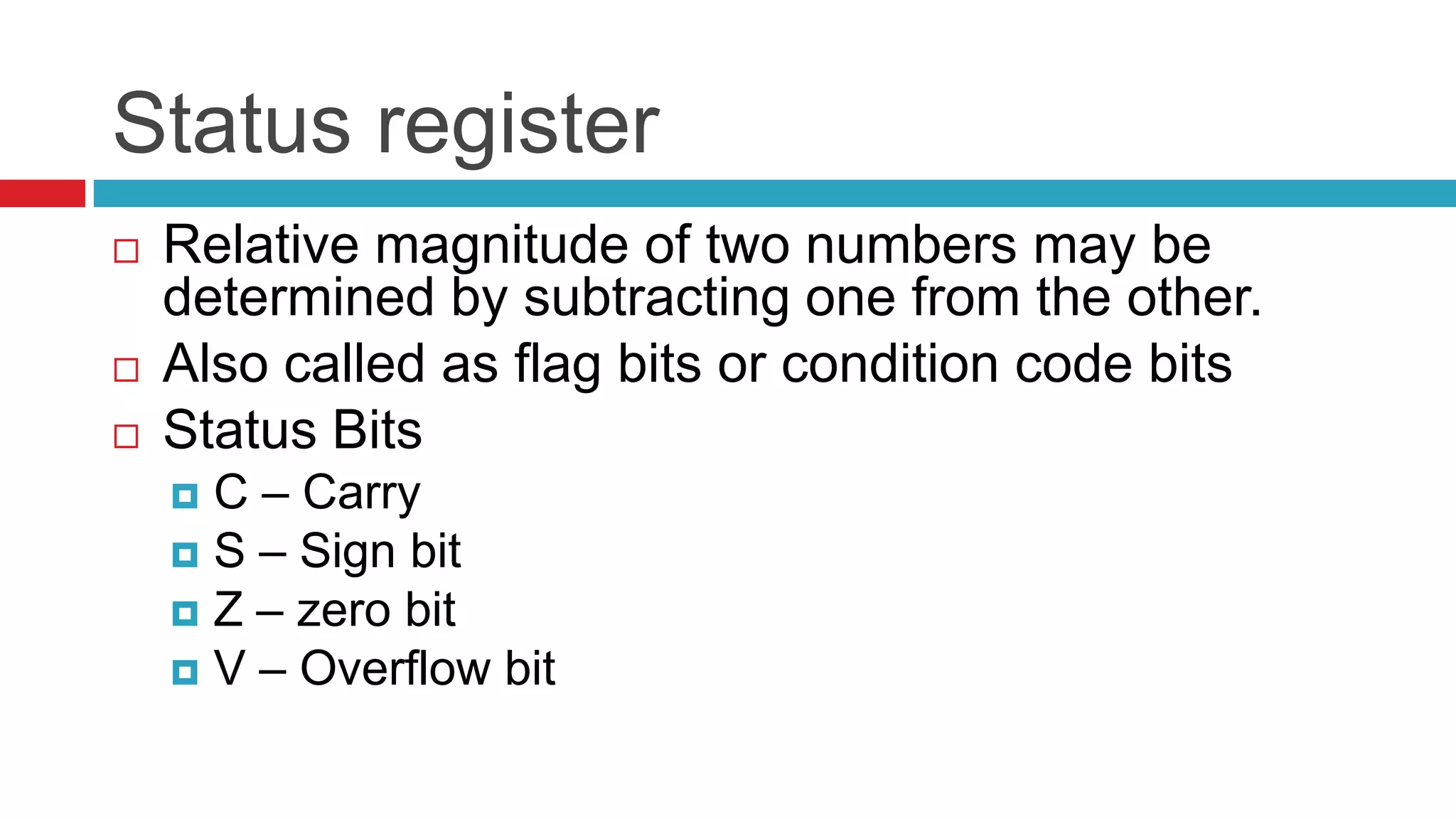

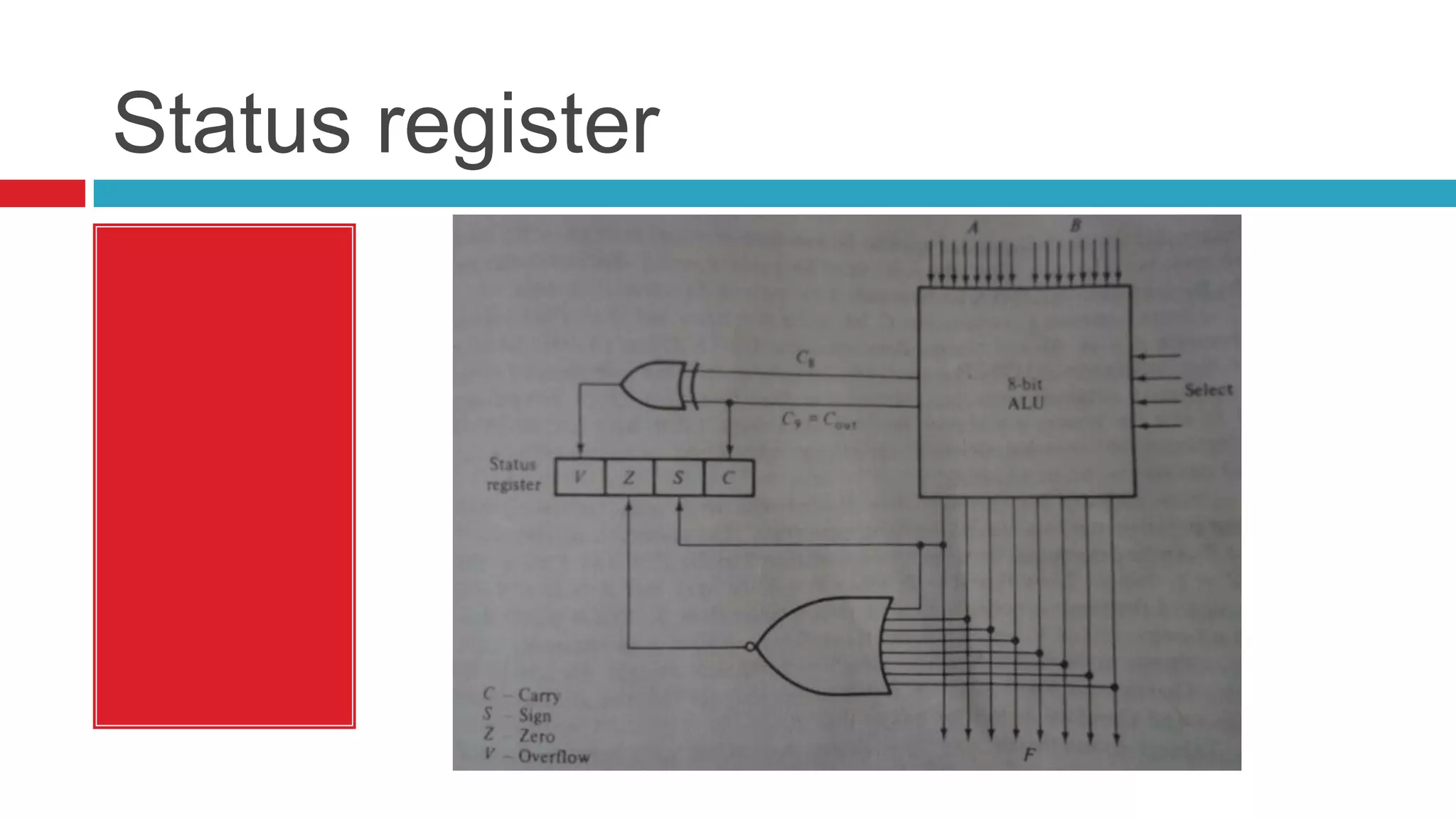

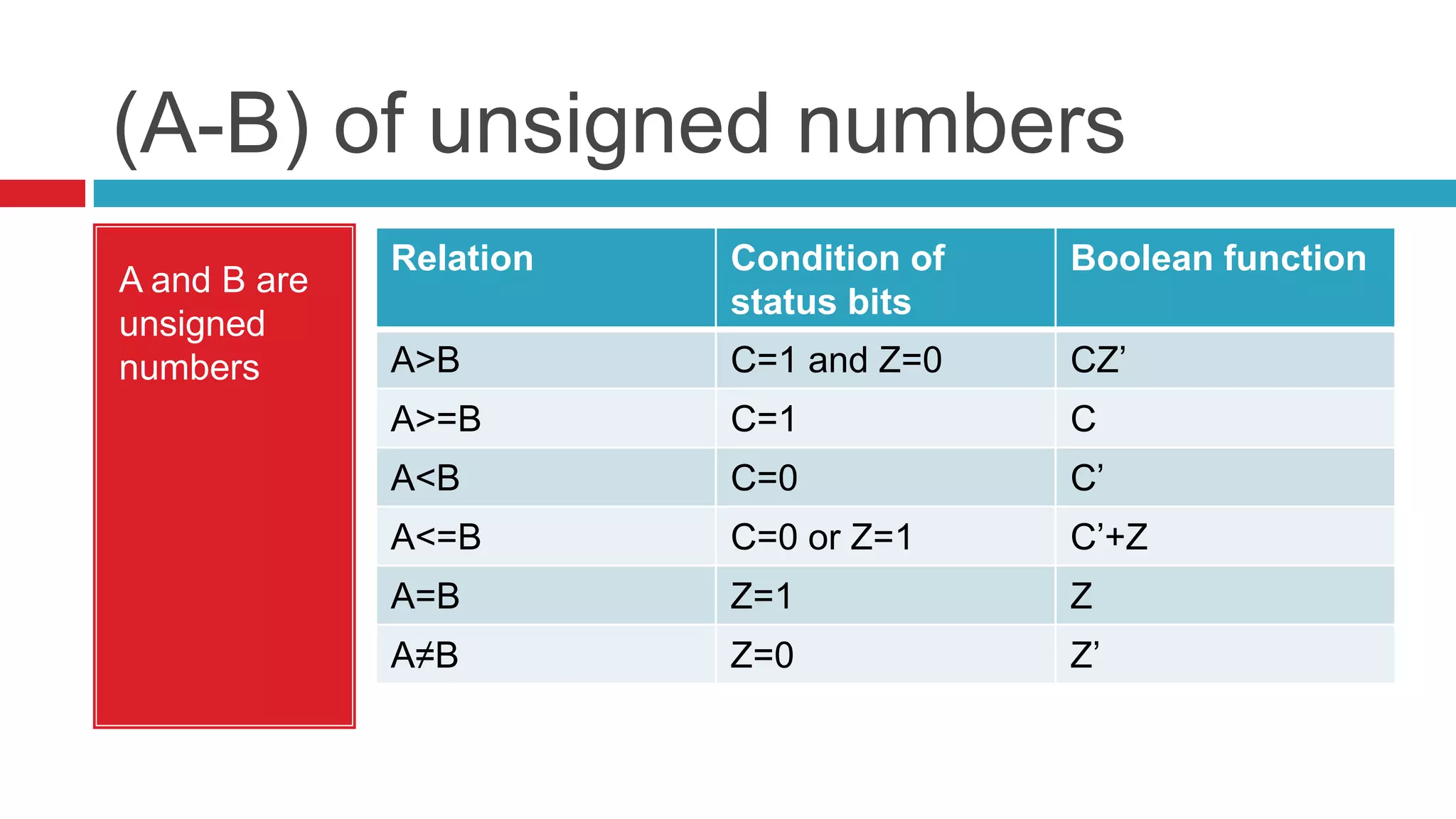

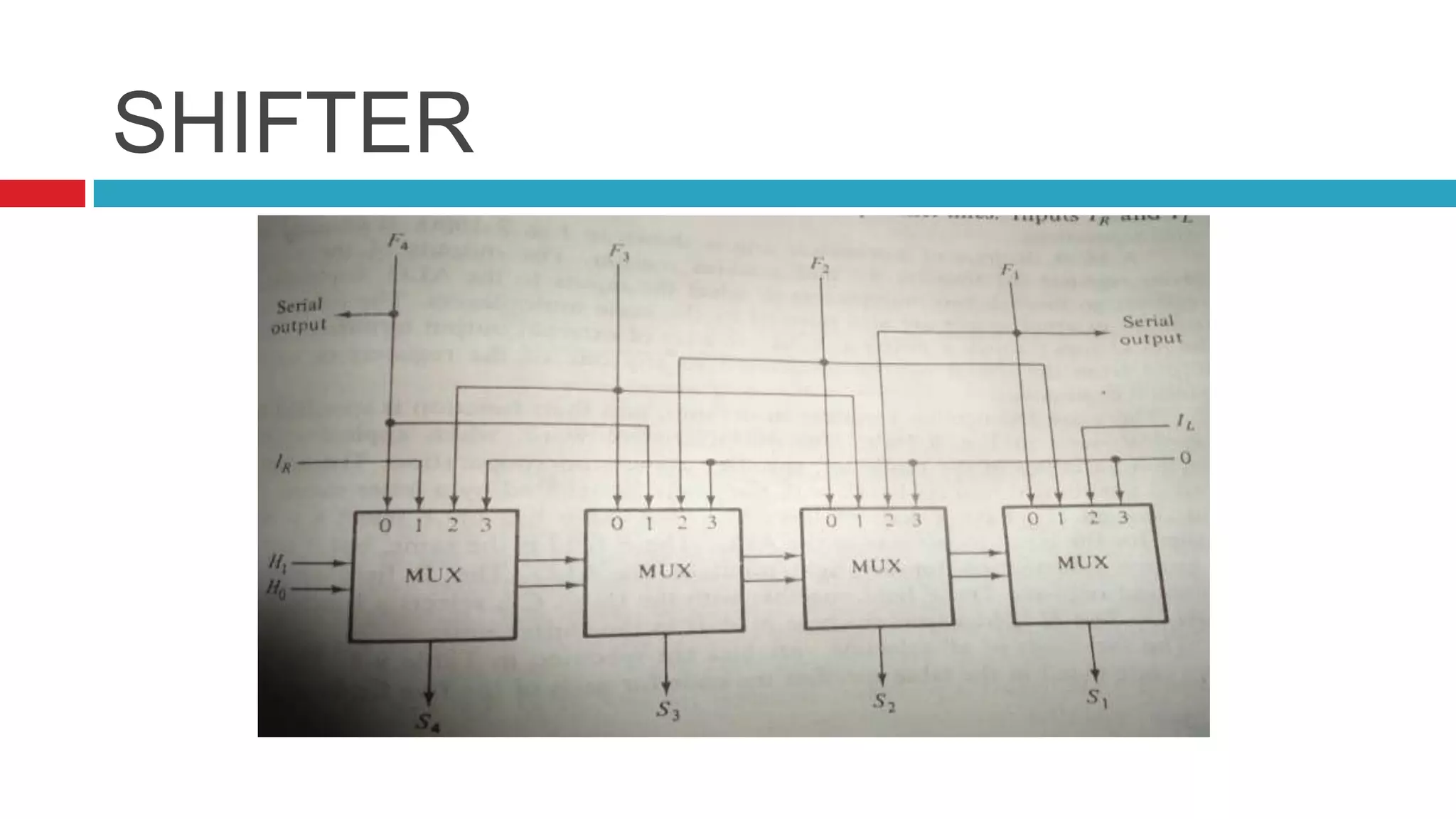

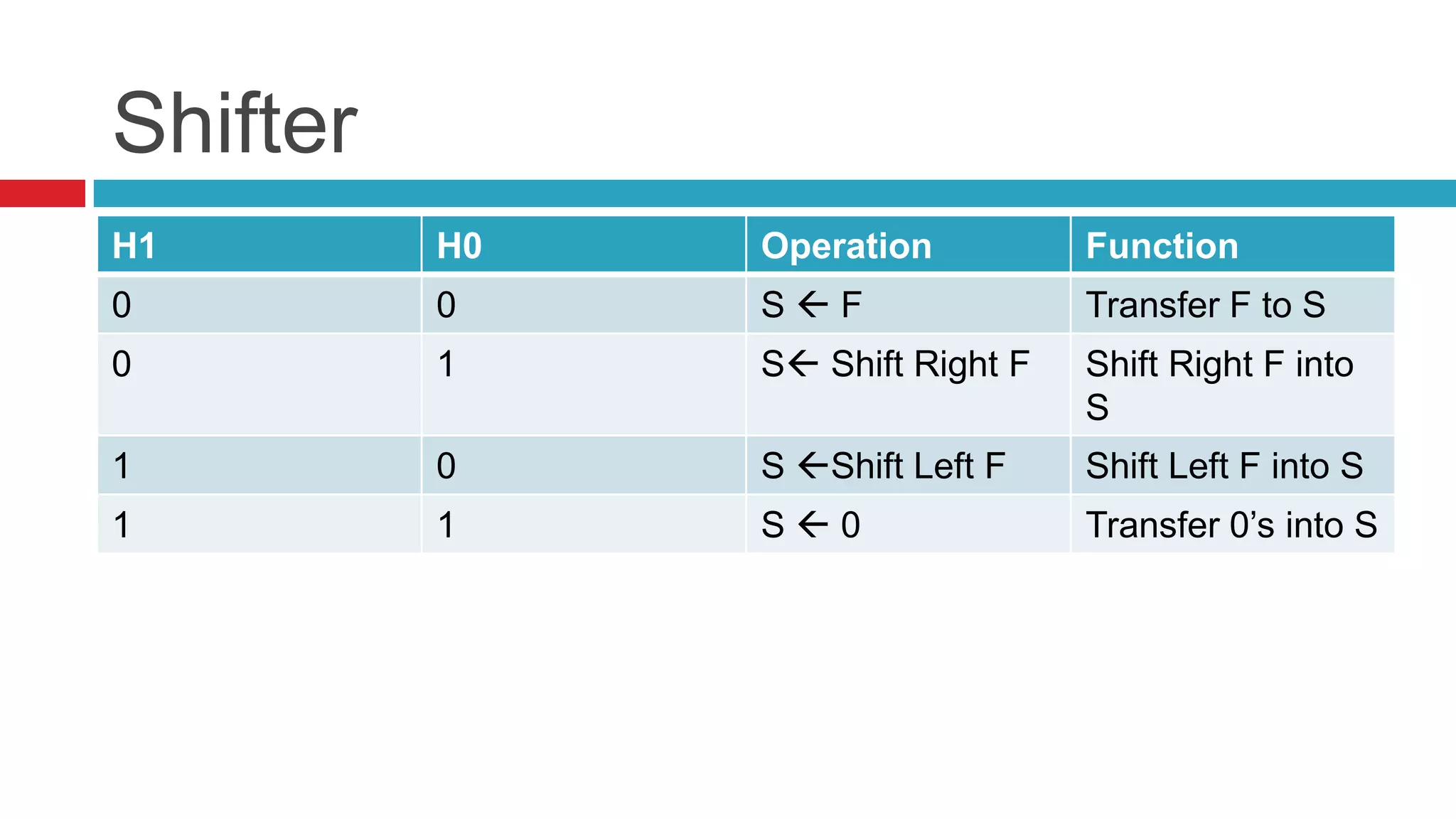

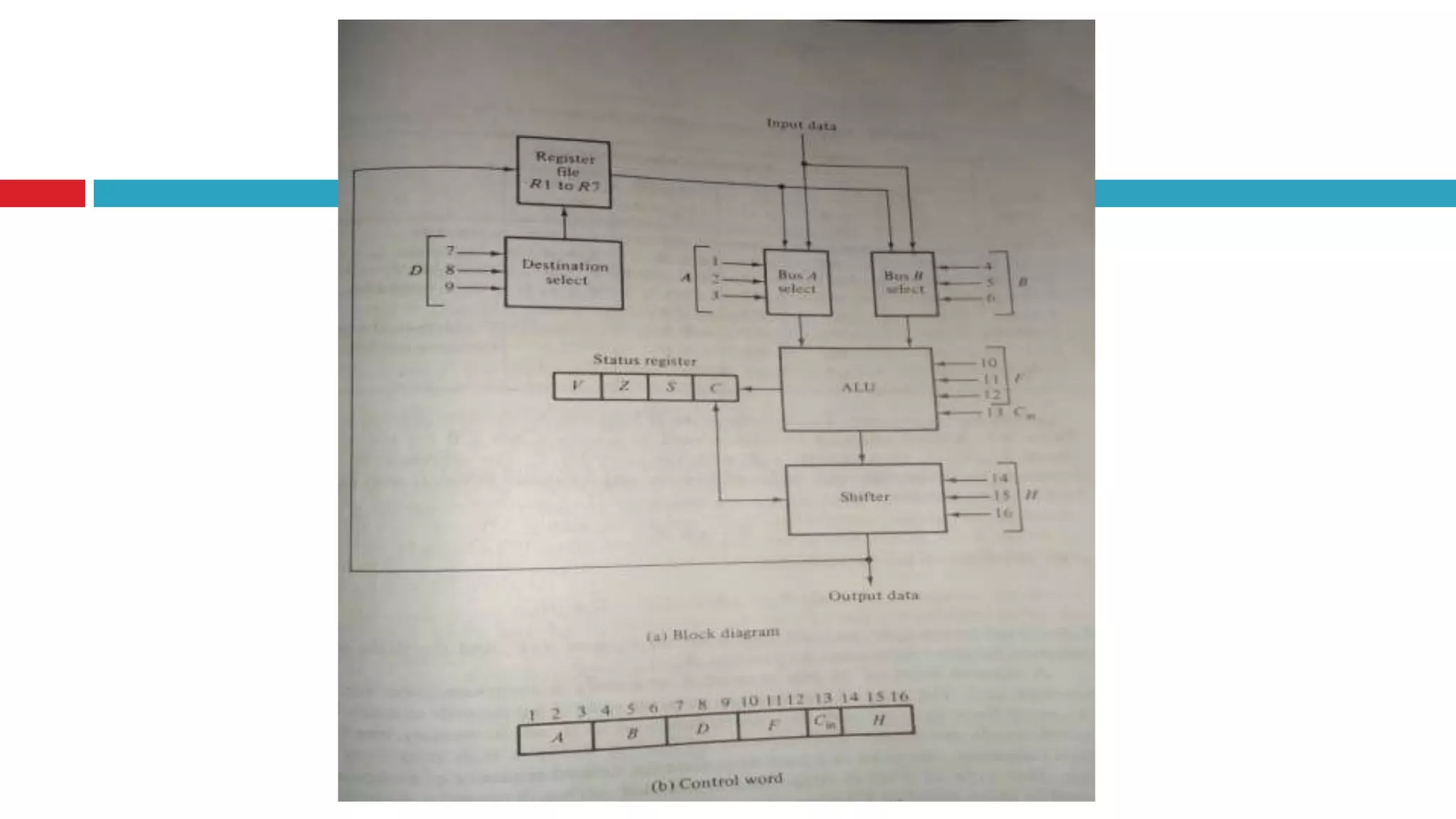

The document discusses status registers and shift registers used in digital circuits. A status register contains status bits that indicate the result of arithmetic logic unit (ALU) operations, including carry (C), sign (S), zero (Z), and overflow (V) bits. The carry bit is set if there is an output carry from the ALU, the sign bit is set if the highest order bit is 1, the zero bit is set if the ALU output is all zeros, and the overflow bit is set if the result is out of the ALU's range. Shift registers are used to shift data in digital circuits.