More Related Content

PPTX

PDF

PDF

PDF

PDF

PDF

PDF

PPTX

Similar to NANDからテトリスへ_前編.pdf

PDF

PDF

PPTX

Hardware Design Exercises PDF

PPT

コンピュータの構成と設計 第3版 第1章 勉強会資料 PPTX

PDF

PDF

2015年度GPGPU実践基礎工学 第4回 CPUのアーキテクチャ PDF

PPTX

PDF

2015年度GPGPU実践プログラミング 第3回 GPGPUプログラミング環境 PPTX

PDF

第3回ローレイヤー勉強会 : FPGAでコンピュータを作ってみた PPTX

Hybrid computing using a neural network with dynamic external memory PDF

Synthesijer.Scala (PROSYM 2015) PDF

2015年度GPGPU実践基礎工学 第6回 ソフトウェアによるCPUの高速化技術 PDF

PDF

GPGPU Education at Nagaoka University of Technology: A Trial Run PPTX

PPTX

More from ヴィスコ・テクノロジーズ株式会社

PDF

組み合わせ最適化問題を量子アニーリングシミュレータで解く.pdf PDF

PDF

PDF

PDF

PDF

Recently uploaded

PDF

【採用ピッチ資料】ランド・ジャパンの未来の仲間たちへ_2026年改訂版資料.pdf PDF

5位_ラテン_成城大学.pdf------------------------- PDF

3位【株式会社ローソン】三万日坊主_京都芸術大学 (1).pdf-------- PDF

chouhouobuse_202601slide_obusetown_nagano.pdf PDF

5位【株式会社ローソン】げきアツこ_高崎経済大学 (1).pdf-------- PDF

【会社紹介資料】株式会社カンゲンエージェント [ 2026/01 公開 ].pdf PDF

2位_ファイヤーサンダーバード_東京理科大学.pdf-------------- PDF

4位【株式会社ローソン様_チームA.S_産業能率大学】 (1).pdf----- PDF

1位_自然組.inc_東京理科大学.pdf------------------- PDF

3位_ Micromaterials_愛知学院大学.pdf----------- PDF

1位[ローソン]オオクワ型_成城大学---------------------- PDF

4位_低燃費ぺあ_東北学院大学.pdf--------------------- PDF

1位_自然組.inc_東京理科大学.pdf------------------- PDF

令和8年度(2026年)令和8年度税制改正大綱速報ポイント解説 要点をまとめて 税理士法人ゆびすい PDF

2位【株式会社ローソン】チームわさび(社会6班)_大和大学 (1).pdf------------- PDF

EXPERTGARDEN_経営層の皆さま向け資料.pdfEXPERTGARDEN_経営層の皆さま向け資料.pdf PDF

【第7章】第3層:風(業務改革)|地方中小企業向け-CX風林火山 実践ガイド-BSC理論×スタートアップサイエンス NANDからテトリスへ_前編.pdf

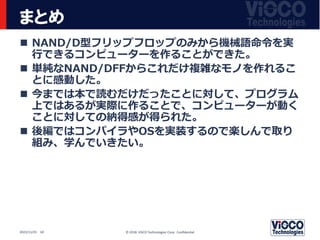

- 1.

- 2.

- 3.

© 2018 ViSCOTechnologies Corp. Confidential

2022/11/25 3

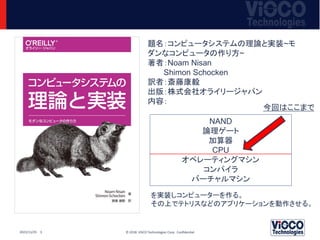

題名:コンピュータシステムの理論と実装~モ

ダンなコンピュータの作り方~

著者:Noam Nisan

Shimon Schocken

訳者:斎藤康毅

出版:株式会社オライリージャパン

内容:

NAND

論理ゲート

加算器

CPU

オペレーティングマシン

コンパイラ

バーチャルマシン

を実装しコンピューターを作る。

その上でテトリスなどのアプリケーションを動作させる。

今回はここまで

- 4.

目次

1章: ブール論理

2章: ブール算術

3章: 順序回路

4章: 機械語

5章: コンピュータアーキテクチャ

© 2018 ViSCO Technologies Corp. Confidential

2022/11/25 4

- 5.

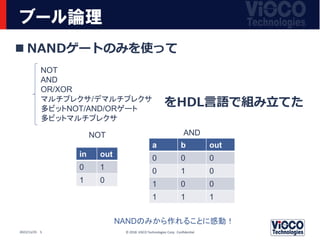

ブール論理

NANDゲートのみを使って

をHDL言語で組み立てた

© 2018ViSCO Technologies Corp. Confidential

2022/11/25 5

NOT

AND

OR/XOR

マルチプレクサ/デマルチプレクサ

多ビットNOT/AND/ORゲート

多ビットマルチプレクサ

NANDのみから作れることに感動!

a b out

0 0 0

0 1 0

1 0 0

1 1 1

AND

in out

0 1

1 0

NOT

- 6.

ブール算術

半加算器 /全加算器 / 加算器 / インクリメンタ / ALU

を今まで作った論理ゲートから構築

ALUでは16ビットの2つの入力から、それらの和、差、

論理積および論理和を計算する仕様となっている

補数表現を用いて引き算を行う理論について学ぶことが

できた。

© 2018 ViSCO Technologies Corp. Confidential

2022/11/25 6

- 7.

順序回路

D型フリップフロップが与えられた状態でレジスタ /

RAM/ カウンタを実装した。

16個のD型フリップフロップとマルチプレクサを組み合わ

せることで16ビットの記憶ができるレジスタを実装した。

レジスタを組み合わせて、64KビットRAMを実装した。

フリップフロップから記憶装置が作れることを理解した。

© 2018 ViSCO Technologies Corp. Confidential

2022/11/25 7

- 8.

- 9.

- 10.

- 11.