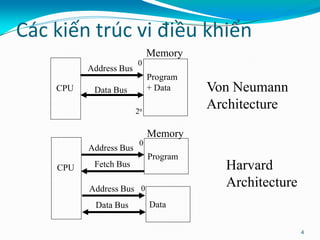

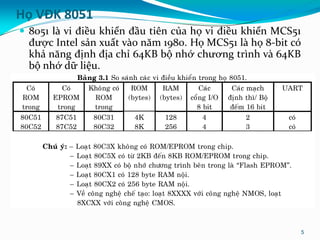

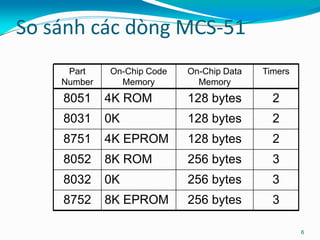

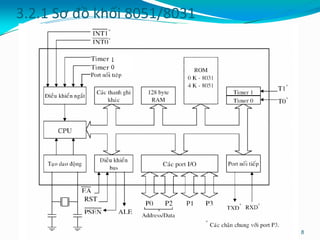

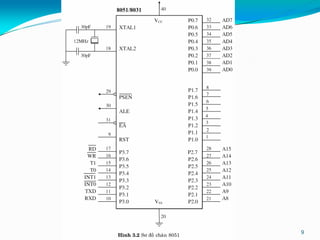

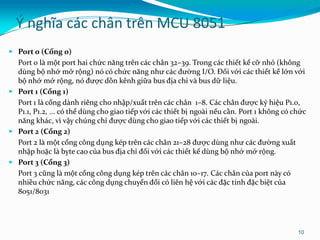

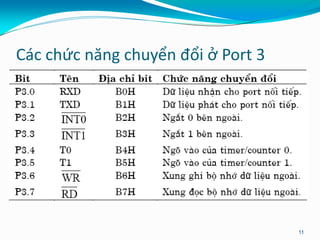

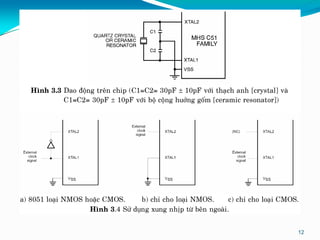

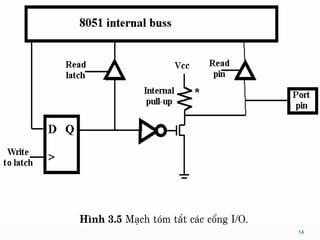

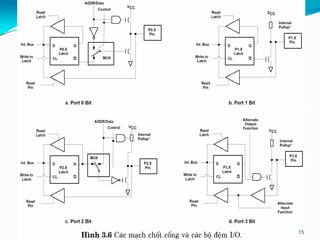

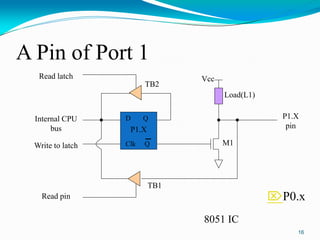

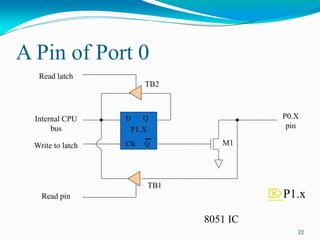

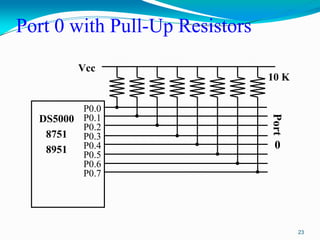

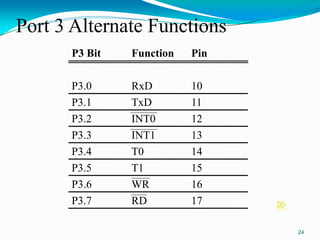

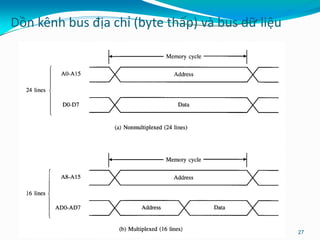

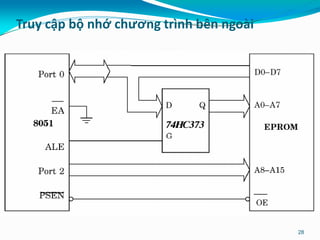

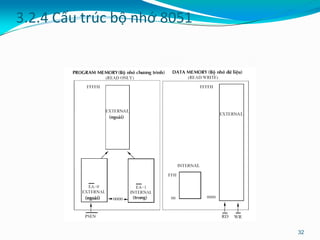

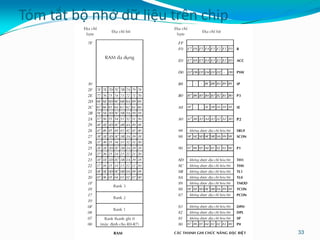

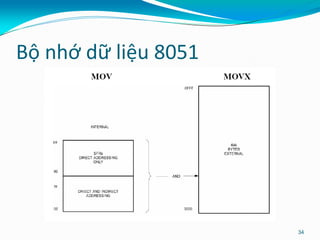

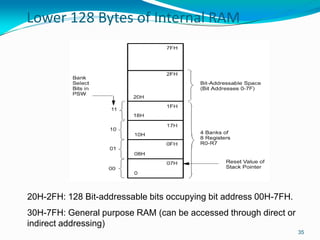

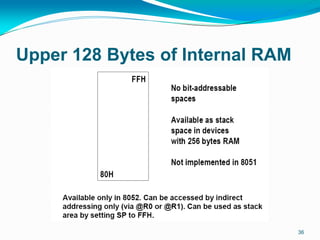

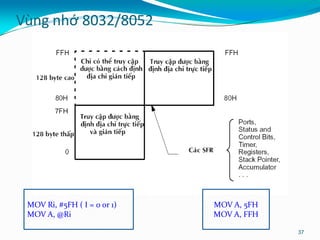

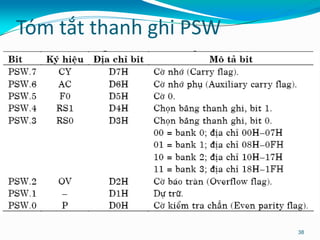

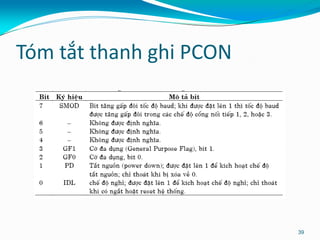

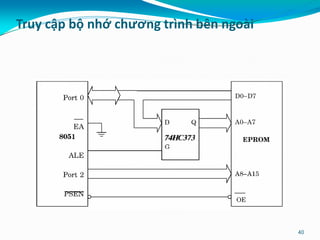

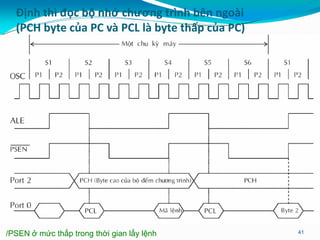

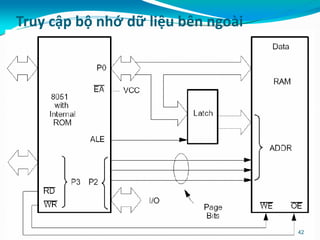

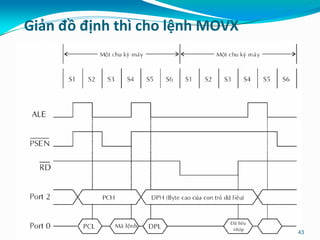

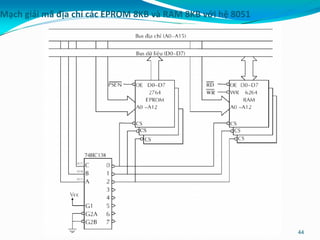

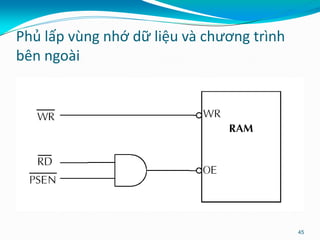

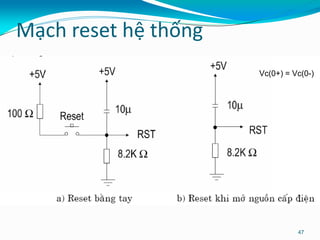

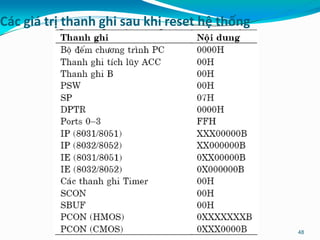

Tài liệu trình bày về họ vi điều khiển 8051, một sản phẩm của Intel sản xuất vào năm 1980, với kiến trúc 8-bit cho phép định địa chỉ bộ nhớ chương trình và dữ liệu lên tới 64KB. Nó bao gồm thông tin chi tiết về cấu trúc phần cứng, các cổng I/O và cách hoạt động của các thành phần bên trong 8051, cùng với sự khác biệt giữa các dòng vi điều khiển trong họ MCS-51. Tài liệu cũng giải thích về các phương thức truy cập bộ nhớ và quy trình reset hệ thống.