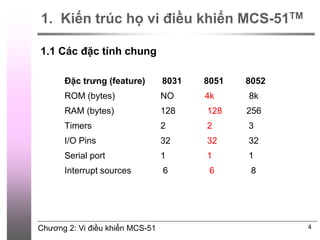

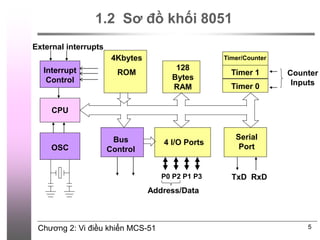

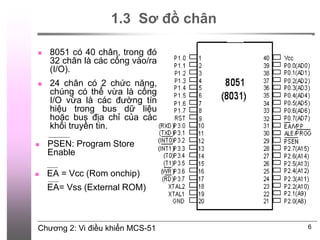

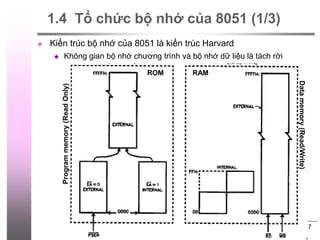

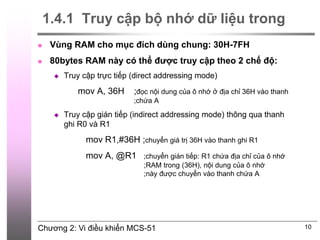

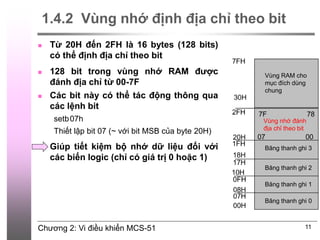

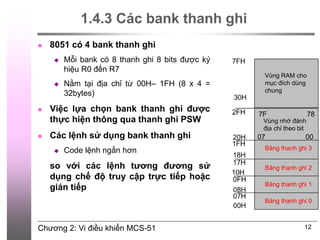

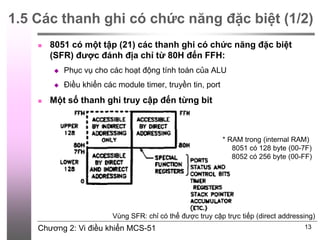

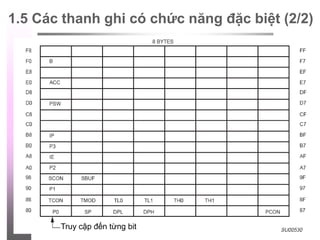

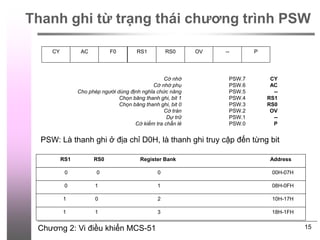

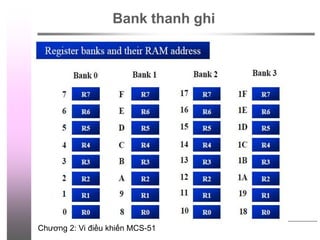

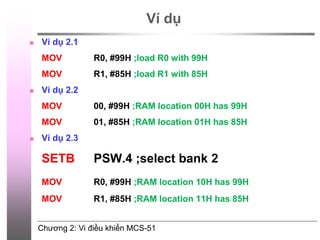

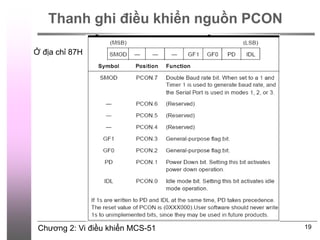

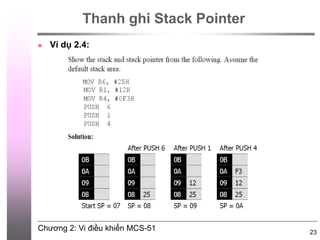

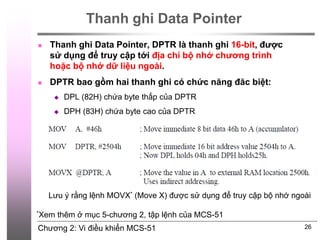

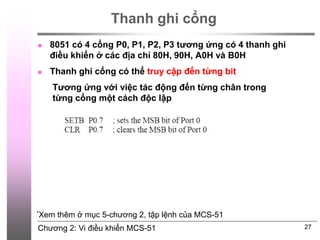

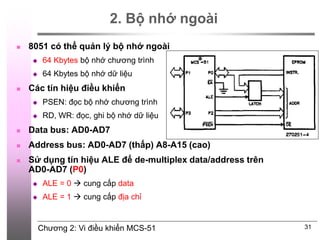

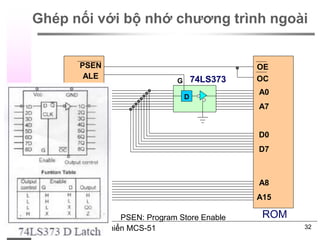

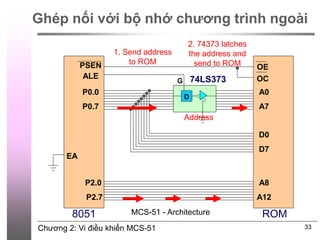

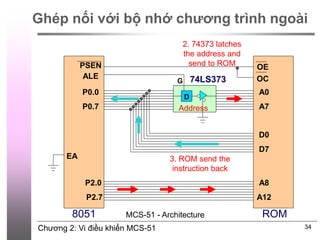

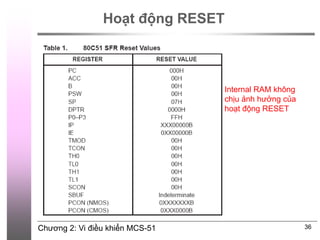

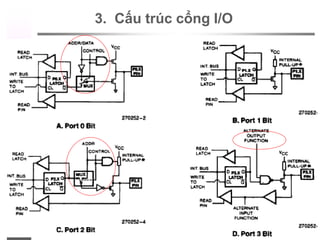

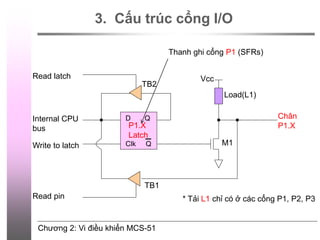

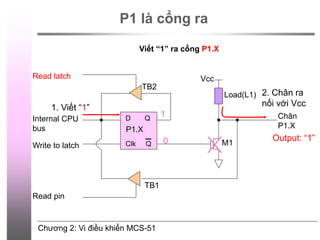

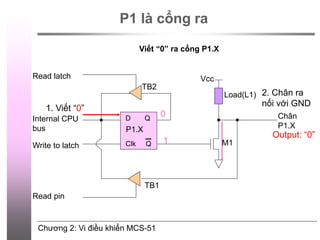

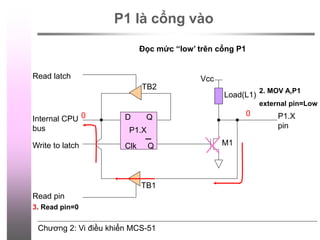

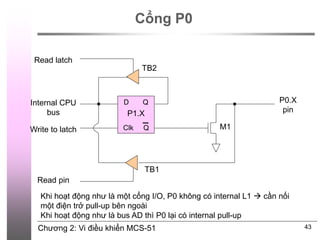

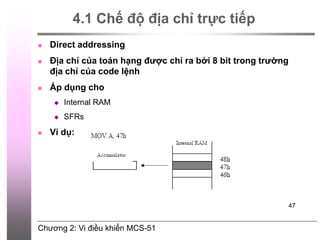

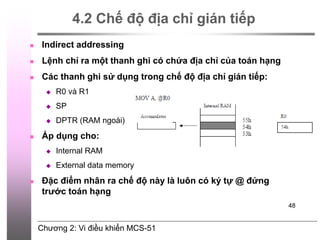

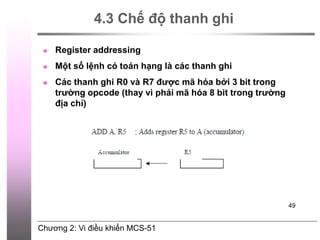

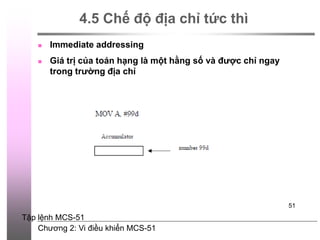

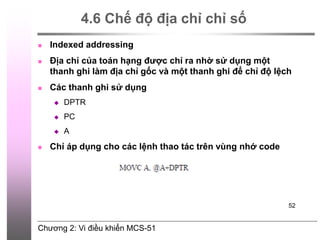

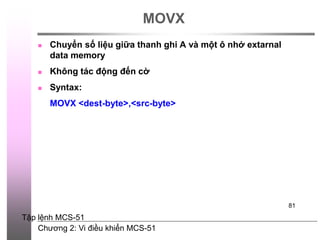

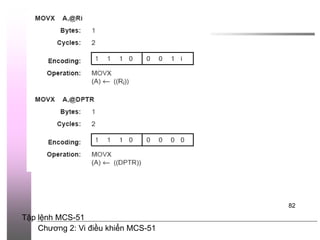

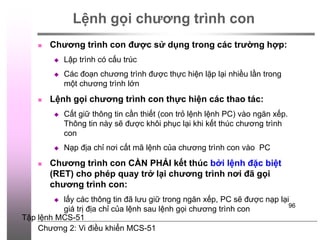

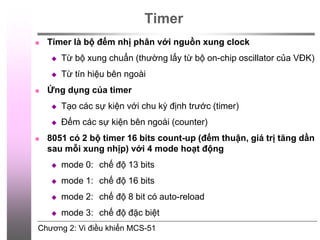

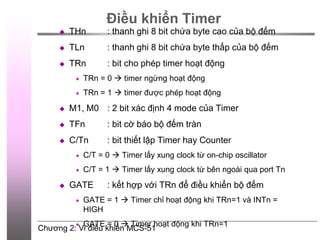

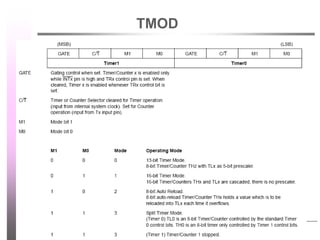

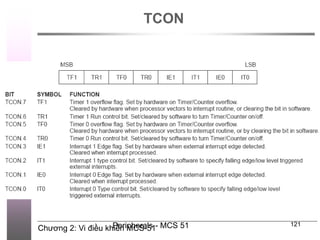

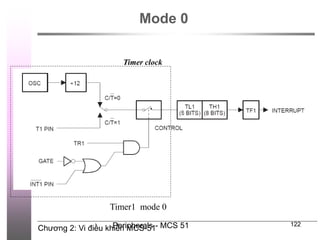

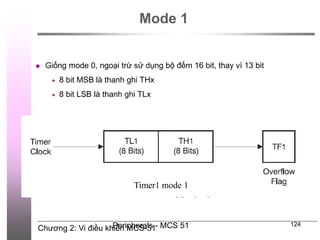

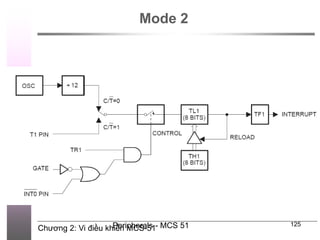

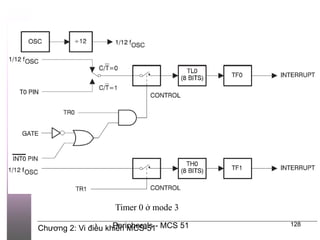

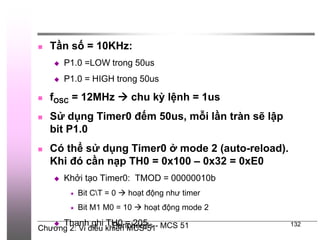

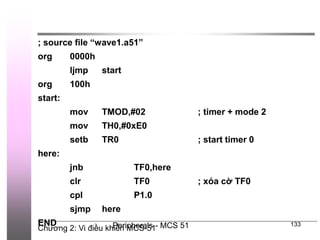

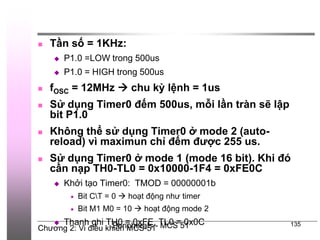

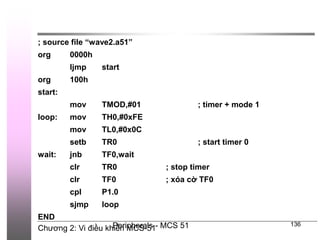

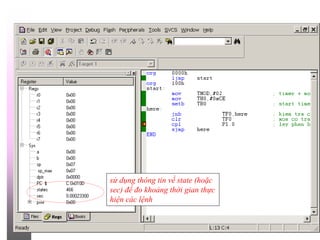

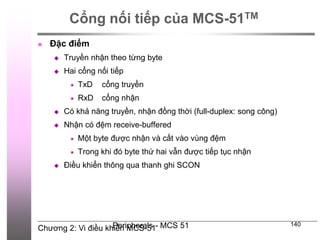

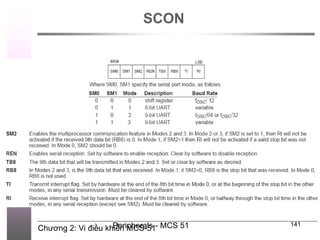

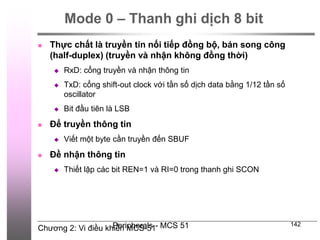

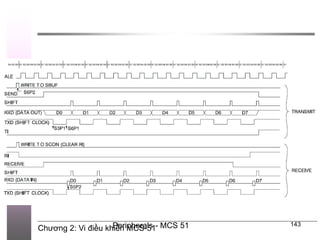

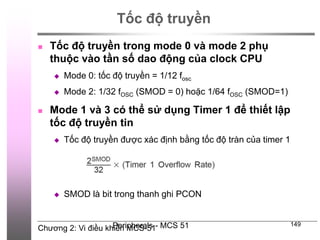

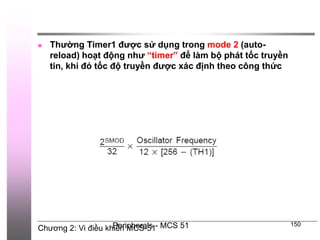

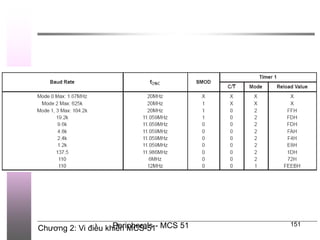

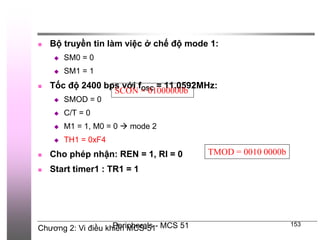

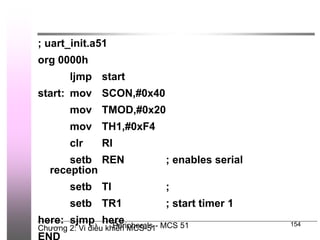

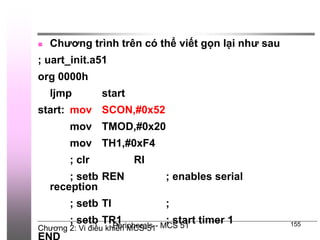

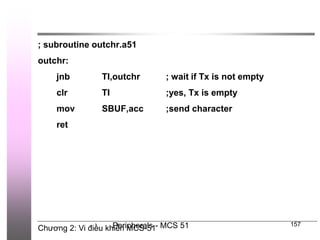

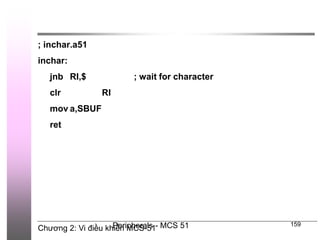

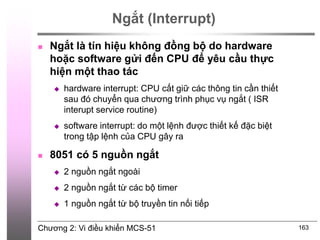

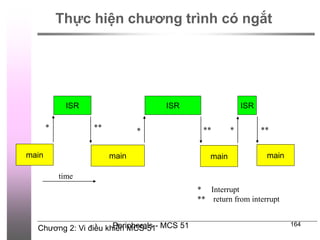

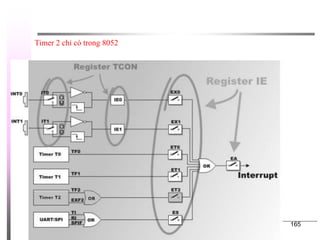

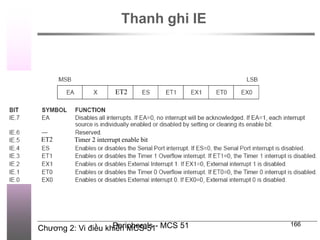

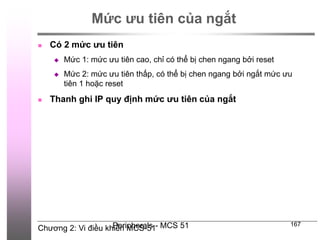

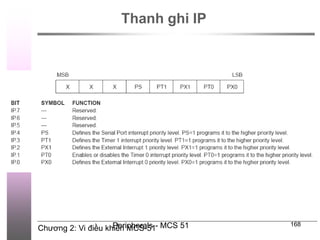

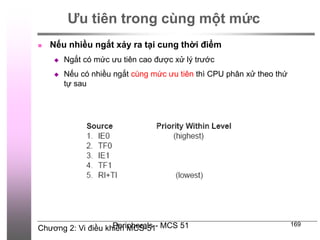

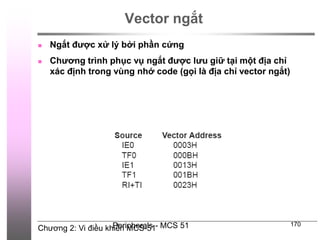

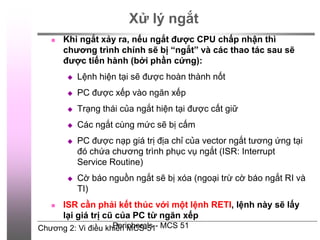

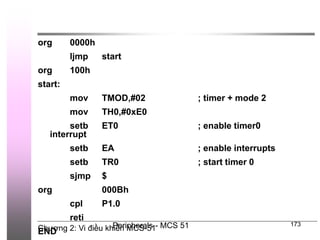

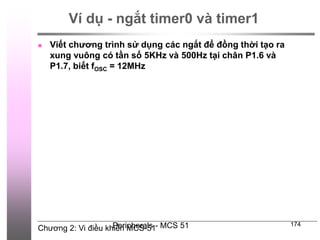

Chương 2 trình bày kiến trúc của vi điều khiển MCS-51, bao gồm các đặc điểm, sơ đồ khối và cổng vào/ra. Các thanh ghi và tổ chức bộ nhớ, cũng như các chế độ truy cập và các thành phần như timers, UART và cấu trúc ngắt cũng được mô tả. Bên cạnh đó, tài liệu cũng đề cập đến khả năng quản lý bộ nhớ ngoài và các tín hiệu điều khiển liên quan.